VerilogHDL总结总结

1. Verilog 语法的基础概念

Verilog HDL是一种硬件描述语言,其中HDL则是Hardware Description Language的缩写。因此,利用Verilog编写的程序最终

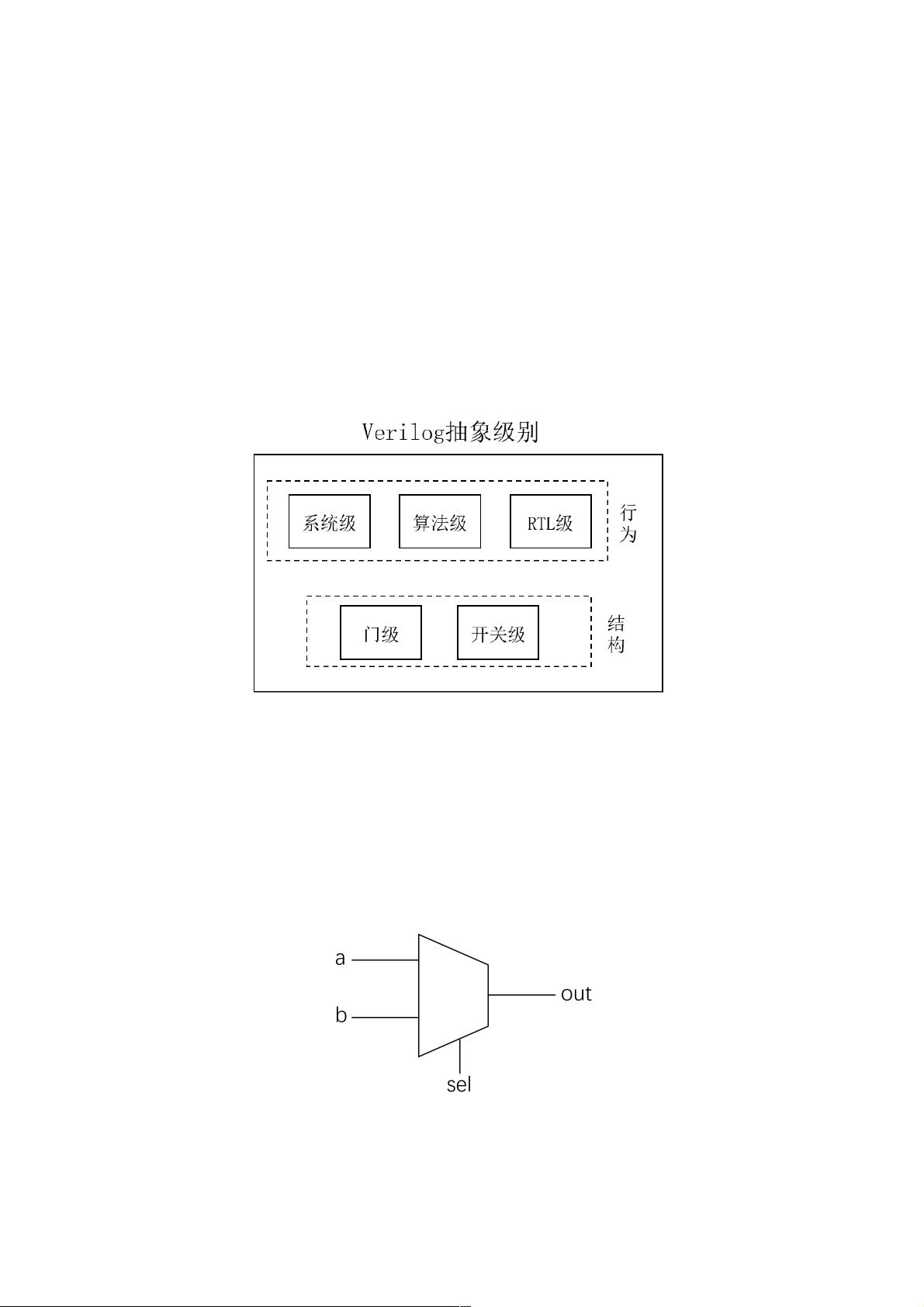

会通过工具转换为具体的电路模块。此外,利用Verilog编写的模型可以是实际电路的不同级别的抽象,通常情况下,我们将

这种抽象级别分为以下五类:

(1)系统级(system-level):用语言提供的高级结构能够实现待设计模块的外部性能的模型。

(2)算法级(algorithm-level):用语言提供的高级结构能够实现算法运行的模型。

(3)RTL级(register transfer level):描述数据在寄存器之间的流动和如何处理、控制这些数据流动的模型。

(4)门级(gate level):描述逻辑门以及逻辑门之间连接的模型。

(4)开关级(switch level):描述器件中三极管和存储结点以及它们之间连接的模型。

其中,前三种抽象级别为行为级抽象,它侧重于于描述电路的功能;门级和开关级属于结构级别抽象,侧重于模块内部结构实

现的具体描述。关系图如下:

1.1 Verilog模块的基本概念

由于Verilog是一门硬件描述语言,因此在编写程序的时候往往是通过模块的形式来进行组织,这里的模块可以看做其他编程

语言中的函数,它用于描述一个特定功能的模块。通过将多个模块联合起来最终可以形成我们的设计模型。

下面从几个简单模块的分析来形成对模块的基本认识:

例1:下面是一个二选一多路选择器的Verilog HDL程序:

其对应的电路图如下图所示:

从代码中可以看出,一个模块是一段以module-endmodule包含的代码段构成。紧跟在关键字module之后的是模块名muxtwo

以及端口列表(out, a, b, sel),这里包含了四个端口,依次为输出端口out、信号端口a、信号端口b以及选择端口sel。

在模块内部,第2、3行是I/O说明,说明了端口列表中端口的输入输出方向以及端口的位数;第4行是内部信号声明,通常包括

reg和wire两种;最后的always块是模块的功能定义,描述的是模块的核心功能。

值得注意的是,上例中的always语句实际上已经属于行为级抽象了,它只关心逻辑功能而不关心其电路结构。下面两个程序

是对上面例子中的二选一多路选择器的门级描述方式: