Verilog HDL设计多周期处理器控制器详解与仿真

版权申诉

本实验是关于计算机组成与结构中的控制器设计与仿真的一个重要部分,目标是让学生深入理解和掌握CPU控制器的基本电路构造及其设计原理,通过实际操作学习Verilog HDL语言进行电路建模和仿真。实验的核心内容是设计一个多周期处理机控制器,其指令系统包括基本的算术逻辑运算(如AND, OR, ADD, SUB等)以及数据加载/存储操作,以及条件分支指令。整个设计需要遵循五个时钟周期来执行指令:取指令、指令译码、ALU操作或地址计算、数据访问或指令完成、最后是结果写回。

实验的关键组成部分包括:

1. **指令集**:实验涉及13种指令,包括读取寄存器(rd)、算术逻辑运算(如andrd, addird等)和内存操作(loadrd, storerd)。还有条件转移指令如branchdisp,要求支持程序的分支控制。

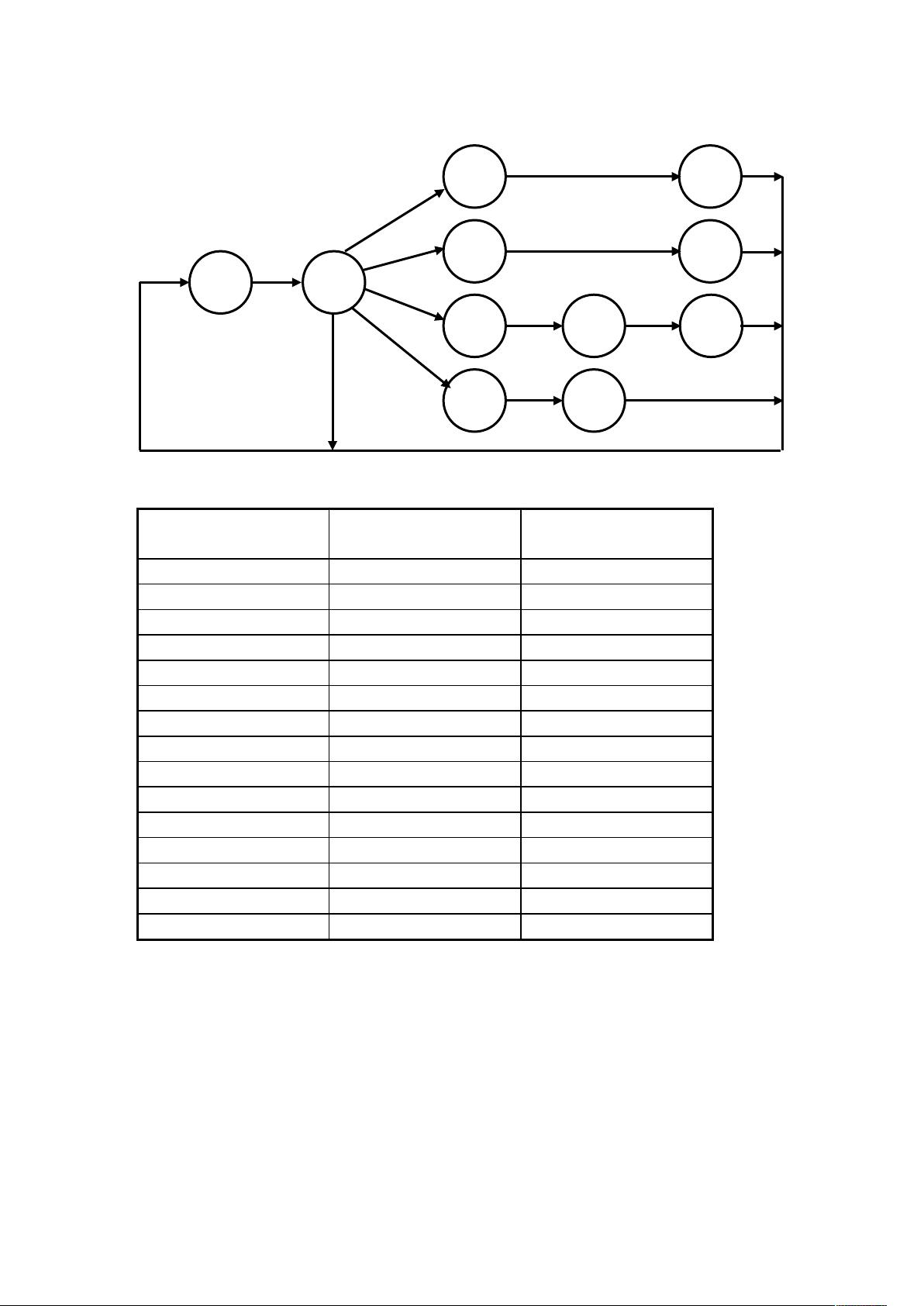

2. **数据路径**:多周期处理机的数据流路径图显示了数据在处理器内部的流动,包括从内存到ALU的路径,以及ALU输出到寄存器堆和存储器的写回路径。这涉及到控制信号如WRITEPC、SELLDST、WRITEMEM、WRITEIR等,它们决定了数据何时被写入或读出。

3. **控制信号**:如SELLOAD用于选择数据来源(ALU输出或存储器),SELST在store指令执行时从寄存器堆中读取rd值,WRITEREG控制寄存器堆的写操作。

4. **Verilog HDL**:学生需要运用Verilog语言进行控制器的设计,这涉及到行为级(模仿处理器的行为)和结构级(描述硬件组件)的模型构建。仿真测试是验证设计正确性和性能的重要环节。

通过这个实验,学生不仅可以提升硬件描述语言的技能,还能理解计算机系统如何按照指令集进行操作,以及控制器在控制数据流动和指令执行中的关键作用。此外,实践经验将有助于培养逻辑设计和问题解决能力,为后续的计算机体系结构和嵌入式系统学习打下坚实基础。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-07-04 上传

2021-07-04 上传

2021-10-12 上传

2023-07-07 上传

2021-01-23 上传

2022-10-24 上传

hinon_

- 粉丝: 0

- 资源: 8

最新资源

- 全国江河水系图层shp文件包下载

- 点云二值化测试数据集的详细解读

- JDiskCat:跨平台开源磁盘目录工具

- 加密FS模块:实现动态文件加密的Node.js包

- 宠物小精灵记忆配对游戏:强化你的命名记忆

- React入门教程:创建React应用与脚本使用指南

- Linux和Unix文件标记解决方案:贝岭的matlab代码

- Unity射击游戏UI套件:支持C#与多种屏幕布局

- MapboxGL Draw自定义模式:高效切割多边形方法

- C语言课程设计:计算机程序编辑语言的应用与优势

- 吴恩达课程手写实现Python优化器和网络模型

- PFT_2019项目:ft_printf测试器的新版测试规范

- MySQL数据库备份Shell脚本使用指南

- Ohbug扩展实现屏幕录像功能

- Ember CLI 插件:ember-cli-i18n-lazy-lookup 实现高效国际化

- Wireshark网络调试工具:中文支持的网口发包与分析