FPGA中SDRAM相位角计算详解

"本文详细介绍了在FPGA设计中如何进行SDRAM相位角计算,以确保数据正确传输。作者使用了EP3C55F484I7 FPGA芯片和MT48LC16M16A2 SDRAM芯片,并通过获取SDRAM和FPGA的相关参数,计算出合适的读写滞后和超前时间,最后设置了PLL参数进行编译和下载。"

SDRAM相位角计算是FPGA设计中的关键步骤,特别是在高速数据传输的应用中。这一过程涉及到对FPGA和SDRAM之间时序匹配的精确计算,以确保数据在正确的时间被采样和驱动。

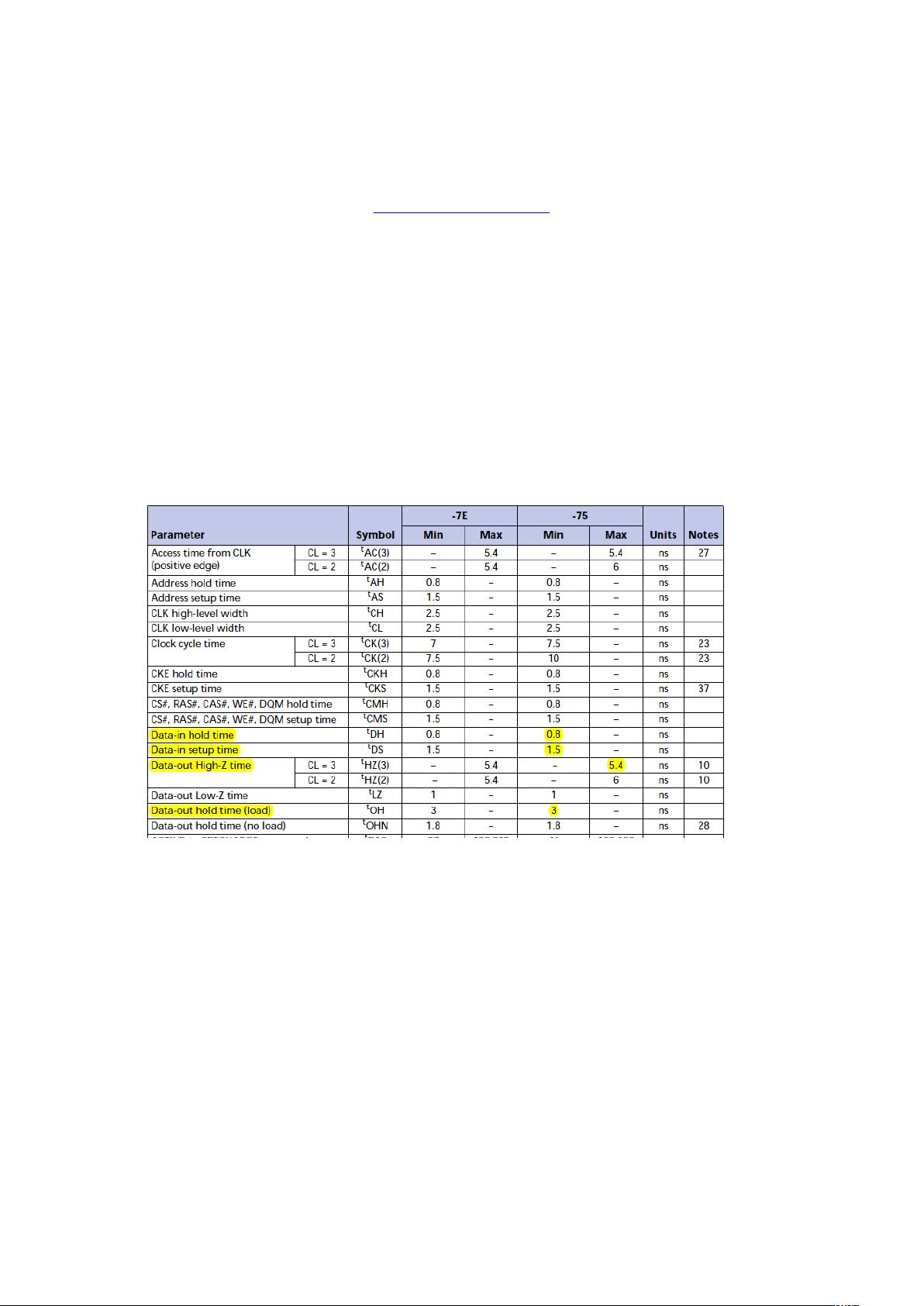

首先,需要了解SDRAM的参数。MT48LC16M16A2是一款常见的SDRAM芯片,其主要时序参数包括输入数据建立时间(TDS)、输入采样保持时间(TDH)、输出高阻时间(THZ)和输出保持时间(TOH)。这些参数在数据手册中可以找到,它们决定了SDRAM的操作边界条件。

接着,FPGA的时序参数设置也至关重要。在Altera的EP3C55F484I7 FPGA中,需要设置时间分析器并获取关键参数,如最大传播延迟时间(TCOMAX)、最大建立时间(Tsumax)、最大保持时间(THmax)和最小传播延迟时间(TCOMIN)。这些参数可以通过FPGA的编译报告获取。

接下来,根据这些参数,我们可以计算出读写滞后和超前时间。读滞后(Toh-Thmax)和写滞后(Tclk-tcomax)确保在时钟边缘之后数据稳定,而读超前(Tcomin-Tdh)和写超前(Tclk-Thz-Tsumax)则确保数据在时钟边缘之前到达。在本例中,作者给出了具体计算示例。

最终,这些计算结果用于设置PLL(锁相环)的相位偏移,以使FPGA的时钟与SDRAM的数据传输相匹配。在设置PLL参数时,将计算出的相位差值转换为适合PLL的值,即-4.1575,然后在PLL配置中应用。

完成上述步骤后,对设计进行编译,并将固件下载到FPGA中,以验证设置是否正确。如果遇到问题或有进一步的疑问,可以通过作者提供的邮箱联系,进行交流和讨论。

SDRAM相位角计算是一个涉及精确时序分析和调整的过程,对于保证FPGA与SDRAM之间的可靠通信至关重要。通过理解SDRAM和FPGA的时序特性,以及熟练运用相关的计算方法,可以有效地优化系统性能。

2022-09-21 上传

点击了解资源详情

点击了解资源详情

2018-07-14 上传

2022-09-23 上传

2022-09-19 上传

qx7873087

- 粉丝: 5

- 资源: 4

最新资源

- Java集合ArrayList实现字符串管理及效果展示

- 实现2D3D相机拾取射线的关键技术

- LiveLy-公寓管理门户:创新体验与技术实现

- 易语言打造的快捷禁止程序运行小工具

- Microgateway核心:实现配置和插件的主端口转发

- 掌握Java基本操作:增删查改入门代码详解

- Apache Tomcat 7.0.109 Windows版下载指南

- Qt实现文件系统浏览器界面设计与功能开发

- ReactJS新手实验:搭建与运行教程

- 探索生成艺术:几个月创意Processing实验

- Django框架下Cisco IOx平台实战开发案例源码解析

- 在Linux环境下配置Java版VTK开发环境

- 29街网上城市公司网站系统v1.0:企业建站全面解决方案

- WordPress CMB2插件的Suggest字段类型使用教程

- TCP协议实现的Java桌面聊天客户端应用

- ANR-WatchDog: 检测Android应用无响应并报告异常