FPGA在EDA/PLD中实现LVDS接口的应用解析

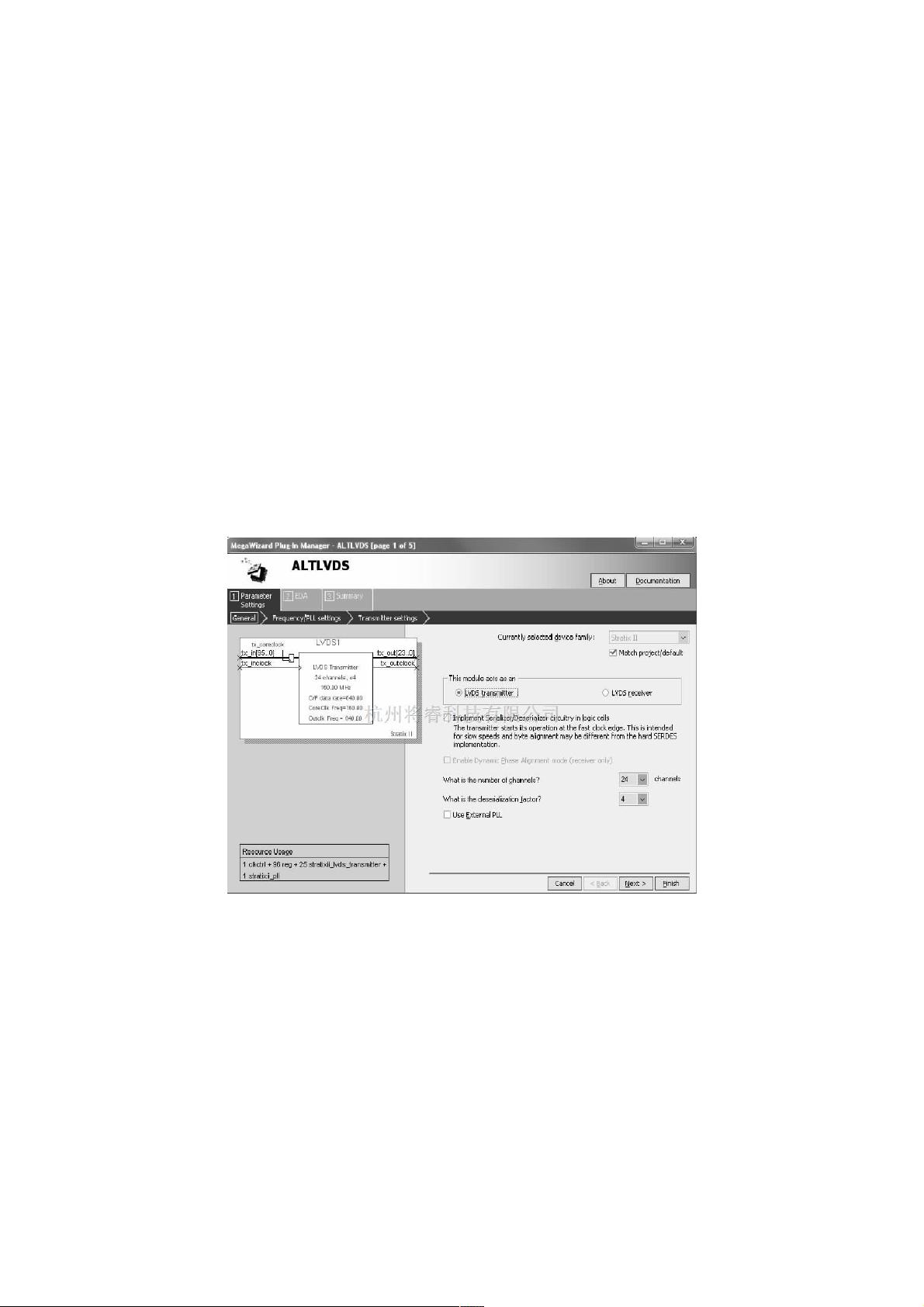

"EDA/PLD中的基于FPGA的LVDS接口应用主要涉及LVDS技术原理、高速数据传输系统的应用以及FPGA实现的LVDS_TX模块在DAC系统中的具体应用。" LVDS(Low-Voltage Differential Signaling)技术是1994年由美国国家半导体公司开发的一种高效低功耗的信号传输模式,它能在保持高数据传输率的同时降低系统能耗。LVDS的核心是利用一对差分线路来传输信号,一条线携带正信号,另一条线则携带与之相反的电平。在接收端,这两个信号被相减,从而有效地消除共模噪声。这种设计使得LVDS具有低电磁辐射和低串扰的优势,特别适合在高速、长距离、高信号完整性的应用环境中使用。 在LVDS接口中,信号的传输速率可以达到几百Mbit/s到2Gbit/s,这使其成为高速数据传输的理想选择。LVDS接口的标准有两个,分别是TIA/EIA的ANSI/TIA/EIA-644标准和IEEE1596.3标准,这些标准确保了不同设备间的兼容性和互操作性。 在EDA(电子设计自动化)和PLD(可编程逻辑器件)领域,FPGA(Field-Programmable Gate Array)因其灵活性和高性能而常被用于实现LVDS接口。在描述的案例中,使用了Altera的Stratix II系列EP2S90 FPGA实现了一个LVDS_TX发送模块。这个模块能够以640Mbit·s-1的数据速率将数据发送到DAC(Digital-to-Analog Converter)电路,展示了LVDS在高速数据转换系统中的实际应用。 基于FPGA的LVDS发送模块设计通常包括以下几个关键部分: 1. 数据输入接口:接收并处理来自系统其他部分的数据,通常包括时钟同步和数据编码等步骤。 2. LVDS编码器:将单端信号转换为差分信号,以满足LVDS接口的要求。 3. 信号驱动器:提供足够的电流驱动差分线路,确保信号的稳定传输。 4. 电源管理:确保低电压运作,降低功耗。 5. 控制逻辑:管理和调整传输参数,如数据速率、时序等。 LVDS接口在DAC系统中的应用,能够提高数据转换的精度和速度,同时减少噪声对信号质量的影响。这种应用实例进一步证明了LVDS接口在高速数据通信系统中的优越性,尤其是在需要高带宽和低噪声的场合,如视频传输、通信网络和高速测试设备等。 LVDS技术结合FPGA的使用,为高速数据传输提供了高效且可靠的解决方案,而基于FPGA的LVDS_TX模块设计则成为了实现这一目标的关键。通过深入理解和应用这些技术,工程师可以设计出满足各种复杂需求的高速数据通信系统。

下载后可阅读完整内容,剩余6页未读,立即下载

- 粉丝: 187

- 资源: 955

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 十种常见电感线圈电感量计算公式详解

- 军用车辆:CAN总线的集成与优势

- CAN总线在汽车智能换档系统中的作用与实现

- CAN总线数据超载问题及解决策略

- 汽车车身系统CAN总线设计与应用

- SAP企业需求深度剖析:财务会计与供应链的关键流程与改进策略

- CAN总线在发动机电控系统中的通信设计实践

- Spring与iBATIS整合:快速开发与比较分析

- CAN总线驱动的整车管理系统硬件设计详解

- CAN总线通讯智能节点设计与实现

- DSP实现电动汽车CAN总线通讯技术

- CAN协议网关设计:自动位速率检测与互连

- Xcode免证书调试iPad程序开发指南

- 分布式数据库查询优化算法探讨

- Win7安装VC++6.0完全指南:解决兼容性与Office冲突

- MFC实现学生信息管理系统:登录与数据库操作

信息提交成功

信息提交成功