AMD Vitis HLS 使用优化:命令、技巧与最佳实践

需积分: 5 12 浏览量

更新于2024-06-19

收藏 16.12MB PDF 举报

"AMD Vitis HLS工具使用和优化指南"

AMD的Vitis HLS(硬件层面上升)工具是针对FPGA开发的重要平台,尤其适合利用C++进行高层次综合,将高级语言代码转换为可运行在FPGA上的RTL(寄存器传输级)代码。本指南深入探讨了如何最大化利用这一工具,提升设计效率和性能。

首先,高层次综合的优势在于它允许开发者使用更接近高级编程语言的C/C++来描述设计,简化了FPGA开发流程。Vivado HLS作为AMD的集成开发环境,提供了一整套工具来支持这个过程,包括代码分析、优化和验证。

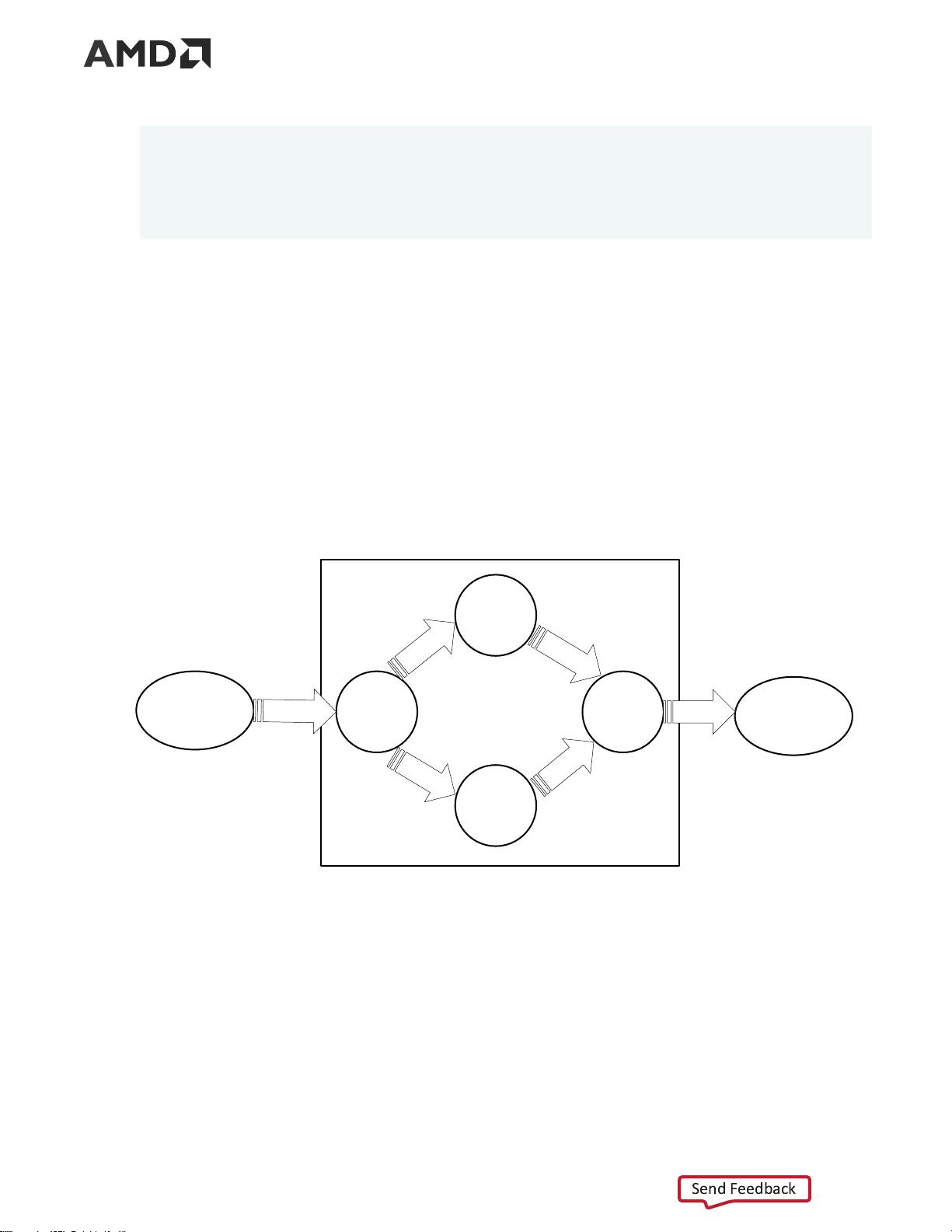

设计代码重构是HLS中的关键步骤,因为它直接影响最终硬件的性能和面积效率。开发者需要了解如何有效地重构代码以利用并行性,例如通过控制驱动的任务和数据驱动的任务来实现任务级并行度。此外,理解循环优化是至关重要的,包括循环流水线、循环展开、循环合并以及对嵌套循环和循环边界的处理,这些都是提高性能的关键技术。

在处理数组时,Vitis HLS提供了多种方法将软件中的数组映射到硬件存储器,优化访问速度和存储效率。开发者需要掌握如何处理数组访问模式、初始化和复位,以及如何实现ROM。同时,理解和应用不同的函数特性,如内联、流水线和例化,可以进一步优化功能执行。

数据类型的选择也对性能有显著影响。标准类型、复合数据类型、AP数据类型(任意精度)、全局变量、指针、矢量数据类型和位宽传输等都是开发者在设计中需要考虑的因素。值得注意的是,Vitis HLS并不支持所有C/C++特性,例如系统调用、动态内存分配、特定指针操作、递归函数和未定义行为,因此开发者需要避免在HLS代码中使用这些不受支持的构造。

该文档还包含了教程和示例,帮助开发者实际操作并理解上述概念。通过遵循最佳实践检查表,开发者能够创建符合AXI4接口规范的IP,并优化其在FPGA上的实现。

总而言之,这份指南为FPGA开发者提供了全面的指导,涵盖了从基本概念到高级优化技巧的所有方面,旨在帮助他们更高效地利用Vitis HLS工具进行FPGA设计,实现高性能、低功耗和高灵活性的硬件解决方案。

421 浏览量

点击了解资源详情

点击了解资源详情

1576 浏览量

284 浏览量

621 浏览量

651 浏览量

296 浏览量

2565 浏览量

红楼愚梦

- 粉丝: 38

- 资源: 2

最新资源

- Community Server专题.pdf

- Vim用户手册,VIM入门好书。

- 华为公司(南京上海)笔试题大全

- 使用.NET和Vss进行团队开发

- Developing J2EE Applications with the UML and Rational Rose

- C#深入浅出全接触和一些基本的介绍

- 单运算放大器,中文版。介绍运放的常用电路。

- 电脑硬盘维修资料(word格式)

- 无线电遥控器的工作原理及红外线原理

- Effcient C++ Programming Techniques

- 轻松搞定 sql server 2000 程序设计.pdf

- Java 多线程编程详解

- MyEclipse 6 Java EE 开发中文手册

- 子网掩码划分 计算机等级考试四级网络工程师

- Keil 与proteus 连接调试

- Ajax for Dummies.pdf