1.8V低功耗CMOS带隙基准电压源设计:高精度与低PSRR特性

需积分: 5 155 浏览量

更新于2024-08-12

收藏 219KB PDF 举报

本文档主要探讨了1.8V高电源抑制比的CMOS带隙基准电压源的设计与实现,针对传统电压源设计中速度、噪声和工作温度范围的挑战,提出了一种创新的设计方案。作者方穗明、王占仓和高风在2007年10月发表于《北京工业大学学报》上,他们基于TSMC工艺进行了电路模拟仿真。

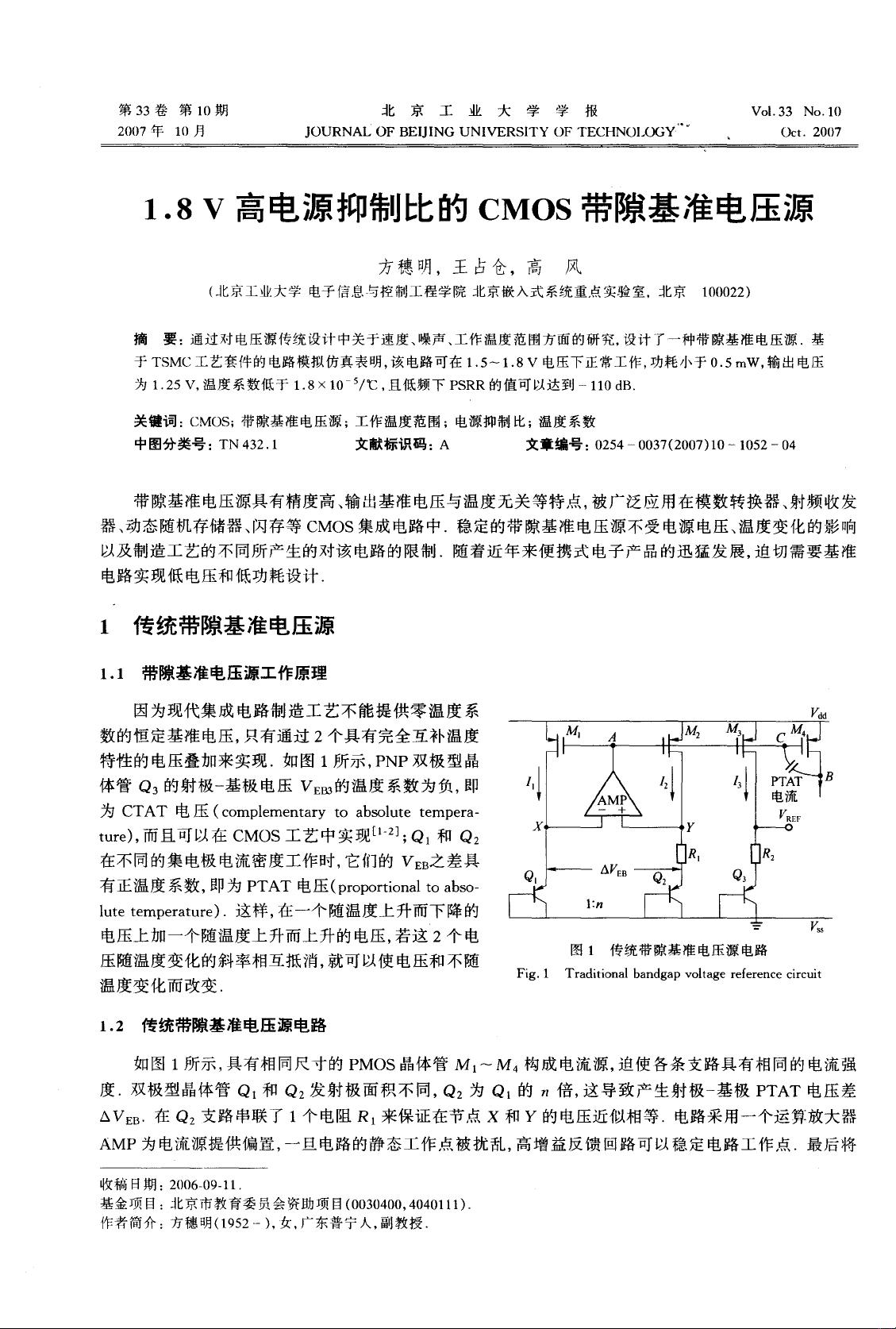

带隙基准电压源是一种关键的电路元件,因其具有高精度和温度独立的特性,广泛应用于模数转换器(ADC)、射频收发器、动态随机访问存储器(DRAM)和闪存等CMOS集成电路中。由于现代集成电路制造技术无法提供零温度系数的恒定基准电压,带隙电路利用PNP晶体管的CTAT电压(负温度系数)和NMOS或PMOS晶体管的PTAT电压(正温度系数)进行补偿,确保输出电压不受电源电压波动和温度变化的影响。

传统带隙基准电压源的基本构造如图1所示,通过调整两个互补工作的晶体管的电流和电压,使得它们的温度效应相互抵消,形成稳定的基准电压。然而,这种设计在追求速度、噪声抑制和温度稳定性之间可能存在权衡。作者的设计旨在改进这一特性,尤其是在低电源电压(1.5~1.8V)下仍能保持高效能和低功耗。

据电路模拟结果,这个新型带隙基准电压源能够在1.5~1.8V电压下稳定工作,功耗控制在0.5mW以下,输出电压为1.25V,显示出出色的能源效率。此外,其温度系数非常低,仅为1.8x10^-5/℃,这意味着在温度变化时,电压变化极小,有利于保证电路的长期稳定性能。在低频情况下,电源抑制比(PSRR)达到了惊人的-110分贝,这表明对电源噪声的抑制能力非常强。

这篇论文的关键知识点包括带隙基准电压源的工作原理、设计挑战、以及作者所提出的解决方案的具体性能指标,如工作电压范围、功耗、温度系数和电源抑制比。这些技术进步对于降低便携式电子产品中的电源需求和优化电路稳定性具有重要意义。

616 浏览量

136 浏览量

218 浏览量

980 浏览量

150 浏览量

2021-07-21 上传

152 浏览量

803 浏览量

2021-06-14 上传

weixin_38745003

- 粉丝: 10

- 资源: 947