DDR2/3高速内存布线与信号完整性设计要点

需积分: 9 102 浏览量

更新于2024-07-25

收藏 621KB PDF 举报

本文档深入探讨了DDR2-800兆比特/秒及DDR3内存的信号完整性(SI)和电源完整性(PI)在PCB(印刷电路板)设计中的关键因素,重点关注低层数PCB,通常采用4-6层的传统技术。随着DDR2的广泛应用,特别是在追求高速度如800兆比特/秒和1066兆比特/秒时,以及DDR3对1600兆比特/秒数据速率的追求,设计挑战愈发显著。

首先,信号完整性(SI)是设计中的核心考虑,因为延迟匹配是满足内存时序要求的关键。这涉及到多方面的因素,包括PCB的层数配置、阻抗控制、互连拓扑设计、延迟匹配策略、电磁干扰(EMI)或称交叉 talk,以及电源完整性管理。较低的层数可能导致信号传播路径变长,增加信号衰减和反射的可能性,因此合理选择层数和布线布局至关重要。

PCB的层堆叠影响信号路径长度和信号完整性。每多一层,信号路径可能增加,从而增加延迟,这对高速信号来说是不利的。为了优化,工程师会采用不同的层分配策略,比如将高速信号层放在靠近信号源和负载的位置,同时保持良好的信号回路完整性。

阻抗控制是为了确保信号在传输过程中保持恒定的电压幅度,防止反射和失真。这意味着在布线过程中需要精确计算和调整线宽与间距,以匹配内存设备的工作频率。此外,信号走线的宽度和长度需要与阻抗控制相结合,以实现最佳的信号质量。

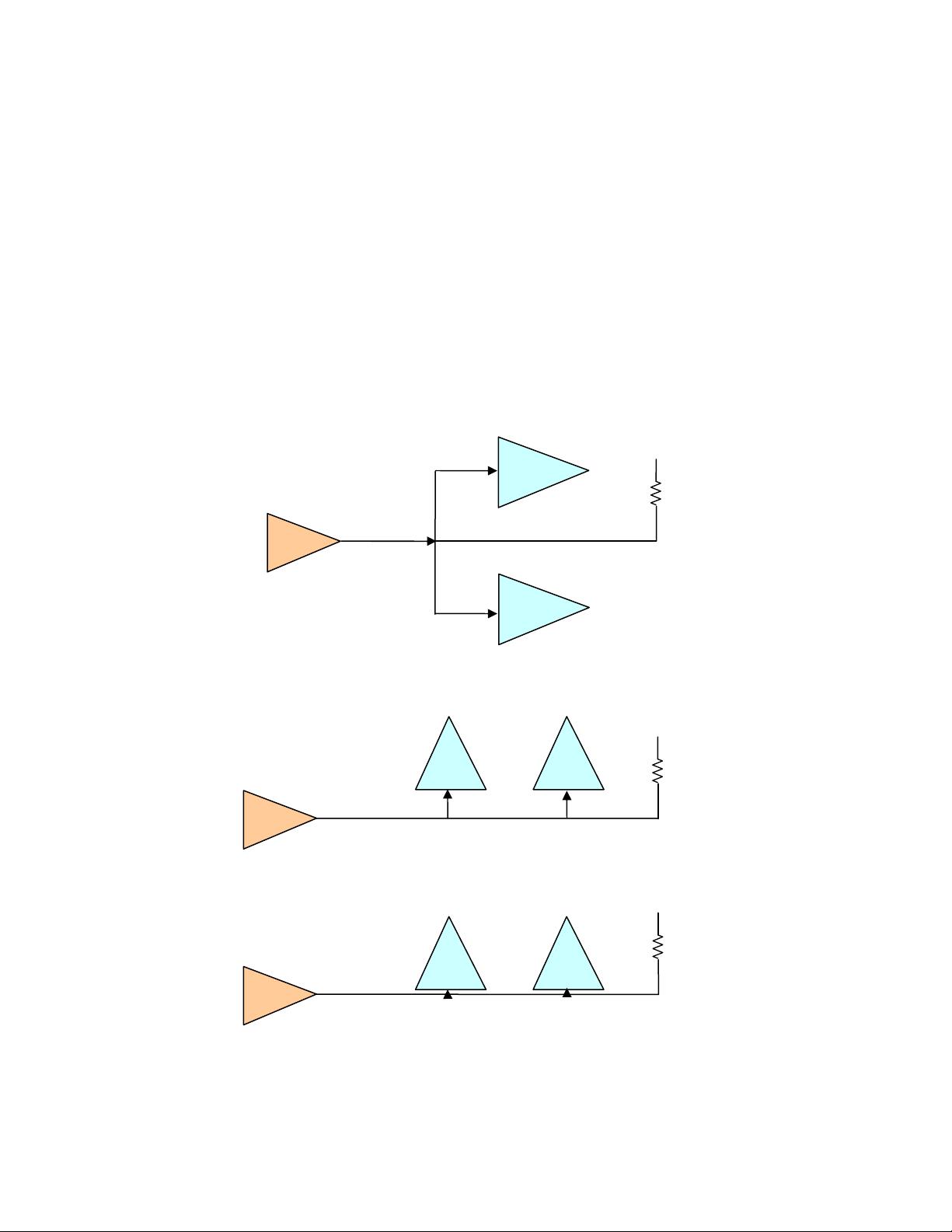

互连拓扑设计是另一个关键环节,包括信号线的走向和连接方式。平面布线、星型连接、多分支网络等不同结构都有其优缺点,设计师需要根据具体应用选择最合适的方案来最小化串扰和噪声的影响。

延迟匹配涉及精确调整各个信号路径的延迟,以确保在接收端正确的时间窗口内接收到数据。这可能通过精心设计的走线长度、使用合适的过孔或走线层以及考虑寄生参数来实现。

电源完整性管理对于DDR2和DDR3的高速运行同样重要。它包括有效的电源分配网络(PDN)设计,以确保内存模块的供电稳定且无纹波,同时避免电源噪声引入的干扰。这可能需要使用电源隔离、去耦电容和布局优化等策略。

DDR布局布线是一门细致入微的技术,涉及多个相互关联的设计要素。理解和掌握这些原理,并结合实际设计工具如Cadence AL,可以帮助工程师创建出满足高性能内存系统需求的高效、稳定的PCB设计。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2012-05-14 上传

2014-11-25 上传

2013-10-28 上传

2010-07-29 上传

2012-12-20 上传

zm96321

- 粉丝: 0

- 资源: 2

最新资源

- 3088㎡三层框架图书馆钢筋及广联达算量(含CAD图纸).rar

- Adafruit_PlatformDetect-3.45.2-py3-none-any.whl.zip

- spray-dots:我们探索随着点而移动的绘画事物

- MATLAB数据字典生成代码-dsc-0-03-03-introducing-python-libraries-nyc-career-ds-0

- EliteParkingXamarin:使用 Xamarin 和 AngularJS 开发 EliteParking 混合移动应用程序

- 智能家居控制app ui .sketch素材下载

- 3091.17平米住宅楼施组及施工图预算(工程量计算、施组、平面图、进度表).rar

- 小程序源码 samsung 蓝牙4.0开发工具包和BLE例子.rar

- Adafruit_BNO055-1.0.1-py2-none-any.whl.zip

- kaiti_GB2312.zip

- 房建工程施工组织设计-某办公楼室内外装饰施工组织设计方案

- MATLAB数据字典生成代码-dsc-0-03-03-introducing-python-libraries-online-ds-pt-03

- Musichspeler:基于网络的音频播放器-开源

- sinx的matlab代码-matlab-engineering-codes:这将是关于在matlab上解决工程问题

- 海洋环保公益组织企业网站html静态模板.zip

- 3116.88平方,六层框架办公楼(计算书、建筑、结构施工图).rar