SAP-1 8位CPU电路设计与16*8 ROM仿真解析

"精简8位CPU电路设计,包括8位CPU电路、SAP-1CPU的组成架构、指令系统、寻址方式、16*8 ROM设计与仿真、以及计算机体系结构的基础知识"

在深入讨论8位CPU电路设计之前,先来理解一下计算机的基本结构。程序存储型计算机体系结构是由冯·诺依曼提出的,这一结构定义了计算机的主要组成部分:控制器、运算器、存储器、输入设备和输出设备。这种结构中,程序和数据都存储在内存中,由程序计数器(PC)指向当前要执行的指令地址。

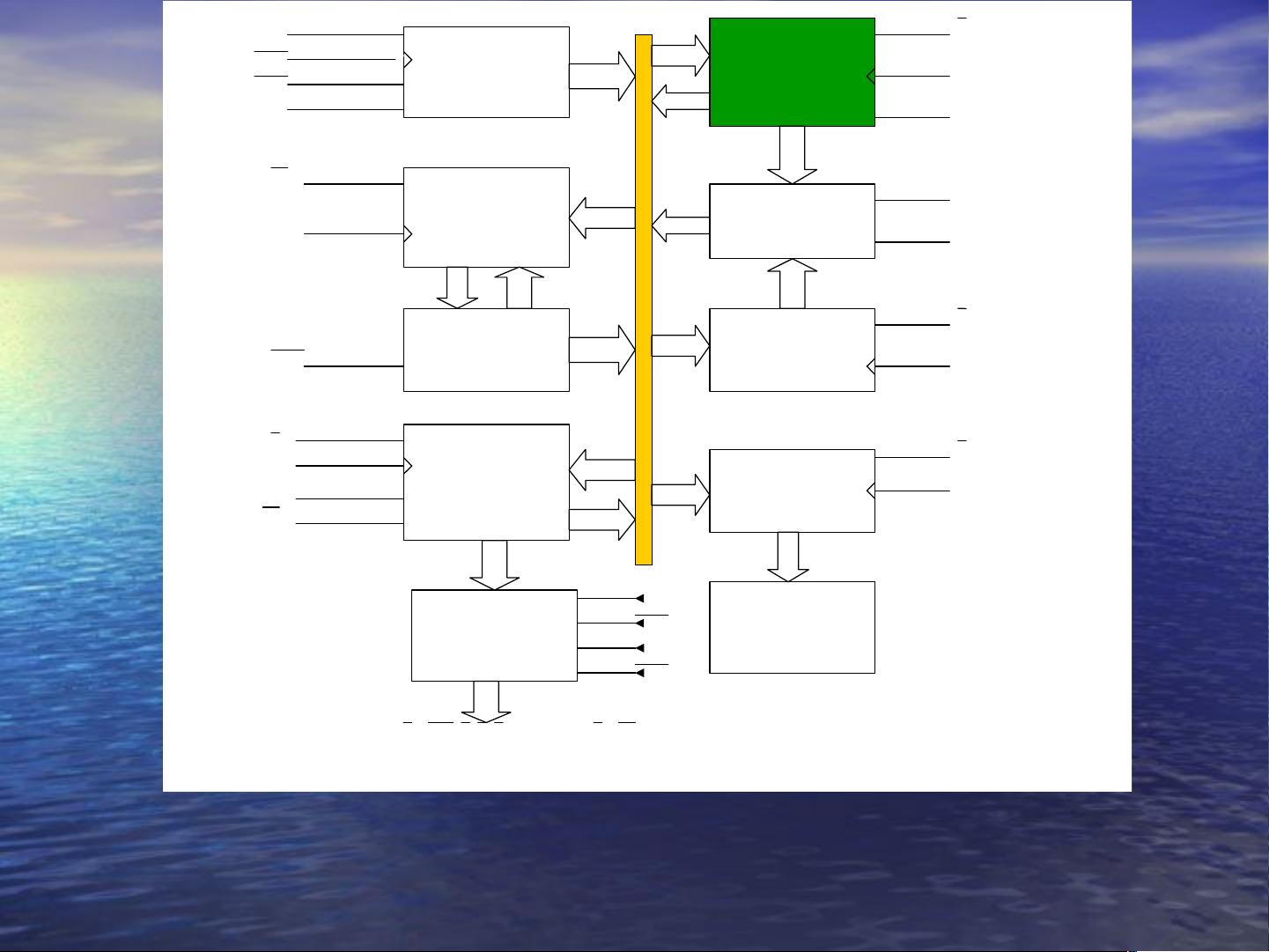

SAP-1CPU是一种简化版的8位CPU,其组成架构包括以下几个关键部件:

1. 程序计数器 (PC):这是一个4位计数器,用于记录当前要执行的指令地址,范围是0到15。每次执行完一条指令,PC会自动加1,跳转到下一个指令地址。

2. 输入与MAR (Memory Access Register):输入部分负责接收来自外部的指令或数据,而MAR则用于临时存储即将被读取或写入内存的地址。

3. 16*8 ROM:这是只读存储器,存储预设好的程序或常量。16表示地址线宽度,可以访问16个不同的位置;8表示数据线宽度,每个位置能存储8位二进制数据。

4. 指令寄存器 (Instruction Register):用于存储从内存读取的当前指令。

5. 累加器 (Accumulator A):用于暂时存储计算结果,通常是CPU内部计算的核心部分。

6. 加法/减法器 (Adder/ subtractor):执行加法和减法运算。

7. 输出寄存器 (Output Register):在运算完成后,将结果暂存于此,准备输出到外部设备。

8. 控制器/时序器 (Controller/sequencer):控制整个CPU的运行流程,根据指令解码产生必要的控制信号。

在SAP-1CPU的指令系统中,会涉及到不同类型的寻址方式,例如直接寻址、立即寻址等,这些决定了如何获取操作数。同时,程序设计涉及如何编写指令序列,实现特定功能。

在计算机体系结构的分类中,除了冯·诺依曼结构,还有哈佛结构。x86处理器遵循冯·诺依曼结构,而ARM和51处理器则是对冯·诺依曼结构的改进型,比如在哈佛结构中,程序和数据拥有独立的存储空间,提高了处理速度。

16*8 ROM的设计与仿真涉及到逻辑门电路和Verilog或VHDL等硬件描述语言,用于实现数据存储和读取功能。在仿真过程中,会验证ROM是否能正确地按照指定地址返回预设的数据。

8位CPU电路设计是一个综合性的任务,涵盖计算机体系结构、数字逻辑、微指令设计等多个方面的知识。通过SAP-1CPU的学习,可以深入了解计算机底层的工作原理。

2018-06-04 上传

2022-06-10 上传

2020-02-08 上传

2023-07-06 上传

2021-10-19 上传

2022-06-20 上传

170 浏览量

2010-04-28 上传

2023-12-18 上传

YLPJ2011

- 粉丝: 0

- 资源: 4

最新资源

- ssmcache:这是一个简单的缓存库,仅从SSM参数存储中检索参数

- spot-playground:试用Spot和OpenAPI客户端生成器

- ZoomInfo ReachOut: B2B Contact & Company Info-crx插件

- VB仿LED中英文滚动字幕显示屏

- latex_3d_objects_with_sketch:在Tex中使用草图绘制3D对象

- WN86.github.io:Hexo博客

- DS1302.zip_VHDL/FPGA/Verilog_VHDL_

- React-Expense-Tracker

- ml:机器学习测试库

- naughty-bobby:一个名为Bobby的顽皮孩子在打向北极的途中大声疾呼圣诞老人的屁股的游戏

- 欧姆龙(OMRON)CP1E经济型PLC中文样本

- PyPI 官网下载 | smartnoise-synth-0.2.1.tar.gz

- faux:有用的软件包的集合

- matlab心线代码-eNRBM:EMR驱动的非负受限玻尔兹曼机

- has-reflect-support-x:测试是否支持ES6 Reflect

- dbaddinslides:DB Addin的幻灯片