组合逻辑电路详解:从译码器到奇偶校验电路

版权申诉

52 浏览量

更新于2024-07-03

收藏 7.79MB PPT 举报

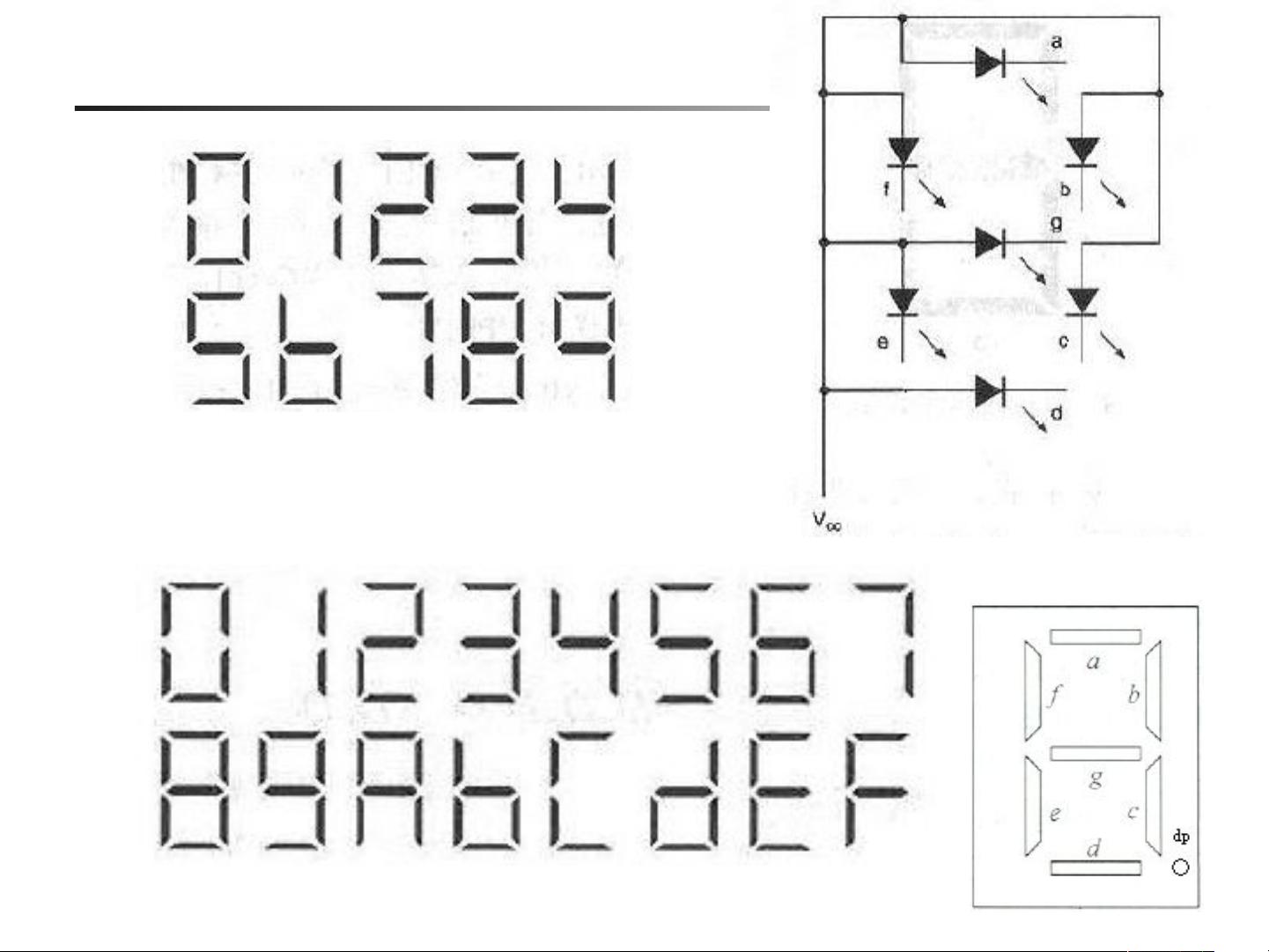

"该资源是关于数字逻辑与数字系统的第5章——组合逻辑电路的讲解。主要内容包括译码器、编码器、数据分配器与数据选择器、数值比较电路、算术运算电路、奇偶校验电路以及如何利用中规模集成电路进行组合电路的分析与设计。其中,详细介绍了各种类型的译码器,如二进制译码器、二-十进制译码器和七段字型码译码器,并提供了3线-8线译码器74HC138的功能表和Verilog代码示例。"

在数字逻辑中,组合逻辑电路是由门电路组成的,它们没有记忆功能,输出仅取决于当前的输入状态。本章重点讲解了以下几个关键知识点:

1. **译码器**:译码器是一种将特定输入二进制代码转换为一组输出信号的电路。例如,二进制译码器接受一组二进制输入,产生与输入代码对应的输出,例如3线-8线译码器74HC138,它有3个输入和8个输出,当输入为特定的3位二进制数时,对应输出变为高电平。

2. **编码器**:与译码器相反,编码器将多个输入信号编码成一个二进制代码。未在描述中详细展开,但编码器常用于将离散的输入信号转换为二进制编码,例如优先编码器。

3. **数据分配器与数据选择器**:数据分配器根据地址输入将单一数据源分配到多个输出;数据选择器则根据控制信号从多个数据输入中选择一个数据源进行传输。

4. **数值比较电路**:这些电路用于比较两个数字的大小,通常包含异或门和其他逻辑门来判断数字之间的关系(大于、小于或等于)。

5. **算术运算电路**:这些电路执行基本的数学操作,如加法、减法、乘法和除法,常用于计算器和计算机硬件中。

6. **奇偶校验电路**:用于检测数字序列中的错误,通过计算位数的奇偶性来提供简单的错误检测。

7. **中规模集成电路构成组合电路的分析与设计**:这部分可能涉及如何利用现成的集成电路,如74系列或其他逻辑器件,来构建复杂的组合逻辑系统,包括使用Verilog等硬件描述语言进行设计和仿真。

理解这些知识点是电子工程和计算机科学的基础,对于设计和分析数字系统至关重要。例如,译码器常用于地址解码,以确定存储器或I/O设备的特定位置;数据选择器和分配器在数据总线管理和多路复用应用中起到关键作用;而算术运算电路是所有数字处理器的心脏。

2021-09-17 上传

2022-05-31 上传

2022-06-14 上传

2022-05-31 上传

2022-06-17 上传

2022-06-17 上传

2022-06-17 上传

2022-06-17 上传