计算机科学:MIPS汇编、硬件结构与性能分析

需积分: 0 83 浏览量

更新于2024-08-04

收藏 426KB DOCX 举报

"期中-综合练习(1)1"

这篇资料涵盖了多个计算机体系结构和编程语言相关的知识点,主要涉及C#编程、MIPS汇编语言、计算机指令编码、硬件结构如乘法器和浮点加法器、数据通路设计、以及处理器性能比较。

1. MIPS汇编语言:

- C语句`a=b+c;`对应的MIPS汇编代码可能是`add $t0, $t1, $t2`,假设`b`存储在$t1中,`c`存储在$t2中,结果`a`存储在`t0`里,其中$t0、$t1和$t2是 MIPS 的寄存器。

2. 指令编码:

- R型、I型和J型指令通常指的是MIPS指令系统中的三种基本指令格式,分别用于不同的操作类型,如寄存器间操作、立即数操作和跳转操作。R型指令包含三个寄存器操作数,I型指令有一个立即数和两个寄存器,J型指令用于表示绝对跳转地址。

3. 寄存器编号方案与指令编码:

- lw$t0,16($t1) 是一个I型指令,其机器码取决于特定的指令编码方案,这需要查看给定的表格来确定。

4. 控制流:

- bne(不等于)指令如果条件满足,会改变程序计数器PC的值。在这个例子中,如果`t0`不等于`t1`,PC会加100,所以下一条指令的地址是0x1010。

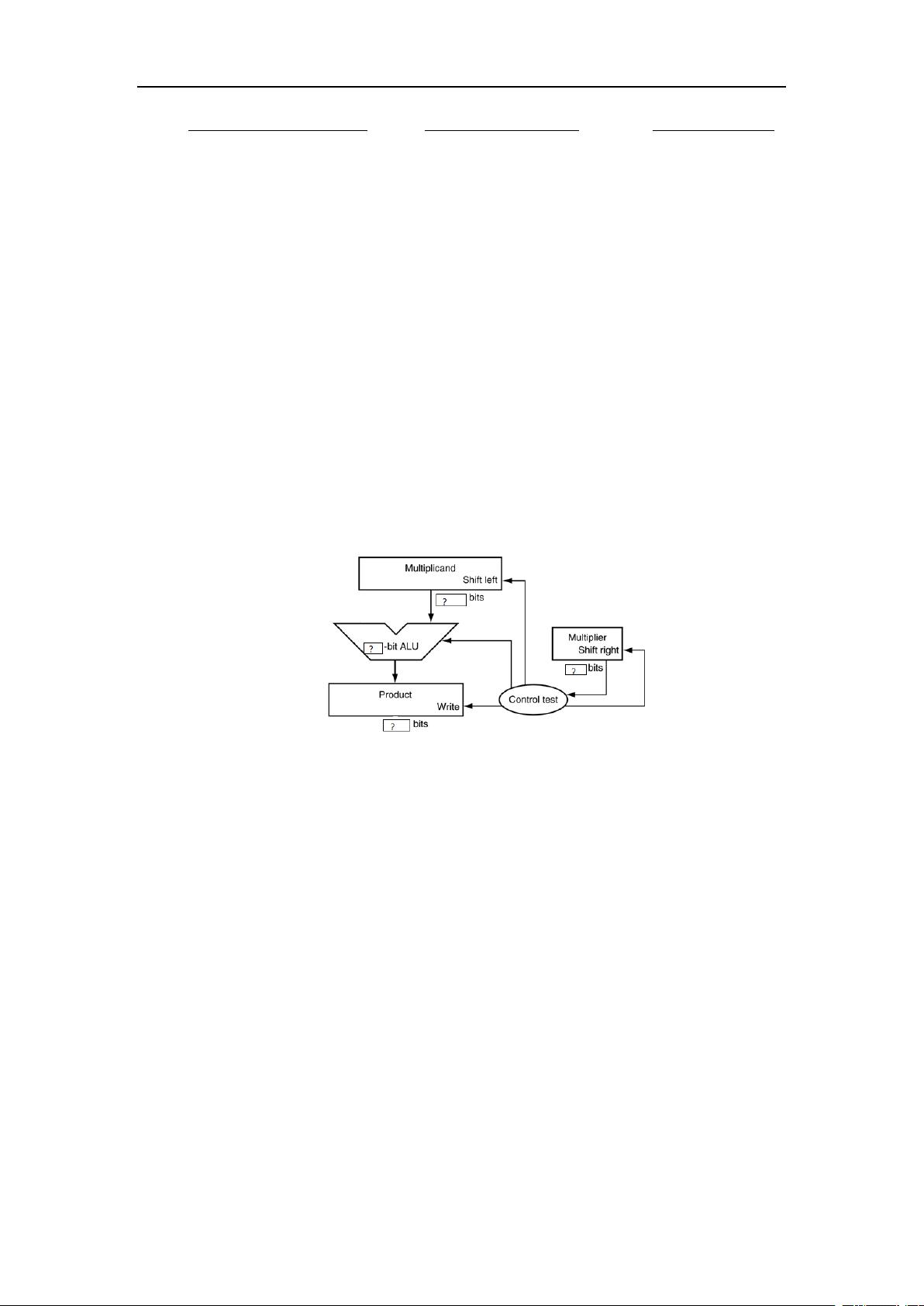

5. 8bitx8bit乘法器结构:

- 完成ALU的输入连线需要了解具体ALU的结构和操作,包括如何进行加法、减法和移位。

- 寄存器宽度应为8位,因为处理的是8bit的数据。

- 移位方向可能需要根据乘法运算的具体实现来决定,例如左移表示乘以2的幂次。

6. 浮点加法器结构:

- 数据连线的补充依赖于浮点数的表示方式(IEEE 754),包括符号、指数和尾数部分。

- 功能描述可能包括“加法”、“比较”和“规格化”等。

7. 单周期数据通路:

- 地址更新电路通常包括PC加上指令长度来形成下一条指令的地址。

- 执行add指令时,readregister1和readregister2读取的是t1和s2的值,即15和20,而Readdata2输出的是它们相加的结果,即35。

8. C代码转换:

- C代码可能是`int i, result, *MemArray; i = t1; result = s2; MemArray = s0;`

9. 控制部件的真值表:

- 需要列出所有可能的指令和对应控制信号的状态。

10. 处理器性能比较:

- 性能最高的处理器是按每秒执行的指令数(IPC,Instructions Per Cycle)计算的,这里需要计算P1、P2、P3的IPC并比较。

- 计算执行10秒的程序的时钟周期数和指令数,需要用到每个处理器的时钟周期和CPI。

- 减少30%时间意味着需要提高时钟频率,同时考虑到CPI增加20%,需要求解新的时钟频率公式来满足这个目标。

这些知识点涉及到计算机硬件、软件和体系结构的多个层面,对于理解计算机的工作原理非常重要。

2021-10-27 上传