Calibration for Split Capacitor DAC in SAR ADC

Zhe Li

1

, Yuxiao Lu

1

, Tingting Mo

1

*

1

Center for Analog/RF IC (CARFIC), School of Microelectronics,

Shanghai Jiaotong University, Shanghai 200240, China

* Email: motingting@ic.sjtu.edu.cn

Abstract

The nonlinearity of split capacitor DAC (CDAC) in SAR

ADC is mainly caused by the mismatch and parasitic

effect of the bridge capacitor. A tunable capacitor array

for compensation can be a solution. This paper first

analyzes the nonlinearity of the split capacitor structure,

and then proves that the linear tuning method results in

linearity improvements and finally, an improved tunable

structure is proposed by calculating the minimal step

which keeps the tuning error within 0.5LSB. The new

implementation achieves smaller area and less power

consumption during the calibration, while maintaining

the same circuit complexity. Behavioral Simulations

based on a 5b-5b split DAC show that the proposed

calibration further improves SNDR and SFDR by 2.2dB

and 1.6dB, respectively compared with the prototype of

compensation capacitor array.

1. Introduction

Recent years have witnessed the rapid development

of charge-redistribution successive approximation

register analog-to-digital-converter (SAR ADC) because

of its low power consumption, minimal analog featureˈ

and the intrinsic advantage from process scaling. In

high-resolution high-speed applications, however, the

SAR architecture is rarely seen due to various technical

barriers. One is large input capacitors, which causes

insufficient time settling and large power consumption.

For traditional binary-weighted capacitive DAC, the

input load capacitance and area increase exponentially

with the number of bits.

Driven by such demands, split capacitor structure is

introduced [1-4]. It can significantly attenuate the total

capacitance with a bridge capacitor added. However, the

fractional-value bridge capacitor is hard to match and is

highly sensitive to parasitic effect, and the linearity

would be thereby severely damaged. To calibrate the

above nonlinear elements, a charge domain

compensation focusing on the calibration of the top-plate

parasitic capacitor was proposed in [1]. Unfortunately,

the mismatch of fractional value capacitor itself was

ignored. [2] suggested an extra top-plate tunable

capacitor to ground. The tunable array improves the

linearity, but the structure remains to be optimized for

better calibration performance.

This paper proposes a modified structure promising

better calibration compared with [2]. The sequence of

this paper is to analyze the linearity performance of split

capacitor DAC at first, and then to prove the linear

tuning [2] of the compensation array results in a linear

SNDR improvement. By revealing how the different

tunable array affect the calibration performance, an

improved version is presented. The new tunable array is

area-efficient and power-saving during the calibration.

Behavioral simulations show that SNDR and SFDR are

improved 2.2dB and 1.6dB, compared with the method

in [2]. DNL and INL are optimized to +0.15/-0.15LSB

and +0.15/-0.18LSB, respectively.

2. Split DAC linearity analysis

The nonlinearity of SAR ADC is mainly caused by

non-binary weights due to capacitor mismatch and

parasitics. To examine the static random mismatch of

capacitors only, Monte Carlo simulation of a 10-bit

traditional binary-weighted DAC in 65nm process is

carried out. To achieve 0.5LSB INL for 10bit resolution

with 99% probability, the minimal capacitance is 20fF

for metal-oxide-metal (MoM) capacitors. In this case,

the total capacitance will count to 20.48pF, which is an

unacceptable size in terms of DAC settling, power

dissipation and physical area.

Split Capacitor DAC can effectively reduce the total

capacitance since the bridge capacitor C

B

separates the

DAC into an i-bit LSB and a j-bit MSB binary-scaled

sub-DAC. The equivalent total output capacitance is

reduced by

2

i-1

times compared to the conventional

structure. The bridge capacitor is usually placed in the

middle of the DAC array to obtain an optimal tradeoff

between the total capacitance and the standard deviation

of INL [3].

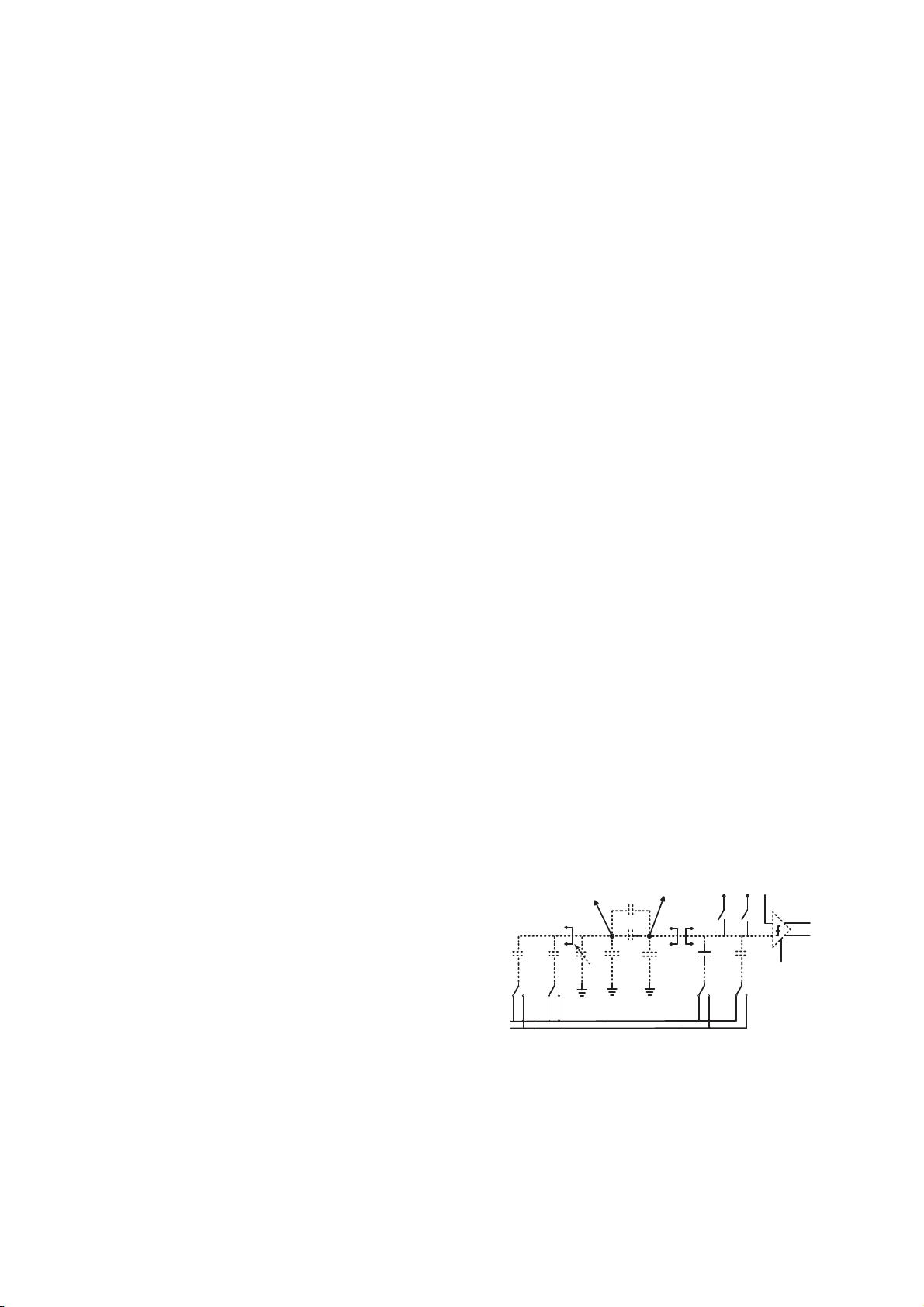

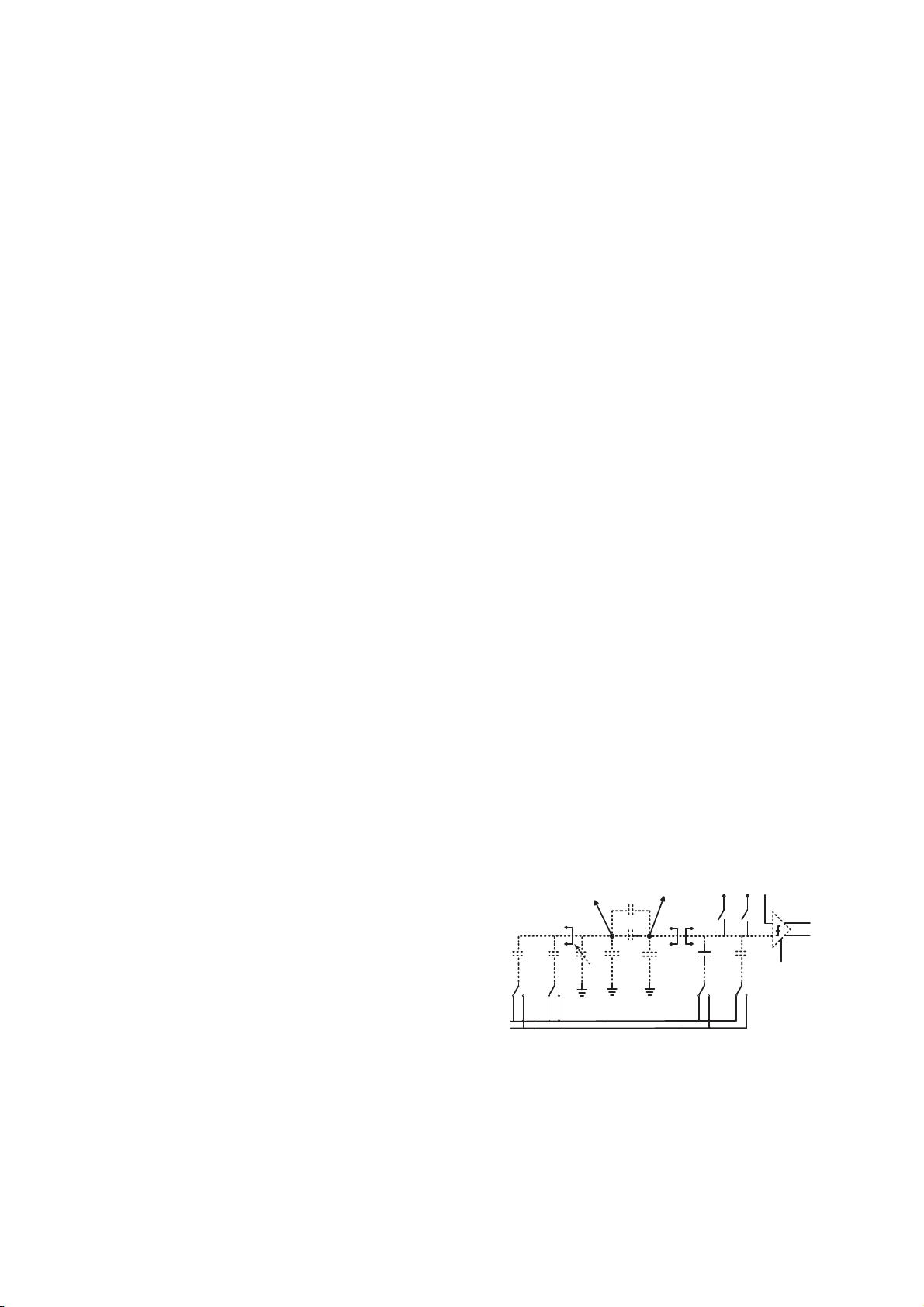

&

())

6$03

9&0

6:B9&0B1

&03B23

&03B21

ELWBQ! ELWBQ!

ELWBQ!

&03B&/.

&

9

7R'$&3SDUW

'$&1SDUW

&

Fig.1 Fully-differential 5b-5b split CDAC non-

ideal

model with tunable array C

V

.

978-1-4673-6417-1/13/$31.00 ©2013 IEEE