Quartus II 与 Modelsim 联合仿真的详细步骤指南

需积分: 18 194 浏览量

更新于2024-09-14

收藏 496KB PDF 举报

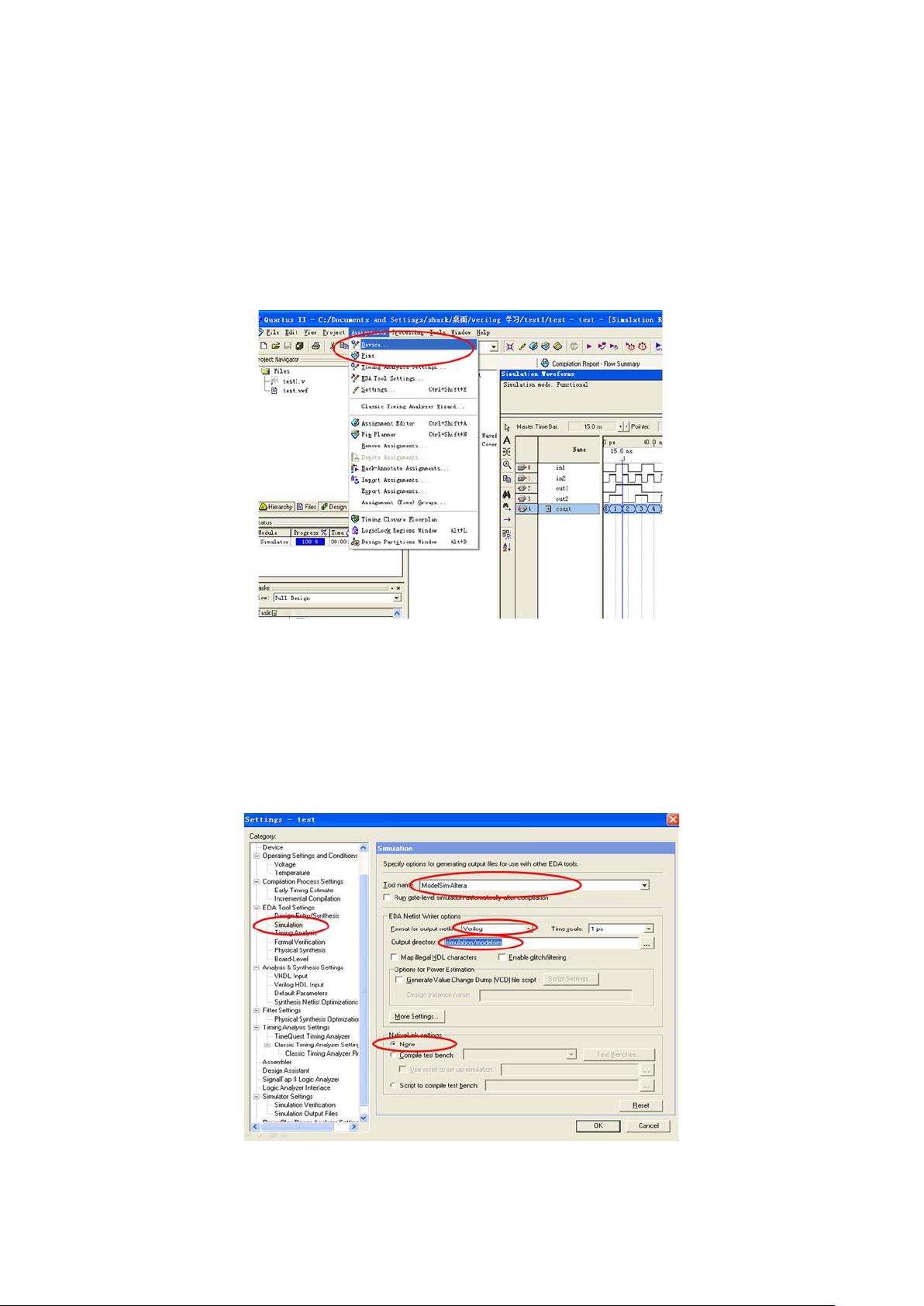

本文档详细介绍了如何在Quartus II和Modelsim这两款常用的硬件描述语言(HDL)设计工具之间进行联合仿真。首先,用户需要在Quartus II中创建一个新的工程,编写好源代码,通常使用Verilog或VHDL语言。源代码编译无误后,进入Assignment部分,选择Device选项,并将仿真工具设置为Modelsim或Modelsim-Altera,根据具体使用的版本进行选择。

在Output netlist格式设置中,指定测试台(testbench)的语言和输出路径,通常默认为simulation/modelsim。对于首次使用,用户需要配置Modelsim的路径,这包括在Tools > Options > EDAToolOptions中修改Modelsim或Modelsim-Altera的路径,确保它与Modelsim.exe的实际位置相符。

接下来,用户需要使用Processing菜单的Start > StartTestBenchTemplateWriter功能来生成testbench文件,文件扩展名为.vt。此时,用户需要编写并确认testbench文件的内容,确保其与源代码中的顶层模块名称一致。

在Quartus II的NativeLink settings中,选择Compile testbench选项,然后在TestBench窗口中新建一个测试设置,输入生成的testbench文件路径,以及设置正确的参数,包括顶层模块名称。最后,点击Ok按钮,准备进行仿真。

用户可以通过Tool > RunEDASimulationTool > EDARTL Simulation启动联合仿真,可以选择进行门级仿真或时序仿真,具体取决于设计的需求。在仿真过程中,模型会根据Quartus II的描述和Modelsim的验证工具进行交互,以检查设计的正确性和性能。

总结来说,本教程提供了从工程设置、testbench生成到仿真执行的完整步骤,对于想要在Quartus II和Modelsim之间进行协同工作的HDL设计师来说,这是一个实用的指南。理解并掌握这些步骤有助于提高设计效率和调试质量。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2008-01-26 上传

2022-08-08 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

uestchuang

- 粉丝: 5

- 资源: 5

最新资源

- SourceAnywhere For VSS 配置手册.pdf

- android平台应用程序开发指南

- 可信计算(A.Practical.Guide.to.Trusted.Computing)

- struts2 学习重点笔记

- 怎样做实验室的工作,MiT新生必读

- 至少应该阅读的九本C++著作

- 西门子GSM TC35的AT命令

- moreEffectiveC++_侯捷.pdf

- STC89系列 中文资料 PDF格式

- 基于WWW的劳资人事管理系统

- wps表格初级教程4

- Struts2轻松入门

- 基于2D模板与3D包围式标定块的鱼眼相机标定

- 基于关键词的WEB文献自动跟踪系统的实现方法

- ISD1400的资料

- C语言写的电子万年历代码