SOC时序分析关键:理解与应用跳变点

128 浏览量

更新于2024-08-31

收藏 160KB PDF 举报

"理解EDA/PLD中的SOC时序分析中的跳变点至关重要,因为它涉及计算设计节点上的时延和过渡值。跳变点是逻辑高电平的百分比,用于衡量压摆率和时延。本文旨在阐述跳变点的定义、固定方式以及在时序模型中的应用。

1. 跳变点的定义:

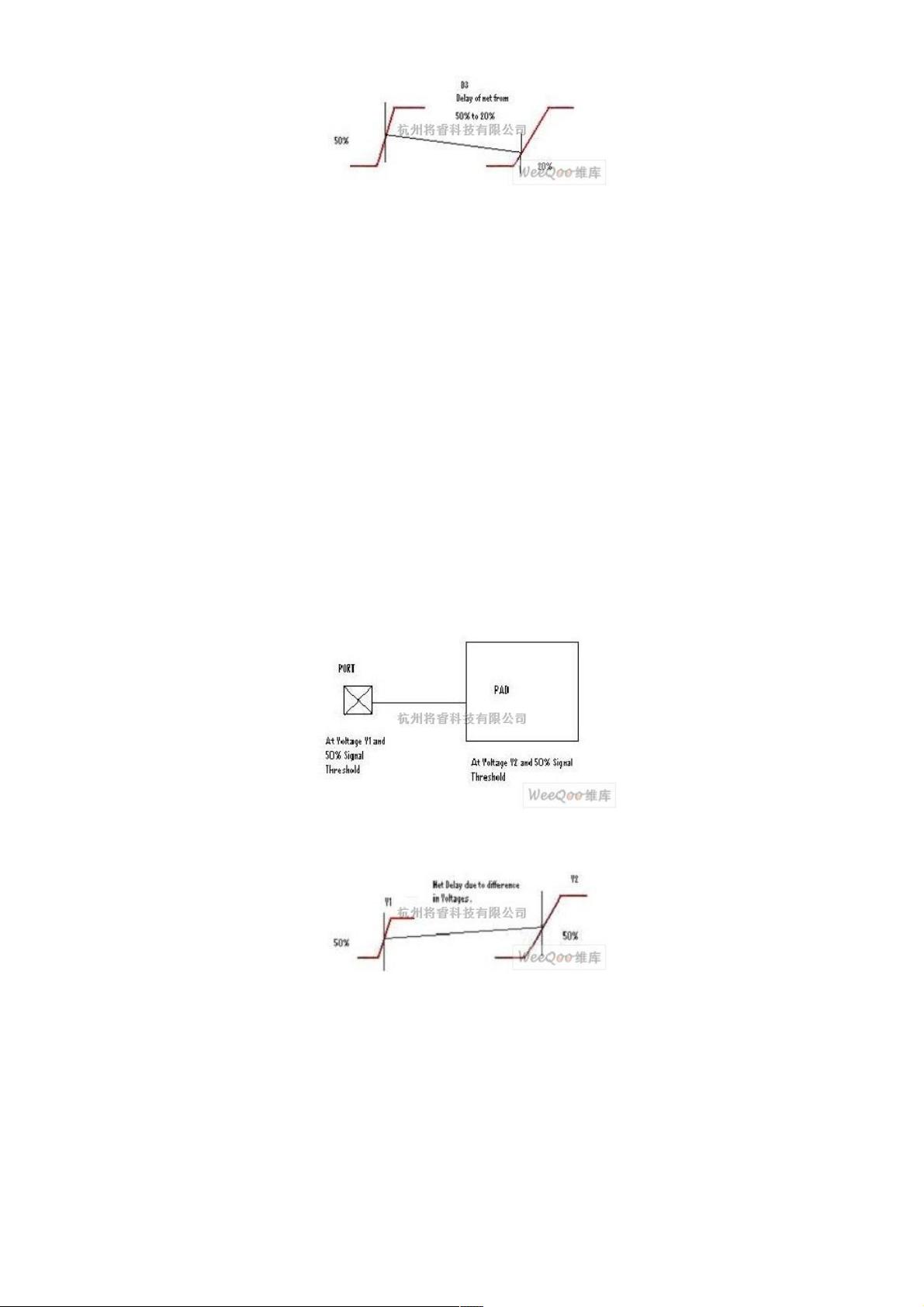

跳变点是评估电路性能的关键指标,特别是在压摆率和时延计算中。它表示信号从低电平到高电平或反之的转换过程中达到特定电平的点。图1(a)展示了压摆率跳变点,而图1(b)则展示时延跳变点。在标准单元和硬模块/IP的时序分析中,跳变点描述了引脚的过渡特性。

2. 固定跳变点的意义:

跳变点在技术节点的规格中通常是固定的,以确保测量的时延和压摆率与实际的模拟波形(如Spice)相匹配。选择线性区(例如20%-80%)的跳变点可以得到更准确的压摆率测量,因为此时晶体管处于线性工作状态,输出波形的线性区域更利于时序分析工具计算单元时延。

3. 时序模型中的跳变点句法:

在时序模型文件(如.liberty文件)中,跳变点的描述是关键。模型会指定不同的跳变点值,用于时序分析工具计算时延。例如,模型可能包含关于输入和输出跳变点的详细信息,这些信息决定了工具如何处理信号的上升和下降时间。

4. 时序签字的重要性:

在SOC设计的后期阶段,正确的时序分析是必要的,因为错误的跳变点理解可能导致时序签字问题。后端设计工程师必须了解跳变点的概念,以避免潜在的设计问题。

5. 影响因素:

除了跳变点的位置,晶体管的电压阈值(Vt)也会影响跳变点的计算。当输入电压超过晶体管的Vt时,输出波形开始线性变化,这直接影响时序分析的结果。

6. 结论:

为了确保有效的SOC时序分析,设计者需要深入理解跳变点的定义、其在计算中的作用以及如何在时序模型中正确使用。掌握这些知识能够帮助工程师优化设计,防止潜在的时序问题,从而提高整个系统级芯片的性能和可靠性。"

2020-12-09 上传

2020-11-17 上传

2020-12-10 上传

2020-11-12 上传

2020-12-10 上传

2020-11-11 上传

2020-12-08 上传

2020-11-21 上传

2022-11-07 上传

weixin_38610682

- 粉丝: 6

- 资源: 878

最新资源

- 探索数据转换实验平台在设备装置中的应用

- 使用git-log-to-tikz.py将Git日志转换为TIKZ图形

- 小栗子源码2.9.3版本发布

- 使用Tinder-Hack-Client实现Tinder API交互

- Android Studio新模板:个性化Material Design导航抽屉

- React API分页模块:数据获取与页面管理

- C语言实现顺序表的动态分配方法

- 光催化分解水产氢固溶体催化剂制备技术揭秘

- VS2013环境下tinyxml库的32位与64位编译指南

- 网易云歌词情感分析系统实现与架构

- React应用展示GitHub用户详细信息及项目分析

- LayUI2.1.6帮助文档API功能详解

- 全栈开发实现的chatgpt应用可打包小程序/H5/App

- C++实现顺序表的动态内存分配技术

- Java制作水果格斗游戏:策略与随机性的结合

- 基于若依框架的后台管理系统开发实例解析