缓冲区结构

缓冲区结构缓冲区结构

缓冲区结构效率分析

效率分析效率分析

效率分析

苏

苏苏

苏

航

航航

航

1

,

,,

,薛彦涛

薛彦涛薛彦涛

薛彦涛

2

(1. 兰州大学信息科学与工程学院,兰州 730000;2. 中国航天二院研究生院,北京 100854)

摘

摘摘

摘 要

要要

要:

::

:I/O 设备与 CPU 的速度不匹配,制约了计算机系统性能的进一步提高。为此,根据计算机体系结构,对缓冲区结构的效率进行分

析,使用 EDA 计算机辅助设计软件 QuartusII 设计异步双时钟 FIFO 缓冲区,并对其进行仿真验证及数据记录,通过对数据的分析,证明

系统整体效率与 FIFO 效率密切相关,只有实现 FIFO 效率的最大化,才能使系统整体效率最大化,同时 FIFO 效率最大化也只能在完成系

统效率最大化的过程中得以实现。

关键词

关键词关键词

关键词:

::

:异步 FIFO;结构效率;EDA 设计;亚稳态

Efficiency Analysis of Buffer Structure

SU Hang

1

, XUE Yan-tao

2

(1. School of Information Science & Engineering, Lanzhou University, Lanzhou 730000, China;

2. The Graduate School of The Second Academy of China Aerospace, Beijing 100854, China)

【

【【

【Abstract】

】】

】To solve the problem of the data transmission speed mismatch between I/O device and CPU, this paper analyzes the efficiency of

various buffer structure based on computer architecture. With QuartusII which is Computer-Aided Design(CAD) using Electronic Design

Automation(EDA) software, it designs the asynchronous dual-clock First In First Out(FIFO) buffer, including the buffer structure of the simulation,

data recording, and analysis of its effectiveness. Analysis results show that the efficiency of computer system is closely related with that of FIFO. To

improve the efficiency of computer system, the efficiency of FIFO is supposed to be improved first. At the same time, the improvement of the

efficiency of FIFO is based on the improvement of the efficiency of computer system.

【

【【

【Key words】

】】

】asynchronous First In First Out(FIFO); structure efficiency; Electronic Design Automation(EDA) design; metastable state

DOI: 10.3969/j.issn.1000-3428.2011.13.006

计 算 机 工 程

Computer Engineering

第 37 卷 第 13 期

Vol.37 No.13

2011 年 7 月

July 2011

·

··

·专栏

专栏专栏

专栏·

··

·

文章编号

文章编号文章编号

文章编号:

::

:1000—

——

—3428(2011)13—

——

—0020—

——

—06

文献标识码

文献标识码文献标识码

文献标识码:

::

:A

中图分类号

中图分类号中图分类号

中图分类号:

::

:TP301

1

概述

概述概述

概述

中断、

DMA

和通道控制技术使得系统中各

I/O

设备之间、

I/O

设备和

CPU

之间可以并行工作。但

I/O

设备、

CPU

的速

度不匹配问题是客观存在的。这限制了连接的

I/O

设备台数,

而且在中断方式时容易造成数据丢失。可见,

I/O

设备和

CPU

速度不匹配的问题制约了计算机系统性能的进一步提高,限

制了系统的应用范围。

I/O

设备与处理机速度不匹配的问题可

以采用设置缓冲区的方法解决。随着现代科技、制造工艺以

及高新材料的不断发展,

CPU

与低速设备间的速度差越来越

大,这使得速度不匹配问题日益严重。而作为解决这一问题

的缓冲区来说,它的效率的好坏很大程度上制约着计算机的

整体效率。人们之前的研究重点放在研究设计新结构的缓冲

区上,很少对缓冲区结构的效率做客观的研究和评价。本文

使用电子设计自动化

(Electronic Design Automation, EDA)

计

算机辅助设计软件

QuartusII

设计异步

FIFO(First In First Out)

缓冲区,并对其进行仿真验证及数据记录。通过对数据的分

析,得出异步

FIFO

的结构效率以及与系统整体效率的关系。

2

异步

异步异步

异步

FIFO

设计

设计设计

设计

异步

FIFO

是指在不同时钟下,按照先进先出原则工作

在高速设备与低速设备间的,起到存储、缓冲数据传输作用

的缓冲器。它不但解决了设备间速度不匹配的问题,而且适

应了现代大规模集成电路芯片系统包含多时钟,跨不同时钟

区域进行异步数据传输的要求。使用异步

FIFO

可以在

2

个

不同时钟系统之间快速而方便地传输实时数据。在网络接口、

图像处理等方面,异步

FIFO

得到广泛的应用。因此,本文

设计出一款异步

FIFO

,并用

Verilog HDL

语言编程实现,并

使用

EDA

计算机辅助设计软件对其进行仿真,对其结构效率

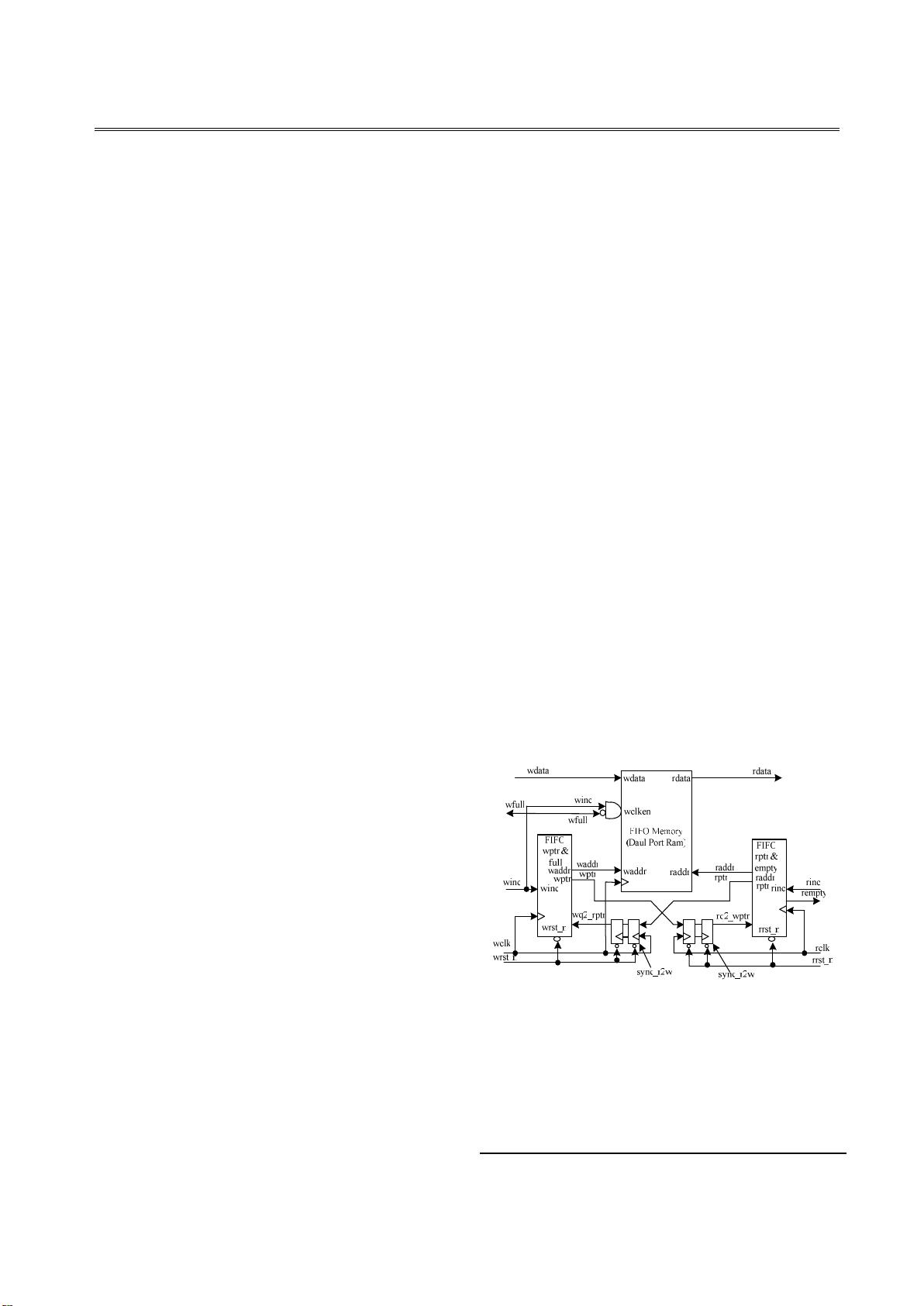

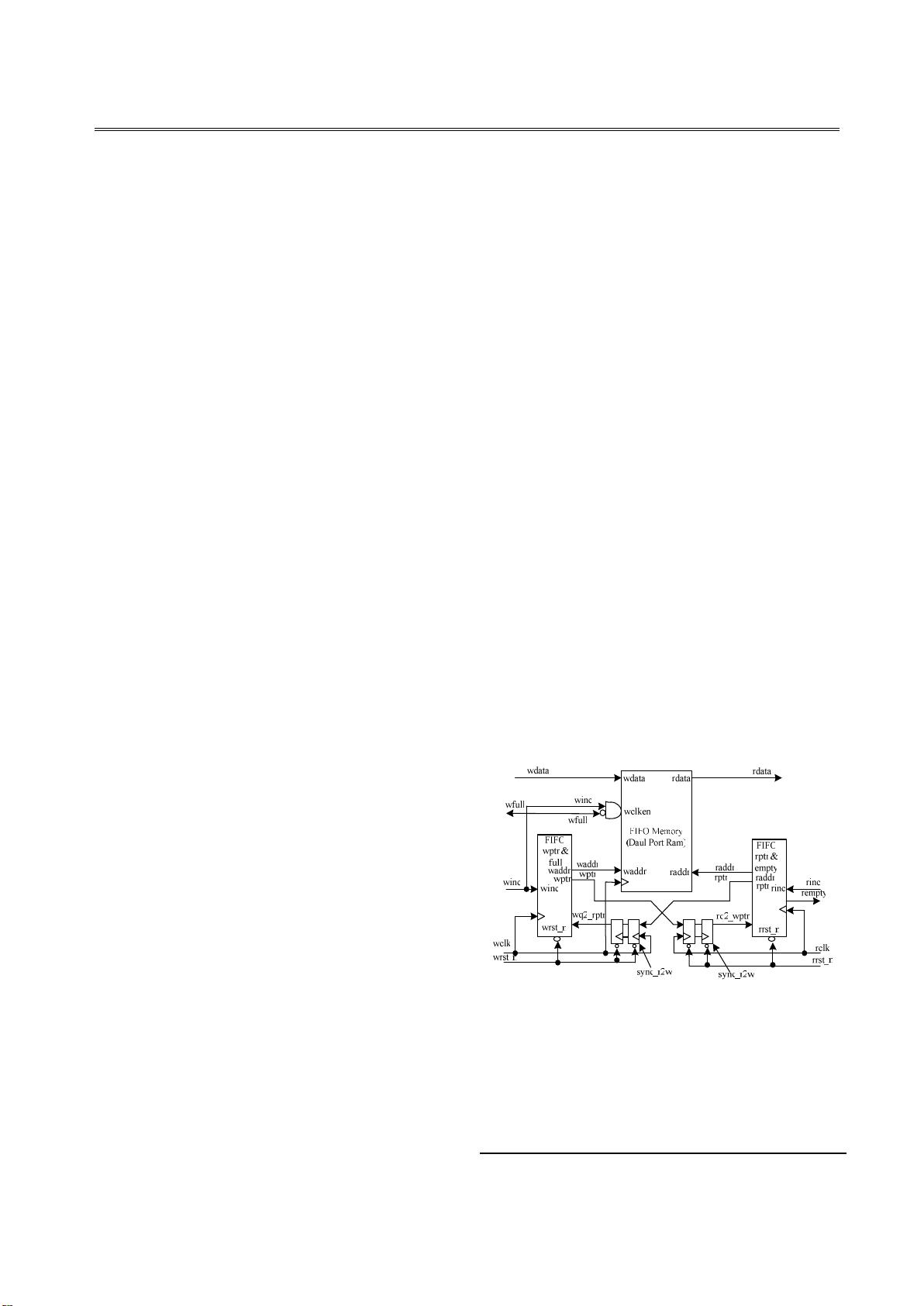

进行分析。图

1

为典型的异步

FIFO

结构。

图

图图

图

1

典型异步

典型异步典型异步

典型异步

FIFO

结构

结构结构

结构

2.1

异步

异步异步

异步

FIFO

设计的必要知识

设计的必要知识设计的必要知识

设计的必要知识

异步

FIFO

设计涉及到的必要知识有:

EDA

软件,亚稳

态,二进制与格雷码相互转化等。

2.1.1 EDA

软件

EDA

软件,即电子系统设计自动化,是超大规模集成电

子器件的厂家,为了能更好地推销他们的产品,在售卖芯片

作者简介

作者简介作者简介

作者简介:

::

:苏 航(1989-),女,学士,主研方向:信息科学;薛彦涛,

硕士研究生

收稿日期

收稿日期收稿日期

收稿日期:

::

:2011-02-01 E-mail:

::

:chenliangsdu@126.com

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

信息提交成功

信息提交成功