ADSP-BF531/ADSP-BF532/ADSP-BF533

Rev. 0 | Page 11 of 56 | March 2004

the vertical blanking intervals. In this mode, the control

byte sequences are not stored to memory; they are filtered

by the PPI.

• Vertical Blanking Only - The PPI only transfers Vertical

Blanking Interval (VBI) data, as well as horizontal blanking

information and control byte sequences on VBI lines.

• Entire Field - The entire incoming bitstream is read in

through the PPI. This includes active video, control pream-

ble sequences, and ancillary data that may be embedded in

horizontal and vertical blanking intervals.

Though not explicitly supported, ITU-R 656 output functional-

ity can be achieved by setting up the entire frame structure

(including active video, blanking, and control information) in

memory and streaming the data out the PPI in a frame sync-less

mode. The processor’s 2D DMA features facilitate this transfer

by allowing the static frame buffer (blanking and control codes)

to be placed in memory once, and simply updating the active

video information on a per-frame basis.

The general-purpose modes of the PPI are intended to suit a

wide variety of data capture and transmission applications. The

modes are divided into four main categories, each allowing up

to 16 bits of data transfer per PPI_CLK cycle:

• Data Receive with Internally Generated Frame Syncs

• Data Receive with Externally Generated Frame Syncs

• Data Transmit with Internally Generated Frame Syncs

• Data Transmit with Externally Generated Frame Syncs

These modes support ADC/DAC connections, as well as video

communication with hardware signaling. Many of the modes

support more than one level of frame synchronization. If

desired, a programmable delay can be inserted between asser-

tion of a frame sync and reception/transmission of data.

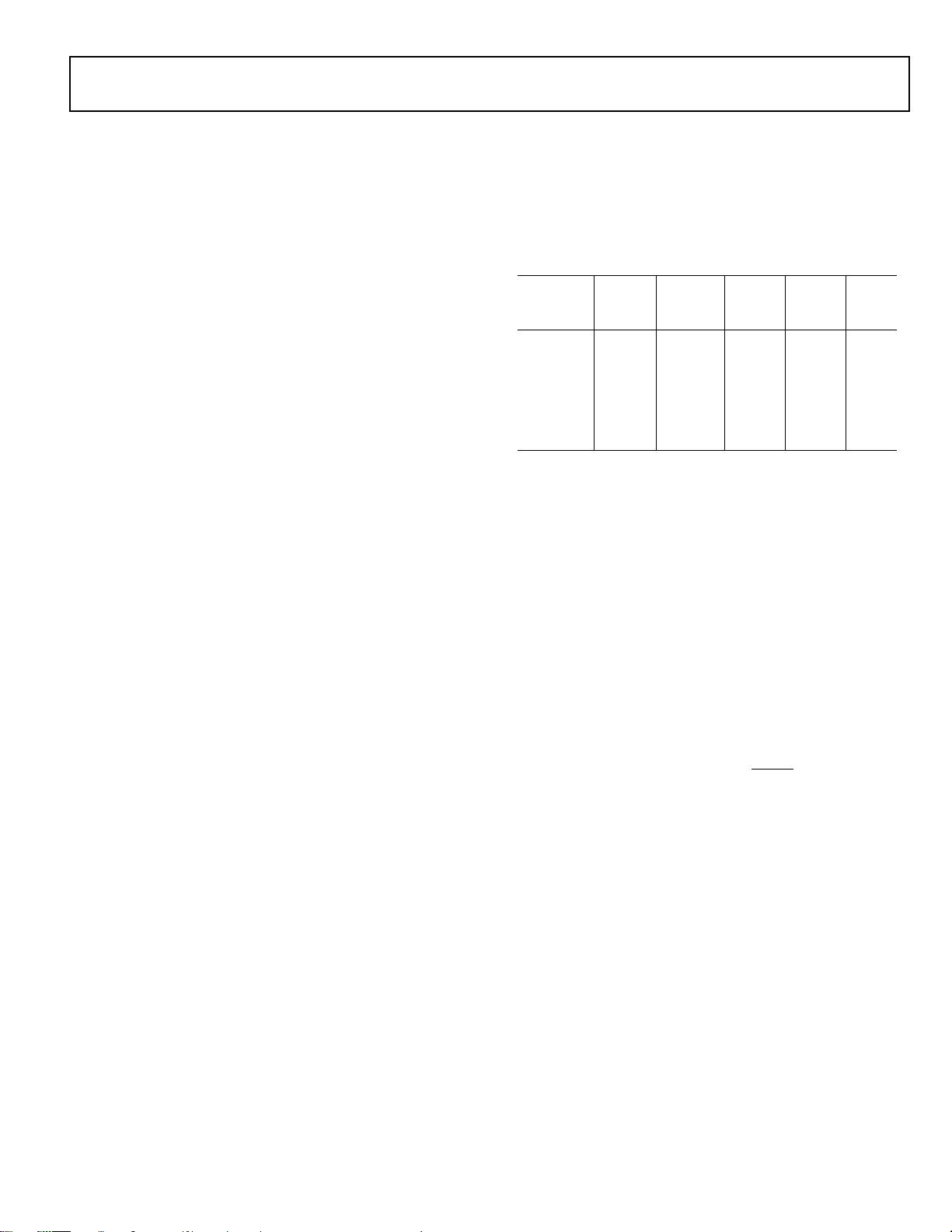

DYNAMIC POWER MANAGEMENT

The ADSP-BF531/2/3 processor provides five operating modes,

each with a different performance/power profile. In addition,

Dynamic Power Management provides the control functions to

dynamically alter the processor core supply voltage, further

reducing power dissipation. Control of clocking to each of the

ADSP-BF531/2/3 processor peripherals also reduces power con-

sumption. See Table 4 for a summary of the power settings for

each mode.

Full-On Operating Mode—Maximum Performance

In the Full-On mode, the PLL is enabled and is not bypassed,

providing capability for maximum operational frequency. This

is the power-up default execution state in which maximum per-

formance can be achieved. The processor core and all enabled

peripherals run at full speed.

Active Operating Mode—Moderate Power Savings

In the Active mode, the PLL is enabled but bypassed. Because

the PLL is bypassed, the processor’s core clock (CCLK) and sys-

tem clock (SCLK) run at the input clock (CLKIN) frequency. In

this mode, the CLKIN to CCLK multiplier ratio can be changed,

although the changes are not realized until the Full-On mode is

entered. DMA access is available to appropriately configured L1

memories.

In the Active mode, it is possible to disable the PLL through the

PLL Control register (PLL_CTL). If disabled, the PLL must be

re-enabled before transitioning to the Full-On or Sleep modes.

Hibernate Operating Mode—Maximum Static Power

Savings

The Hibernate mode maximizes static power savings by dis-

abling the voltage and clocks to the processor core (CCLK) and

to all the synchronous peripherals (SCLK). The internal voltage

regulator for the processor can be shut off by writing b#00 to the

FREQ bits of the VR_CTL register. This disables both CCLK

and SCLK. Furthermore, it sets the internal power supply volt-

age (V

DDINT

) to 0 V to provide the lowest static power

dissipation. Any critical information stored internally (memory

contents, register contents, etc.) must be written to a non-vola-

tile storage device prior to removing power if the processor state

is to be preserved. Since V

DDEXT

is still supplied in this mode, all

of the external pins tri-state, unless otherwise specified. This

allows other devices that may be connected to the processor to

have power still applied without drawing unwanted current.

The internal supply regulator can be woken up either by a Real-

Time Clock wakeup or by asserting the RESET

pin.

Sleep Operating Mode—High Dynamic Power Savings

The Sleep mode reduces dynamic power dissipation by dis-

abling the clock to the processor core (CCLK). The PLL and

system clock (SCLK), however, continue to operate in this

mode. Typically an external event or RTC activity will wake up

the processor. When in the Sleep mode, assertion of wakeup will

cause the processor to sense the value of the BYPASS bit in the

PLL Control register (PLL_CTL). If BYPASS is disabled, the

processor will transition to the Full On mode. If BYPASS is

enabled, the processor will transition to the Active mode.

When in the Sleep mode, system DMA access to L1 memory is

not supported.

Deep Sleep Operating Mode—Maximum Dynamic Power

Savings

The Deep Sleep mode maximizes dynamic power savings by

disabling the clocks to the processor core (CCLK) and to all syn-

chronous peripherals (SCLK). Asynchronous peripherals, such

Table 4. Power Settings

Mode PLL PLL

Bypassed

Core

Clock

(CCLK)

System

Clock

(SCLK)

Core

Power

Full On Enabled No Enabled Enabled On

Active Enabled/

Disabled

Yes Enabled Enabled On

Sleep Enabled Disabled Enabled On

Deep Sleep Disabled Disabled Disabled On

Hibernate Disabled Disabled Disabled Off