优化DDR4接口分析: Cadence工具与案例研究

需积分: 10 125 浏览量

更新于2024-06-30

收藏 3.65MB PDF 举报

在"如何有效分析DDR4接口"的2015年Cadence课程分享PPT中,该讲座深入探讨了DDR4接口设计中的关键问题及其解决方案。主要内容包括:

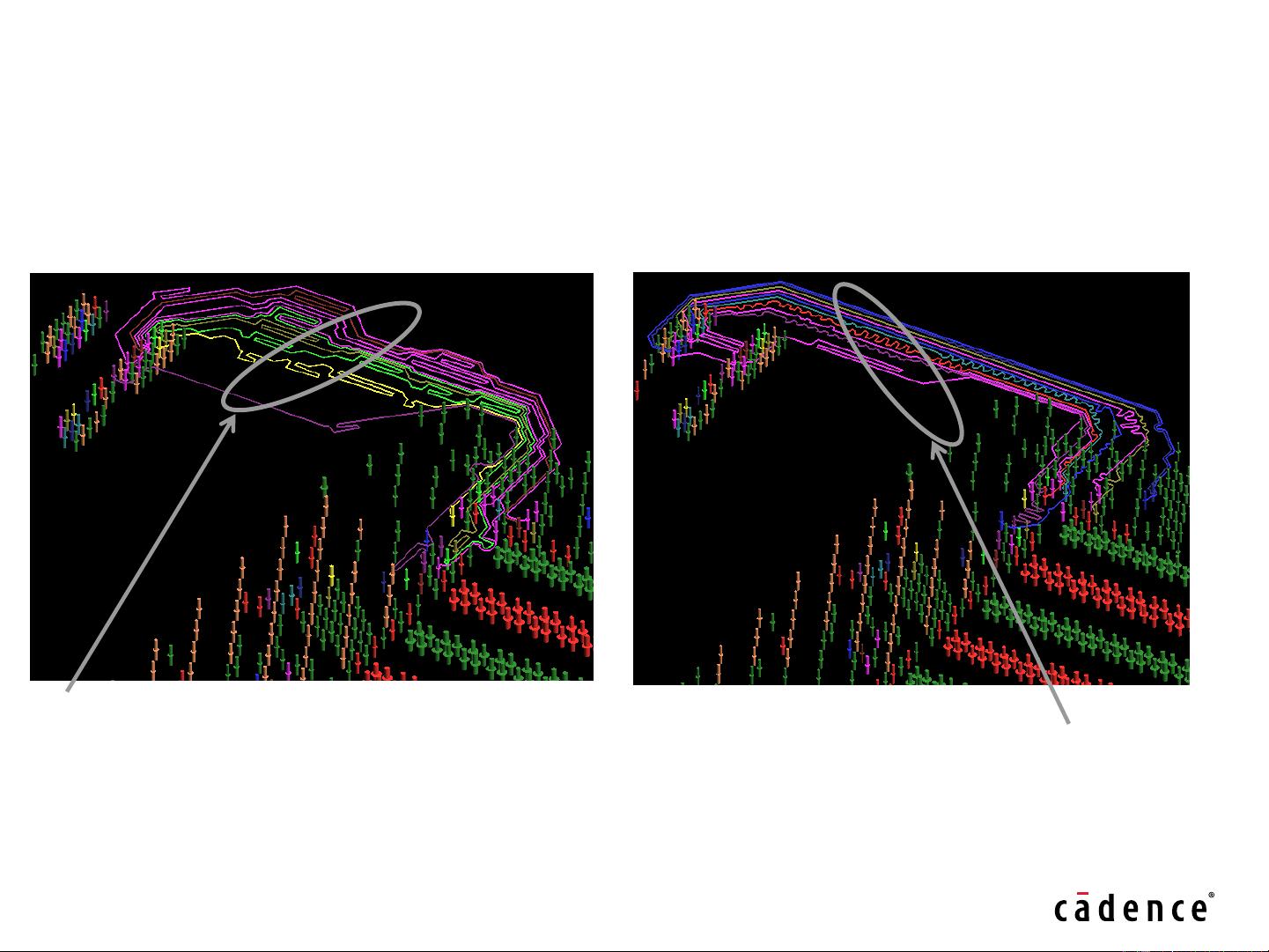

1. 功率感知信号完整性(Power-aware SI):随着内存系统频率的提升和设计密度的增加,DDR4接口面临的挑战显著增多。高速率数据传输、核心电压和I/O电压的降低使得信号质量受到更多噪声的影响,这要求信号完整性(SI)工具能够适应新的设计需求。功率感知的SI分析是解决这些问题的关键,它关注的是在保证电源效率的同时确保信号的可靠传输。

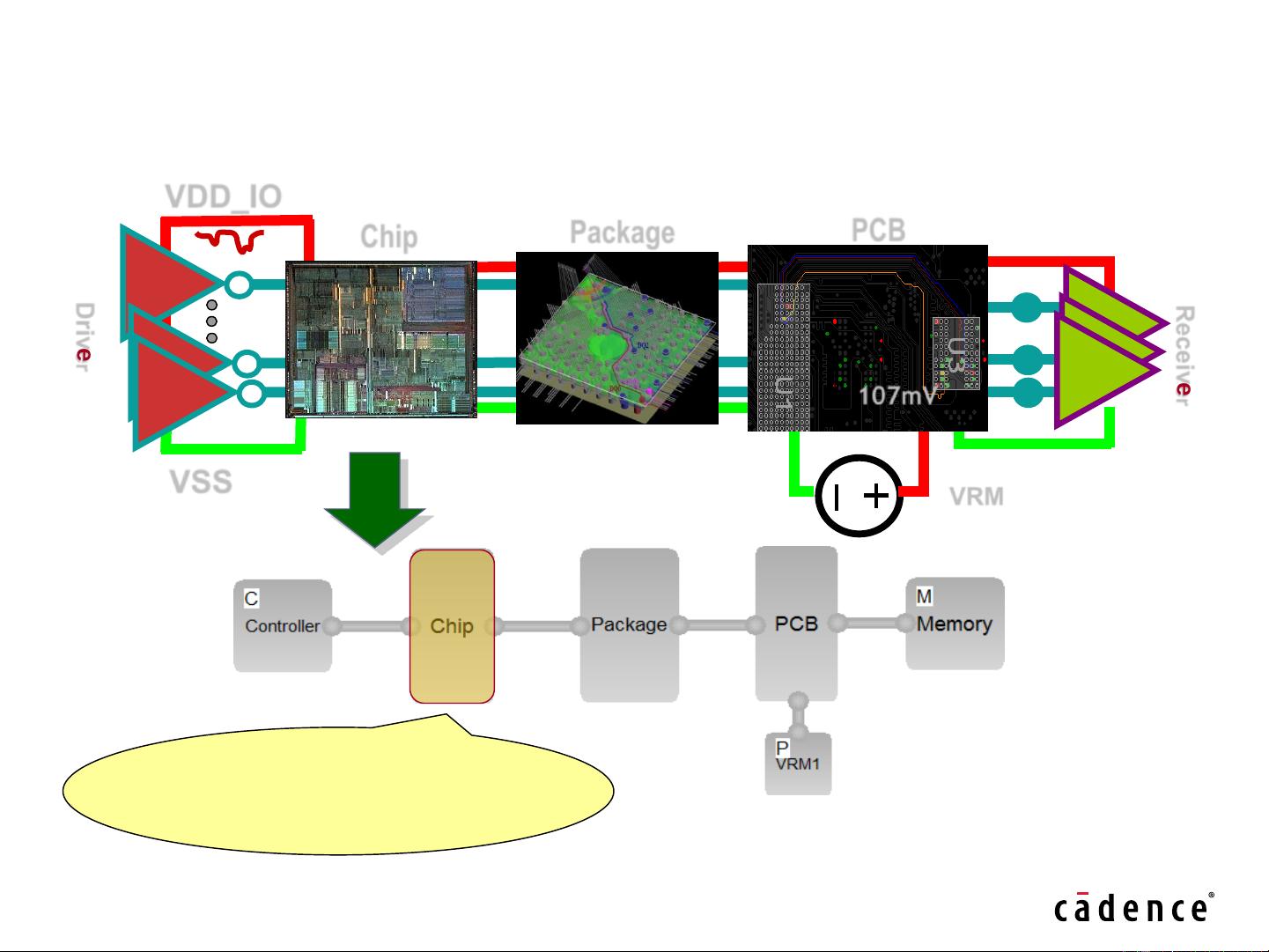

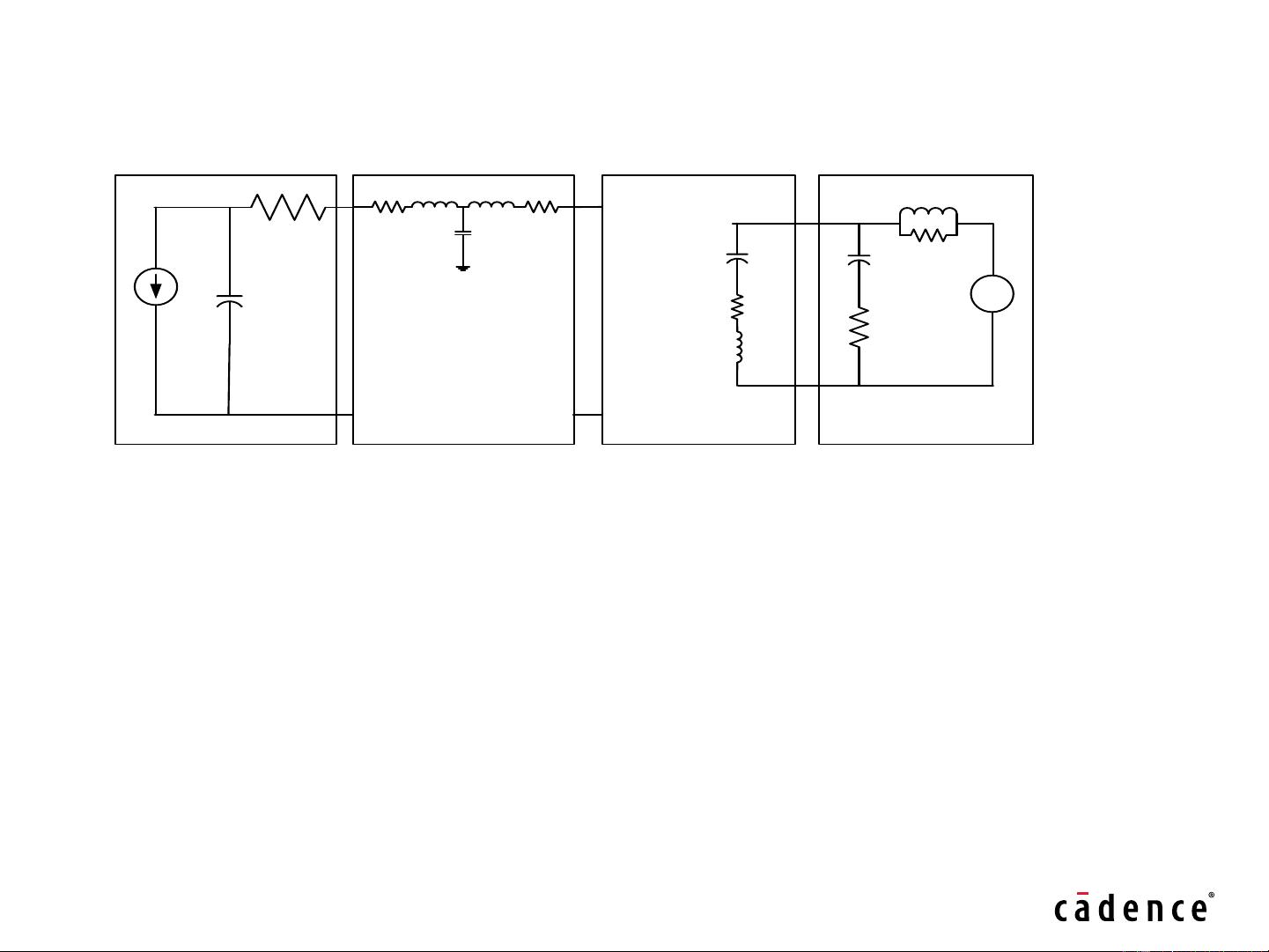

2. 集成核心和功率感知并行总线系统建模方法:通过Cadence-Sigrity工具,讲解了一种综合的系统级建模策略,旨在同时考虑核心功能和电源管理,以便优化并行总线的设计。这种方法有助于设计师在系统级别进行有效分析,确保性能和效率的平衡。

3. Cadence-Sigrity环境下的构建:参与者学习如何在Cadence-Sigrity工具环境中构建一个整合了核心功能和功率管理的并行总线系统。这包括了从概念设计到实现的全过程,以及如何利用虚拟参考设计,如基于Cadence DDR4 IP测试芯片的测试平台。

4. 案例研究:通过一个实际的虚拟参考设计,展示了如何结合Cadence的DDR4 IP测试芯片、封装和PCB,进行仿真与测量的关联性研究。这一步骤对于验证设计性能和实际应用效果至关重要,可以帮助设计师更好地理解和优化接口的信号完整性。

5. 系统级并行总线分析:讨论了在系统层面分析并行总线时所面临的挑战,如电源噪声对信号质量的影响和日益紧缩的噪声预算。这部分强调了SI工具在解决这些问题时的重要性。

6. 经典SI工具的挑战:传统SI工具在应对快速发展的DDR4标准和设计复杂性方面可能存在局限,例如可能无法充分处理高速率和低电压条件下的信号完整性问题。因此,需要不断更新和改进SI工具以满足新的设计需求。

总结来说,这门课程提供了针对DDR4接口设计的深度洞察,涵盖了从理论模型构建到实践应用的全面指导,旨在帮助设计师高效应对信号完整性挑战,确保系统在高密度和高性能环境下稳定运行。通过使用Cadence-Sigrity工具,设计师可以更精确地分析和优化内存系统,从而提升整体设计的质量和可靠性。

2019-05-23 上传

2024-09-11 上传

2016-01-17 上传

2021-05-07 上传

2022-05-20 上传

2021-01-27 上传

2019-09-24 上传

点击了解资源详情

点击了解资源详情

dimmi

- 粉丝: 4

- 资源: 7

最新资源

- 创建个性化的Discord聊天机器人教程

- RequireJS实现单页应用延迟加载模块示例教程

- 基于Java+Applet的聊天系统毕业设计项目

- 从HTML到JSX的转换实战教程

- 轻量级滚动到顶部按钮插件-无广告体验

- 探索皇帝多云的天空:MMP 100网站深度解析

- 掌握JavaScript构造函数与原型链的实战应用

- 用香草JS和测试优先方法开发的剪刀石头布游戏

- SensorTagTool: 实现TI SensorTags数据获取的OS X命令行工具

- Vue模块构建与安装教程

- JavaWeb图片浏览小程序毕业设计教程

- 解决 Browserify require与browserify-shim冲突的方法

- Ventuno外卖下载器扩展程序使用体验

- IIT孟买医院模拟申请webapp功能介绍

- 掌握Create React App: 开发Tic-Tac-Toe游戏

- 实现顺序编程与异步操作的wait.for在HarmonyOS2及JavaScript中