CMOS数控振荡器在数字锁相环DPLL中的设计与应用

117 浏览量

更新于2024-08-30

收藏 515KB PDF 举报

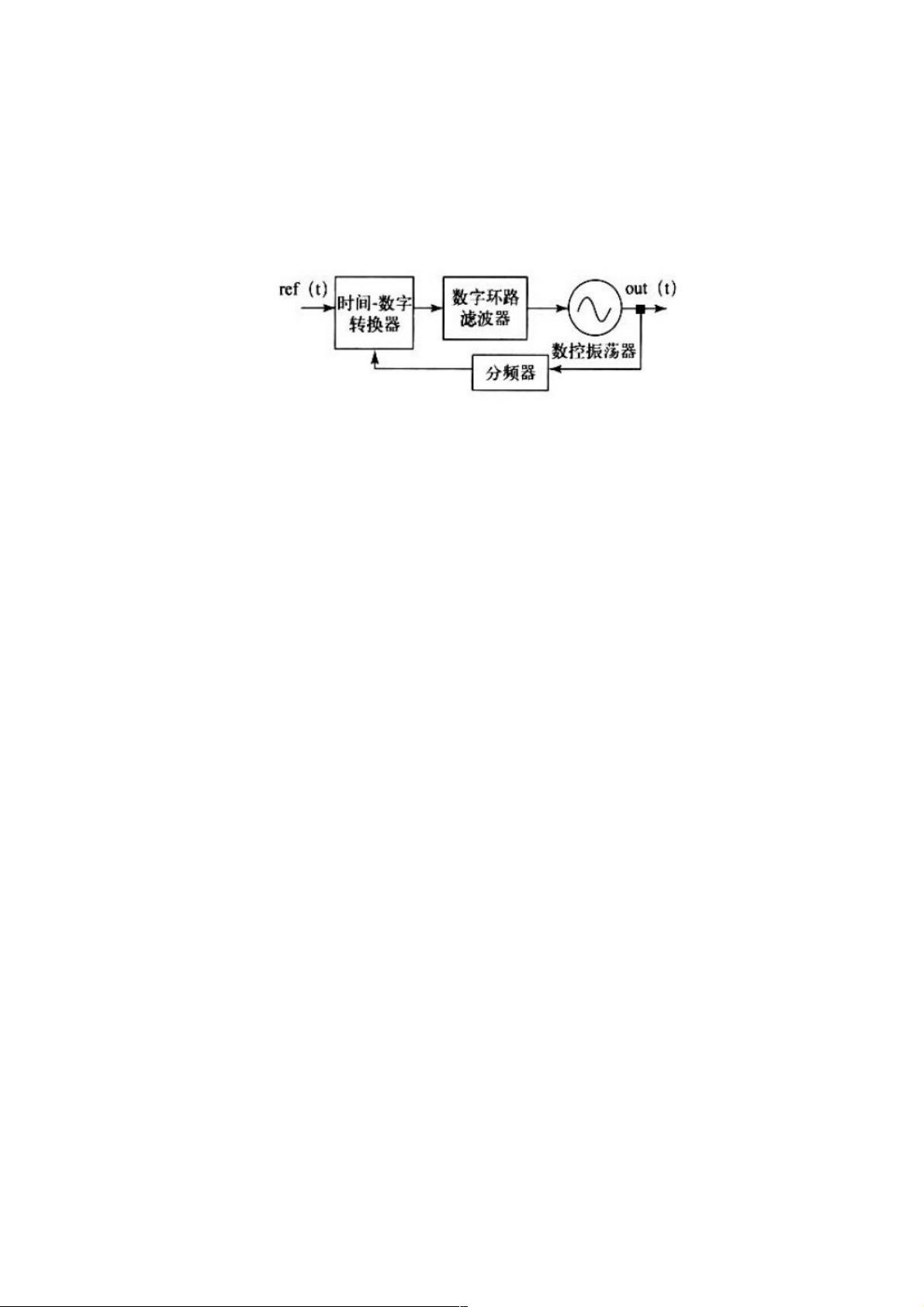

"CMOS数控振荡器设计用于数字锁相环DPLL,常见于高性能数字电路如DSP和微处理器。数字锁相环相对于模拟锁相环,具有更少的非线性器件,更适合高速数字逻辑电路。"

本文将详细讨论CMOS数控振荡器在数字锁相环(DPLL)中的设计与应用。DPLL是现代集成电路中的关键组件,特别是在数字信号处理器和微处理器中,它提供精确的时钟同步和频率控制。

1. 数字锁相环(DPLL)简介:

DPLL是一种能够自动调整系统时钟与参考信号之间的相位关系的电路,常用于频率合成、时钟恢复和信号同步。与模拟锁相环相比,DPLL利用数字信号处理技术,减少了对高阻值电阻、电容和电感的依赖,使得设计更简化,同时提高了系统的稳定性和集成度。

2. CMOS数控振荡器(DCO)设计:

DCO是DPLL的核心部分,其频率直接由输入的数字控制字决定。在本文设计中,DCO采用多级环形振荡器结构,每个级由5个CMOS反相器串联组成,形成闭环负反馈。根据巴克豪森准则,确保了振荡条件的满足。反相器数量(n)和其延迟(tr、tf)决定了振荡频率。为了优化性能,反相器的PMOS和NMOS管的宽度和长度被精心设计,以确保tr=tf,从而产生对称的波形,提高抗噪声能力。

3. 工艺参数与性能优化:

在90nm工艺下,MOSFET的沟道长度设为0.1μm,PMOS管的宽度是NMOS管的两倍,以平衡反相器中的电阻,达到Rn=Rp。这样做的好处是减小了上升和下降沿的不匹配,增强了振荡器的稳定性。

4. 抗噪声性能:

通过对称波形的设计,DCO能够抵抗噪声干扰,提高整体系统的信噪比。在高速数字系统中,这种优化的振荡器设计至关重要,因为它直接影响到整个系统的精度和可靠性。

5. 应用场景:

DPLL与DCO的组合在各种应用中发挥着重要作用,例如通信系统中的频率合成、数据传输中的时钟恢复,以及高性能计算平台中的时钟管理。它们为系统提供了灵活的频率调整和精确的时间同步,提升了系统的整体性能。

CMOS数控振荡器在数字锁相环中的设计是一项关键技术,通过优化电路结构和参数,实现了高效、稳定的频率生成,适应了数字信号处理领域对高速、低噪声时钟源的需求。

218 浏览量

2021-05-29 上传

点击了解资源详情

263 浏览量

147 浏览量

447 浏览量

2021-07-26 上传

2021-05-09 上传

2023-07-09 上传

weixin_38747818

- 粉丝: 9

最新资源

- 掌握PerfView:高效配置.NET程序性能数据

- SQL2000与Delphi结合的超市管理系统设计

- 冲压模具设计的高效拉伸计算器软件介绍

- jQuery文字图片滚动插件:单行多行及按钮控制

- 最新C++参考手册:包含C++11标准新增内容

- 实现Android嵌套倒计时及活动启动教程

- TMS320F2837xD DSP技术手册详解

- 嵌入式系统实验入门:掌握VxWorks及通信程序设计

- Magento支付宝接口使用教程

- GOIT MARKUP HW-06 项目文件综述

- 全面掌握JBossESB组件与配置教程

- 古风水墨风艾灸养生响应式网站模板

- 讯飞SDK中的音频增益调整方法与实践

- 银联加密解密工具集 - Des算法与Bitmap查看器

- 全面解读OA系统源码中的权限管理与人员管理技术

- PHP HTTP扩展1.7.0版本发布,支持PHP5.3环境