FPGA实现线性FIR滤波器设计与优化

版权申诉

2 浏览量

更新于2024-07-02

收藏 1.96MB DOC 举报

"基于FPGA实现线性FIR数字滤波器的设计与应用"

在现代通信系统和信号处理中,FIR(Finite Impulse Response,有限冲击响应)数字滤波器扮演着至关重要的角色,尤其在宽带信号处理领域。本文探讨的是如何在FPGA(Field-Programmable Gate Array,现场可编程门阵列)平台上实现线性FIR数字滤波器,以满足实时、高效和灵活的需求。

1.1 课题背景

随着无线通信和雷达技术的快速发展,对信号的频谱分析精度和实时性提出了更高的要求。FIR滤波器因其线性相位特性、良好的稳定性和设计灵活性,成为理想的选择。FPGA因其可重构性,能快速适应不同滤波需求,因此成为实现FIR滤波器的优选平台。

1.2 课题研究的目的和意义

本研究旨在提高FPGA实现FIR滤波器的效率,通过优化算法和硬件结构,降低资源消耗,同时保持高速运行能力。这有助于提升信号处理系统的整体性能,应用于各种实时信号处理系统,如通信接收机、雷达信号处理等。

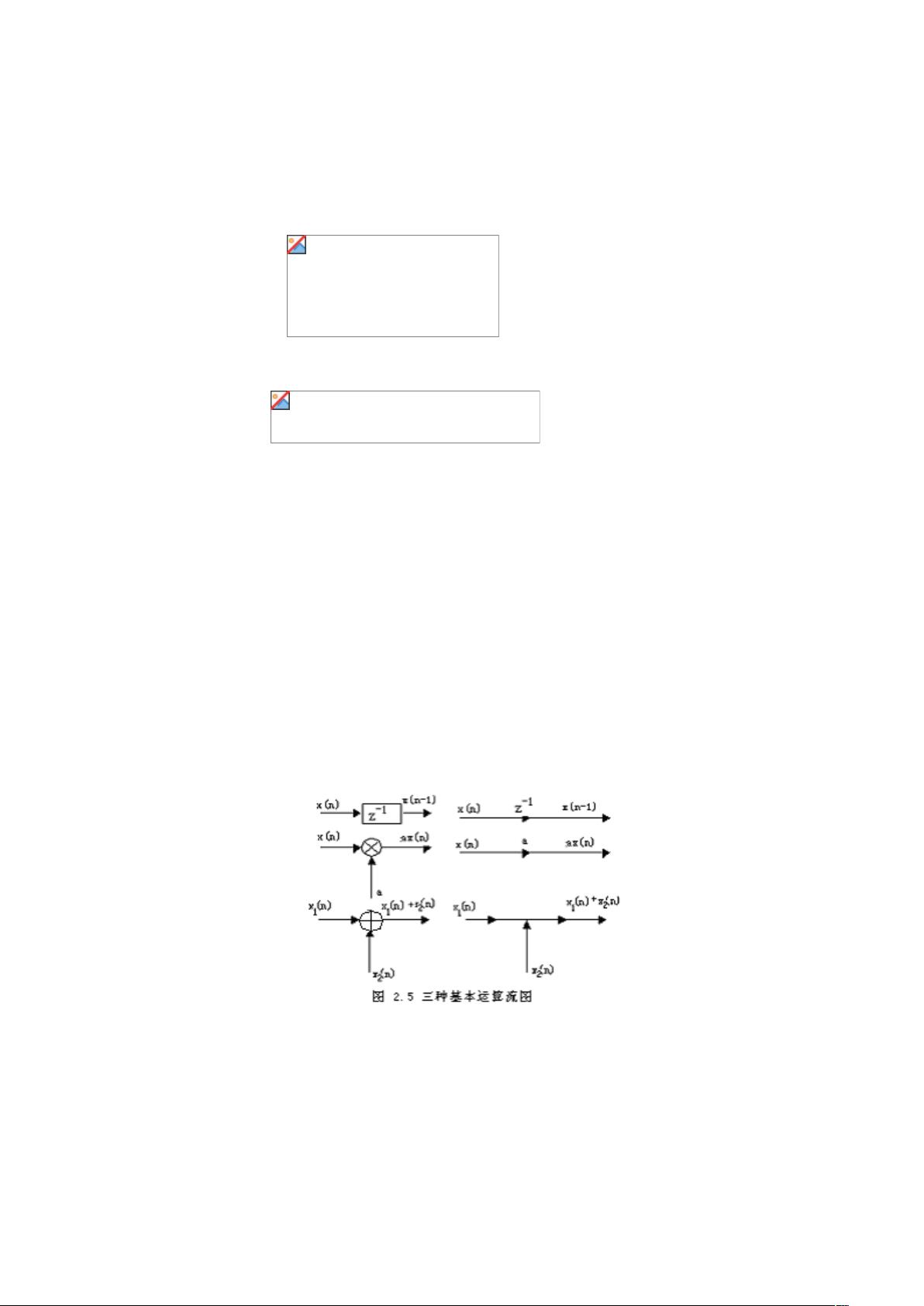

2.1 滤波器的基本概念

滤波器主要用于去除信号中的噪声或提取特定频率成分。滤波原理基于傅立叶变换,通过对信号进行频域分析来实现频率选择性。

2.1.2 滤波器的分类

滤波器主要分为两大类:IIR(无限冲击响应)和FIR。FIR滤波器因其线性相位特性、无环路延迟以及易于设计成任意频率响应而被广泛采用。

2.2.1 FIR滤波器的特点

FIR滤波器的输出仅取决于当前及之前输入序列的值,没有反馈路径,因此其稳定性好,且容易实现线性相位特性。

3. FIR数字滤波器的设计思路

设计FIR滤波器时,通常采用窗口法、频率采样法或等效脉冲响应法。本文重点在于FPGA上的实现,因此采用分布式算法,利用FPGA的并行处理能力,将乘加运算转化为查找表结构,以减小存储需求。

4. FPGA实现的关键技术

4.1 查找表(LUT,Lookup Table)实现乘法器

查找表是一种高效的硬件实现乘法的方法,通过预计算并存储乘法结果,可以快速完成乘法运算,减少FPGA资源的占用。

4.2 分布式算法

分布式算法允许滤波器系数分布在多个逻辑单元中,同时处理多个输入样本,从而提高运算速度。

4.3 流水线技术

通过多级流水线设计,FIR滤波器的各个阶段可以在不同的时钟周期内独立完成,极大地提升了运算吞吐量,而不影响系统的总体运行速度。

5. VHDL编程

使用VHDL硬件描述语言,可以精确描述FIR滤波器的逻辑结构,便于FPGA的综合和实现。

总结,基于FPGA的线性FIR数字滤波器设计是信号处理领域的重要研究课题,通过优化的算法和硬件结构,实现了高速、低资源消耗的滤波器,这对于实时信号处理系统具有重大意义。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-09-18 上传

2023-06-20 上传

2023-06-20 上传

2021-10-05 上传

2021-10-04 上传

2021-10-04 上传

智慧安全方案

- 粉丝: 3814

- 资源: 59万+

最新资源

- 全国江河水系图层shp文件包下载

- 点云二值化测试数据集的详细解读

- JDiskCat:跨平台开源磁盘目录工具

- 加密FS模块:实现动态文件加密的Node.js包

- 宠物小精灵记忆配对游戏:强化你的命名记忆

- React入门教程:创建React应用与脚本使用指南

- Linux和Unix文件标记解决方案:贝岭的matlab代码

- Unity射击游戏UI套件:支持C#与多种屏幕布局

- MapboxGL Draw自定义模式:高效切割多边形方法

- C语言课程设计:计算机程序编辑语言的应用与优势

- 吴恩达课程手写实现Python优化器和网络模型

- PFT_2019项目:ft_printf测试器的新版测试规范

- MySQL数据库备份Shell脚本使用指南

- Ohbug扩展实现屏幕录像功能

- Ember CLI 插件:ember-cli-i18n-lazy-lookup 实现高效国际化

- Wireshark网络调试工具:中文支持的网口发包与分析