UVM分析端口与分析导出:一对一与一对多的区别与应用

在UVM (Universal Verification Methodology) 中,analysis port 和 analysis export 是两个重要的概念,它们与常规的port 和 export 功能有所不同。UVM 是一种广泛应用于硬件验证的工具,用于系统级和组件级的测试。这两个特性在处理transaction 时展现了一种不同的通信模式。

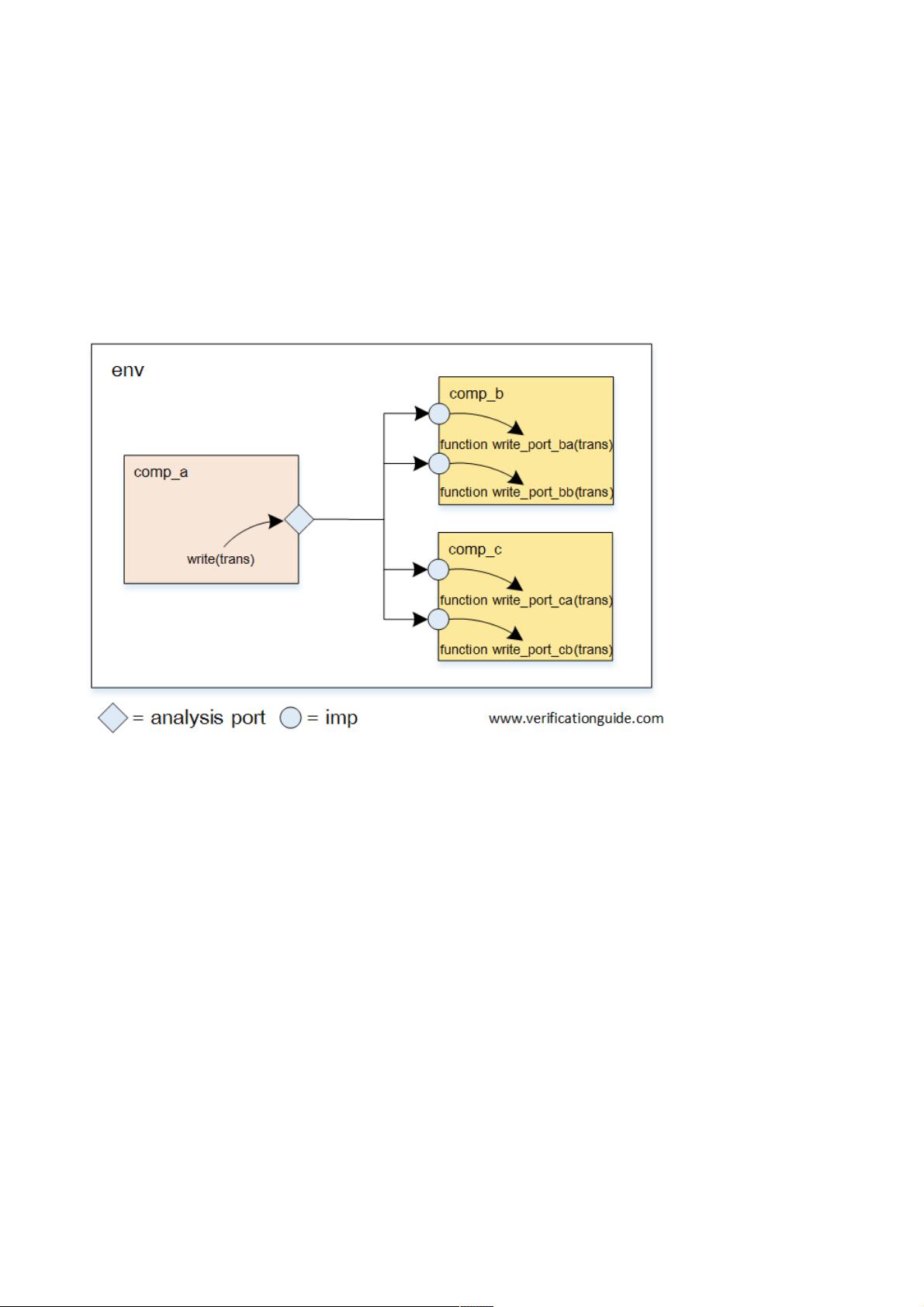

首先,让我们来看看它们的区别。分析端口(analysis port)和分析导出(analysis export)都是用来传输交易数据,但它们的通信模型有所差异。analysis port 实现的是一对多(one-to-many)的通信,这意味着一个分析端口可以同时与多个接口模块(IMP,Interface Model Port)连接,通过写入操作(write)将数据广播出去。这种方式简化了设计,因为分析端口无需关心接收方的响应,它自己完成发送后即认为任务完成,无需等待确认。这与普通port 和 export 的一对一(one-to-one)通信模式不同,后者可能需要进行put、get 或 transport 操作,并且有阻塞和非阻塞的区分。

相比之下,普通port 分为 put_port、get_port 和 transport_port,它们各自负责数据的输入、输出或传输,而且每个port 只能执行单一类型的操作,不能同时处理多个功能。此外,put、get 和 transport 操作支持阻塞和非阻塞模式,这在处理数据流时提供了灵活性。

在代码示例中,如 class component_a,它扩展自uvm_component 并定义了一个名为analysis_port_a 的分析端口,用于传输transaction 类型的数据。在构造函数中,先声明分析端口并创建实例,然后在组件的上下文中使用。这种设计使得component_a 能够方便地与多个IMP 进行数据共享和同步,而无需关注每个IMP 的响应细节。

analysis port 和 analysis export 在UVM 中提供了一种高效、简洁的通信方式,特别适用于那些需要数据广播或简单数据共享的场景。理解并正确使用这些特性有助于提高验证测试的效率和可维护性。当设计验证环境时,应根据具体需求选择合适的端口类型,以确保系统的有效验证和性能。

196 浏览量

153 浏览量

303 浏览量

137 浏览量

324 浏览量

765 浏览量

点击了解资源详情

点击了解资源详情

324 浏览量

weixin_38666114

- 粉丝: 7

- 资源: 971