华为内部FPGA高级设计技巧:Xilinx篇速效优化策略

需积分: 25 106 浏览量

更新于2024-07-23

收藏 2.98MB PDF 举报

本篇文档深入探讨了FPGA设计的高级技巧,专注于Xilinx平台,特别针对深圳市华为技术有限公司内部分享。文档共62页,详细涵盖了FPGA设计的关键要素和技术细节,旨在帮助设计者提升效率并优化资源利用。

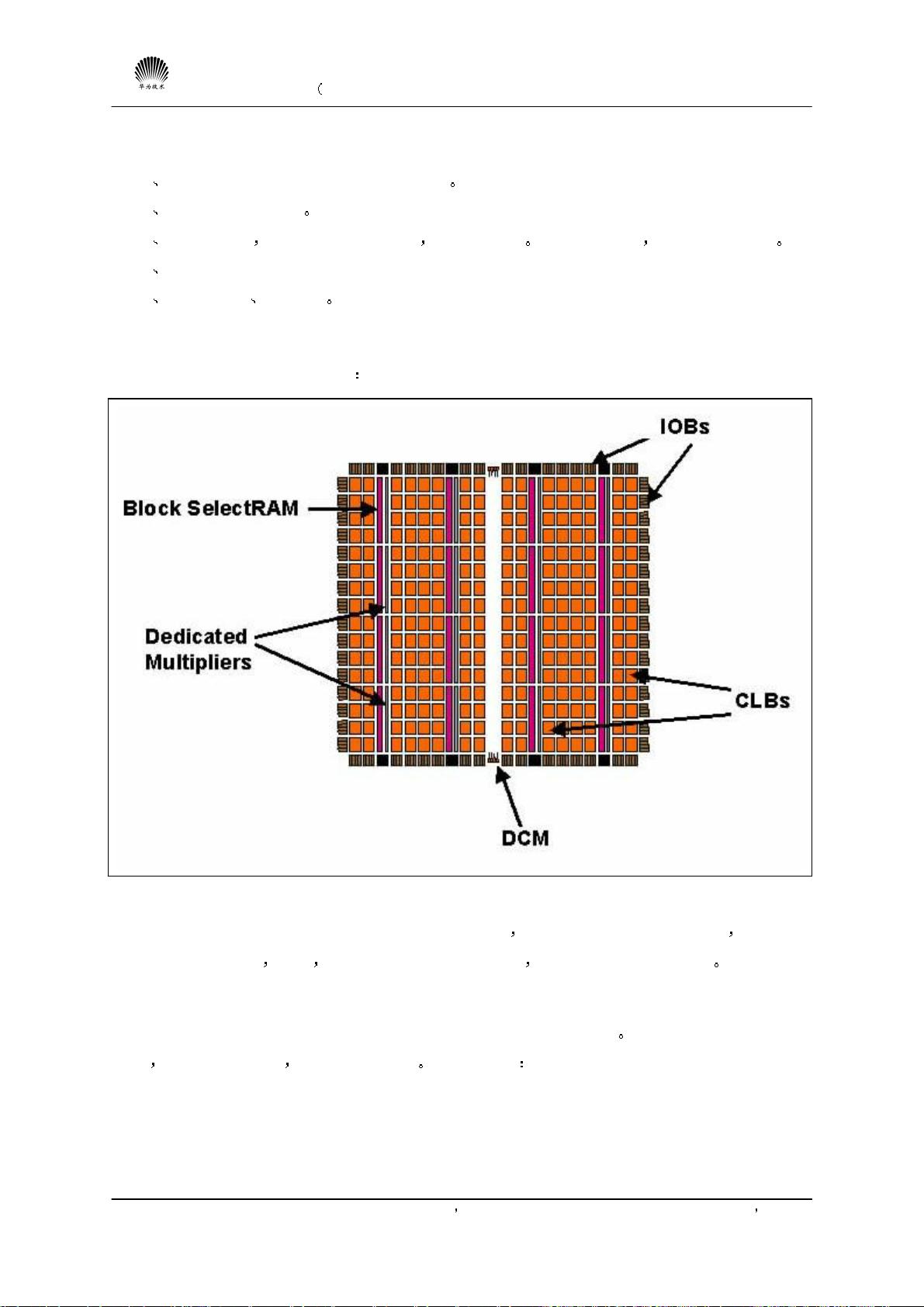

首先,章节3.3至3.3.4部分详细介绍了逻辑单元(LUT)的各种用法,包括LUT作为基本逻辑元件、Slice的使用、SRL(Shift Register LUT)以及MUXFX(Multiplexer Feedback)等,这些都是构建复杂逻辑电路的基础。理解并合理运用这些单元可以有效减少逻辑级数,提高速度并降低资源占用。

在第3.4节中,讨论了内存资源,如Distributed RAM和BlockRAM,以及它们在存储和数据处理中的作用,特别是BlockSelectRAM的内部结构和配置方法,有助于优化数据流处理。

章节3.5和3.6聚焦于I/O接口,包括IOB结构、Select I/O控制、DCI(Data Compression Interface)等,强调了正确配置I/O对于整体系统性能的影响。

3.7章介绍了时钟资源管理,包括GlobalClock、CLKMUX、DCM(Digital Clock Management)、以及全局时钟分配,这些都是保证设计时序完整性和系统稳定性的关键。

4.1至4.3的部分着重于减少关键路径的逻辑级数,通过IF语句、Case语句和优化加法电路结构来改善设计延迟。串行进位与超前进位策略能有效提升设计速度,同时保持逻辑层次清晰。

文档还提到了编码风格对FPGA设计的影响,尤其是在Virtex II架构下,理解ASIC与FPGA的不同结构特性有助于选择合适的编程策略。

本篇文档是华为内部分享的高级FPGA设计技巧,涵盖了从基本逻辑元素到高级资源管理和时钟控制的全方位内容,适合有经验的FPGA设计师深入学习和实践。

198 浏览量

147 浏览量

155 浏览量

点击了解资源详情

108 浏览量

122 浏览量

guiping1979

- 粉丝: 0

- 资源: 3

最新资源

- STM32F103 4路超声波

- Plot Superquadratic Surfaces:这是一对用于绘制一般超椭圆体和超环面的函数-matlab开发

- JQueryRevision

- flat-view

- 行业分类-设备装置-一种接枝SiOsub2sub粒子簇取向增强涤纶纤维的制备方法.zip

- grpc_stream-medium

- 移远调试+升级工具包.rar

- LiterateTest.jl

- 行业分类-设备装置-一种接触式密封倒置型气波制冷机.zip

- next-redux-toolkit-auth

- 6ES7215-1AG40-0XB0_V04.04.00.zip

- sentry-heroku:在 heroku 上快速简单地设置哨兵 7 服务器

- ptwaters87.github.io:项目网站

- 卡斯巴赫特

- 行业分类-设备装置-一种接触冷感性聚酯纤维织物.zip

- pycocotools.zip