QuartusII驱动的模块化数字钟设计与实现

需积分: 32 83 浏览量

更新于2024-07-22

收藏 883KB DOC 举报

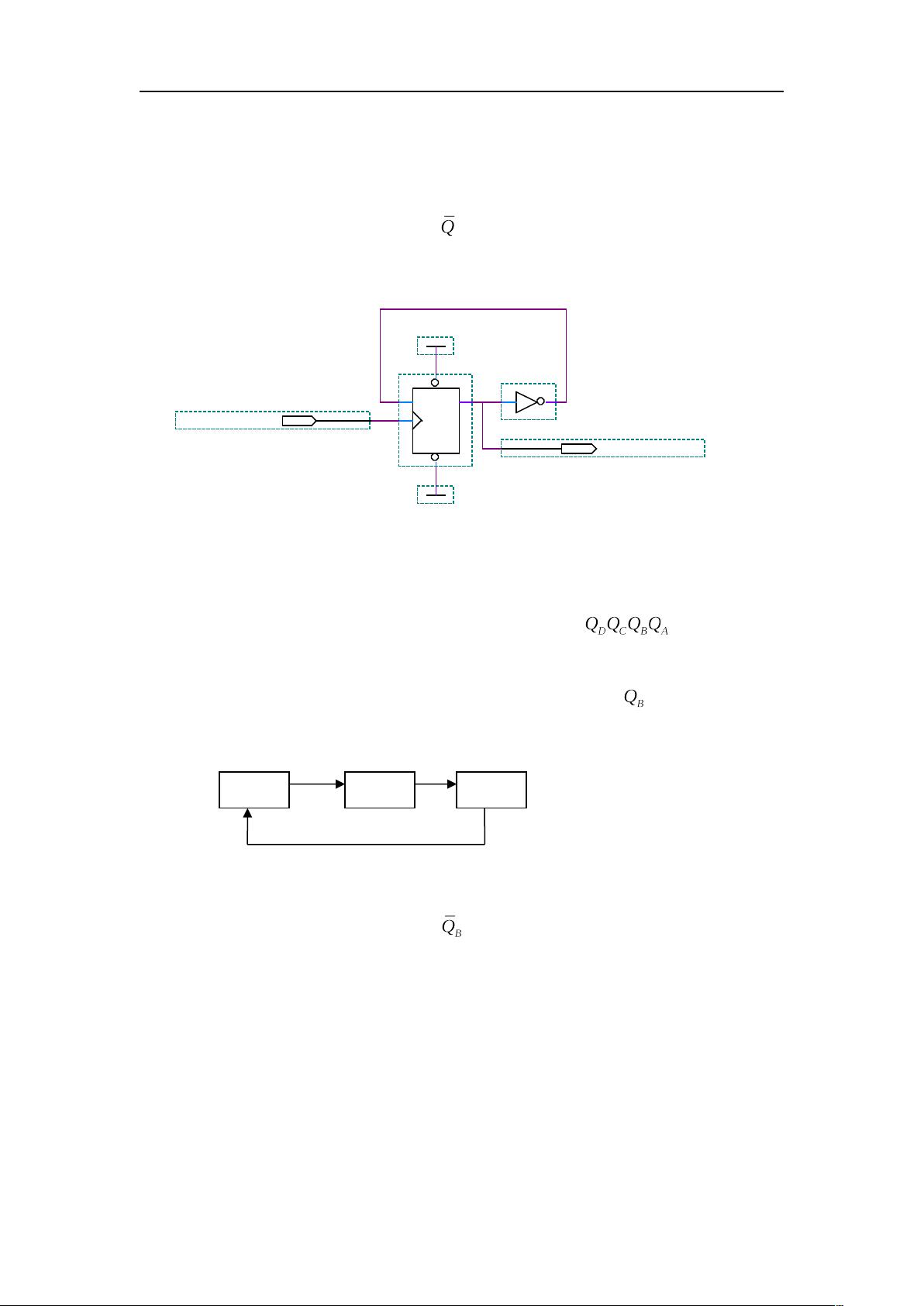

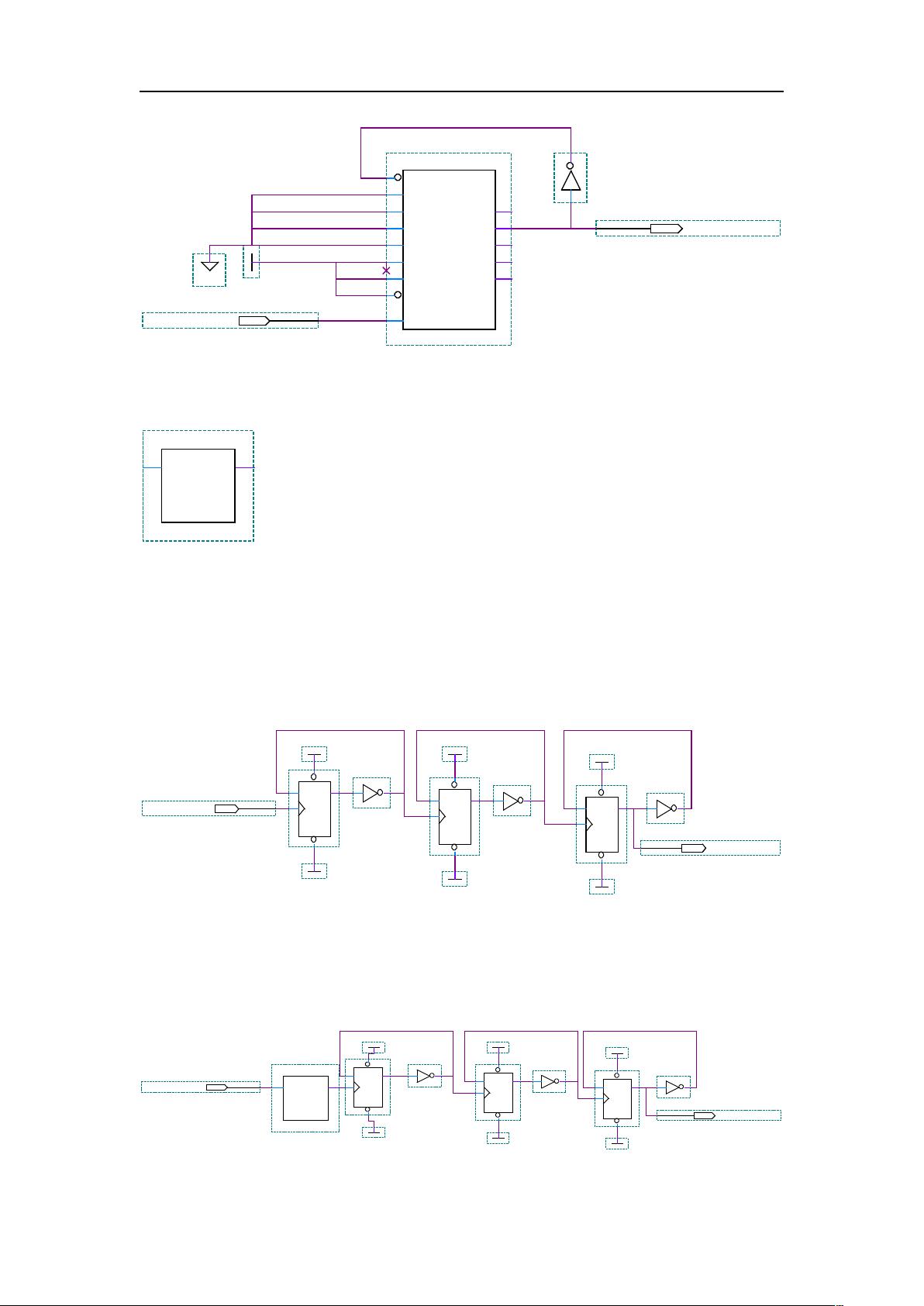

本文档详细介绍了如何利用QuartusII软件平台进行一款功能丰富的多功能数字钟的设计过程。首先,作者强调了使用QuartusII这款强大的集成开发环境(IDE),因为它支持理论图(原理图)输入设计,这与传统的VHDL语言相比,提供了更为直观和易于理解的设计方式。设计的核心目标是采用模块化设计原则,将整个数字钟的功能分解为多个独立的子模块,以便于管理和优化。

设计流程包括以下几个关键部分:

1. 设计内容简介:

文章首先概述了设计的目标,即构建一个具备多种功能的数字钟,如时间显示、定时器、报时、闹钟设置以及音乐播放等。这种多功能性使得设计更具实用性。

2. 设计要求:

设计要求可能涵盖了精度、稳定性、功耗控制以及用户界面友好度等方面,确保数字钟在满足基本时间显示的同时,还能提供其他实用特性。

3. 方案论证:

整体电路设计遵循模块化思想,通过合理布局和组件选择,使每个子模块如脉冲产生电路、计时电路、显示电路等都能独立工作,同时又能协同完成整个系统的功能。

- 脉冲产生电路:负责生成稳定的时钟信号,作为整个系统的基准。

- 计时电路:精确测量和计算时间间隔,实现定时和计数功能。

- 显示电路:清晰地显示小时、分钟和秒数,可能还包括日期等信息。

- 保持电路:确保在电源中断时能保持计时状态。

- 清零电路:用于复位计数器或清除显示。

- 校分电路:处理小时和分钟的转换。

- 校时电路:允许用户手动调整时间。

- 整点报时电路:在整点时触发响铃或播报时间。

- 闹钟设定电路:设置特定时间的提醒功能。

- 音乐产生电路:播放预先存储的音乐片段,增强用户体验。

4. 软件仿真与硬件测试:

在完成所有子模块设计后,软件仿真至关重要,确保逻辑正确无误。然后将设计编译并下载到可编程实验系统SmartSOPC中,进行硬件测试,验证实际运行效果。

通过这个设计,作者不仅展示了软件在硬件设计中的重要性,还让读者理解了模块化设计方法在复杂系统中的优势,提升了设计的灵活性和可维护性。此外,文档还强调了硬件设计软件化的理念,即利用高级软件工具简化硬件设计流程,提高设计效率。

1770 浏览量

157 浏览量

523 浏览量

306 浏览量

4714 浏览量

275 浏览量

2021-09-29 上传

139 浏览量

2021-10-12 上传

tommytao12345

- 粉丝: 0

- 资源: 1

最新资源

- 企业信息化建设

- 自我卡萨

- react-native

- Project-2:我们的第一个全栈应用程序!

- zxing-android-eclipse-lib

- docker-elixir:Elixir的官方Docker映像

- GameOfLife:“生活游戏”的全HTML(和JavaScript)实现

- PVP-HUB-ESPADA:Reinos-Hispanos 官方插件 || 该插件包括给你一把铁剑,FULL DIAMOND,它可以让你在HUB(大厅)中战斗

- 企业信息化

- NextJS_with_MongoDB

- discord-bot-playercount:一个不和谐的机器人,可以在不和谐状态下不断显示游戏的玩家人数

- NutnetAPI

- Data-Structures-in-Real-Life-Projects

- 中小学信息技术教育的现状与发展

- seoml

- Python-Data-Journalism:适用于数据记者工具系列的Jupyter笔记本