时序逻辑电路解析:同步计数器设计与分析

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

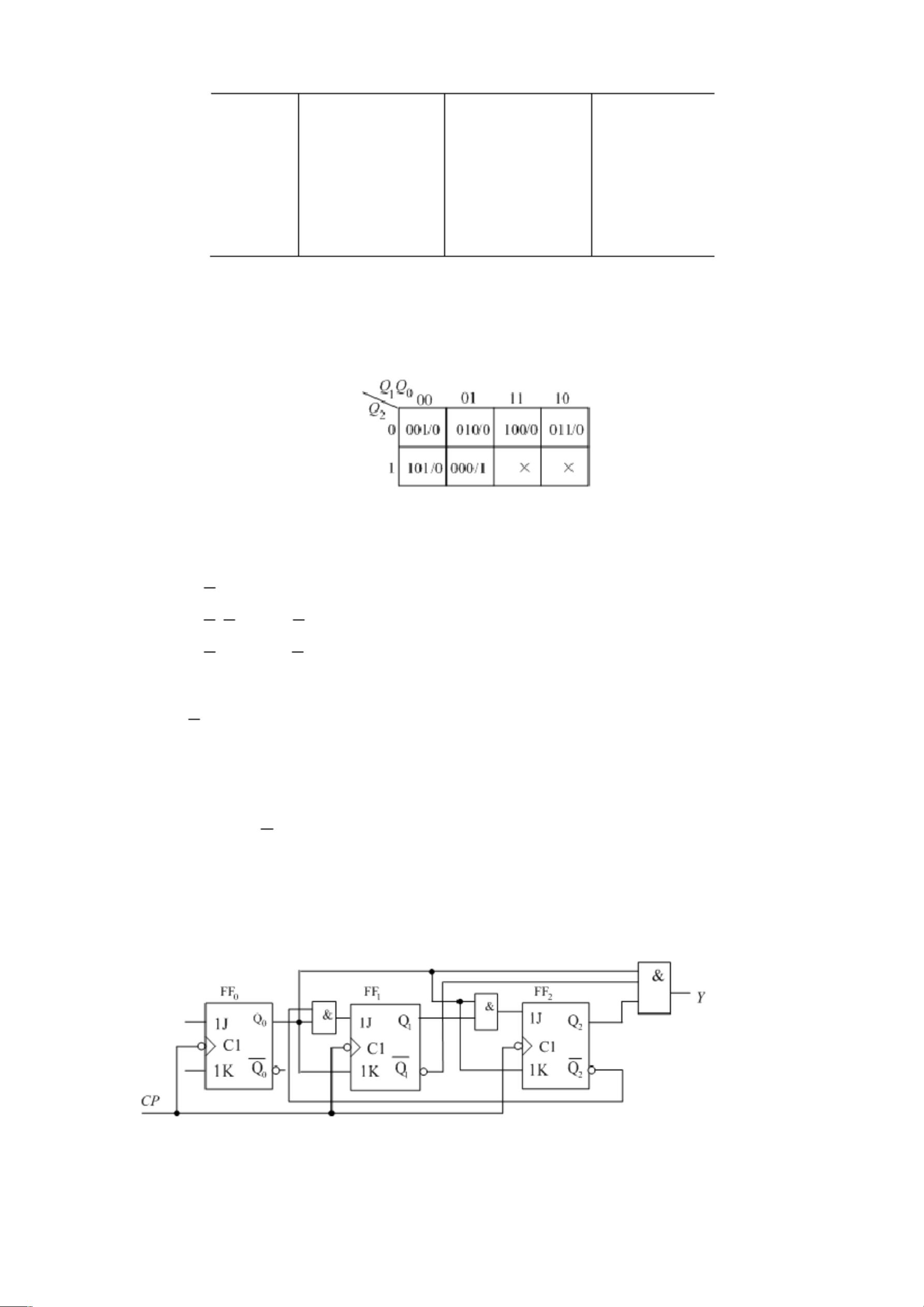

"数电习题及答案.docx" 本文主要涉及数字电子技术中的时序逻辑电路相关知识,包括其基本概念、分类、描述方法以及设计实例。 时序逻辑电路是一种重要的数字电路类型,与组合逻辑电路不同,它由两部分组成:组合逻辑电路和存储电路(触发器)。组合逻辑电路负责处理输入信号并生成输出,而存储电路则用于保存电路的状态。这种电路的特点在于其输出不仅取决于当前的输入,还依赖于电路的前一状态。 同步时序逻辑电路是其中一类,它的所有触发器由同一个时钟脉冲控制,这类电路的描述通常包括三组方程:驱动方程(定义触发器的输入)、状态方程(描述状态如何随时间变化)和输出方程(给出电路的输出与状态和输入的关系)。异步时序逻辑电路则没有统一的时钟,状态转换可能由多个独立的时钟或边沿触发。 在具体的设计实例中,例如同步五进制计数器的设计,通常会采用D触发器,并通过状态转换图、状态真值表、状态方程和驱动方程来完成。例如,一个同步五进制计数器可能需要3个触发器,通过特定的连接方式使得电路从状态000依次计数到100,形成五进制计数序列。 此外,电路的自启动性也是一个关键特性,这意味着电路在没有初始条件的情况下,能够从某个特定状态开始工作。例如,一个五进制加法计数器如果能从任意状态开始计数,则具有自启动性。 在分析时序电路的逻辑功能时,我们需要写出电路的驱动方程(定义触发器的输入)、状态方程(描述状态的更新规则)和输出方程(确定输出与状态和输入的关系),并绘制状态转换图以直观地表示状态之间的转换路径。例如,一个可控3进制计数器,其驱动方程、状态方程和输出方程将决定电路如何响应输入信号X来改变状态和产生输出。 时序逻辑电路是数字系统的基础模块,它们在计算机、通信设备和其他数字系统中广泛应用,理解和设计这类电路对于深入理解数字电子技术至关重要。通过解决习题和理解实例,可以巩固这些概念,并提高实际问题解决能力。

剩余36页未读,继续阅读

- 粉丝: 6686

- 资源: 3万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- C++多态实现机制详解:虚函数与早期绑定

- Java多线程与异常处理详解

- 校园导游系统:无向图实现最短路径探索

- SQL2005彻底删除指南:避免重装失败

- GTD时间管理法:提升效率与组织生活的关键

- Python进制转换全攻略:从10进制到16进制

- 商丘物流业区位优势探究:发展战略与机遇

- C语言实训:简单计算器程序设计

- Oracle SQL命令大全:用户管理、权限操作与查询

- Struts2配置详解与示例

- C#编程规范与最佳实践

- C语言面试常见问题解析

- 超声波测距技术详解:电路与程序设计

- 反激开关电源设计:UC3844与TL431优化稳压

- Cisco路由器配置全攻略

- SQLServer 2005 CTE递归教程:创建员工层级结构

信息提交成功

信息提交成功