高速数字设计实战:典型案例解析与信号完整性指南

需积分: 10 61 浏览量

更新于2024-07-27

收藏 1.23MB PDF 举报

高速电路设计已经成为现代电子工程领域的重要组成部分,尤其是在航空、雷达、汽车电子、无线通信和有线接入等领域,其技术的发展与应用日益广泛。本文旨在结合理论与实践,通过作者亲身经历的案例,为初入行业的硬件工程师提供实用且具有说服力的指导,避免他们在设计过程中走弯路。

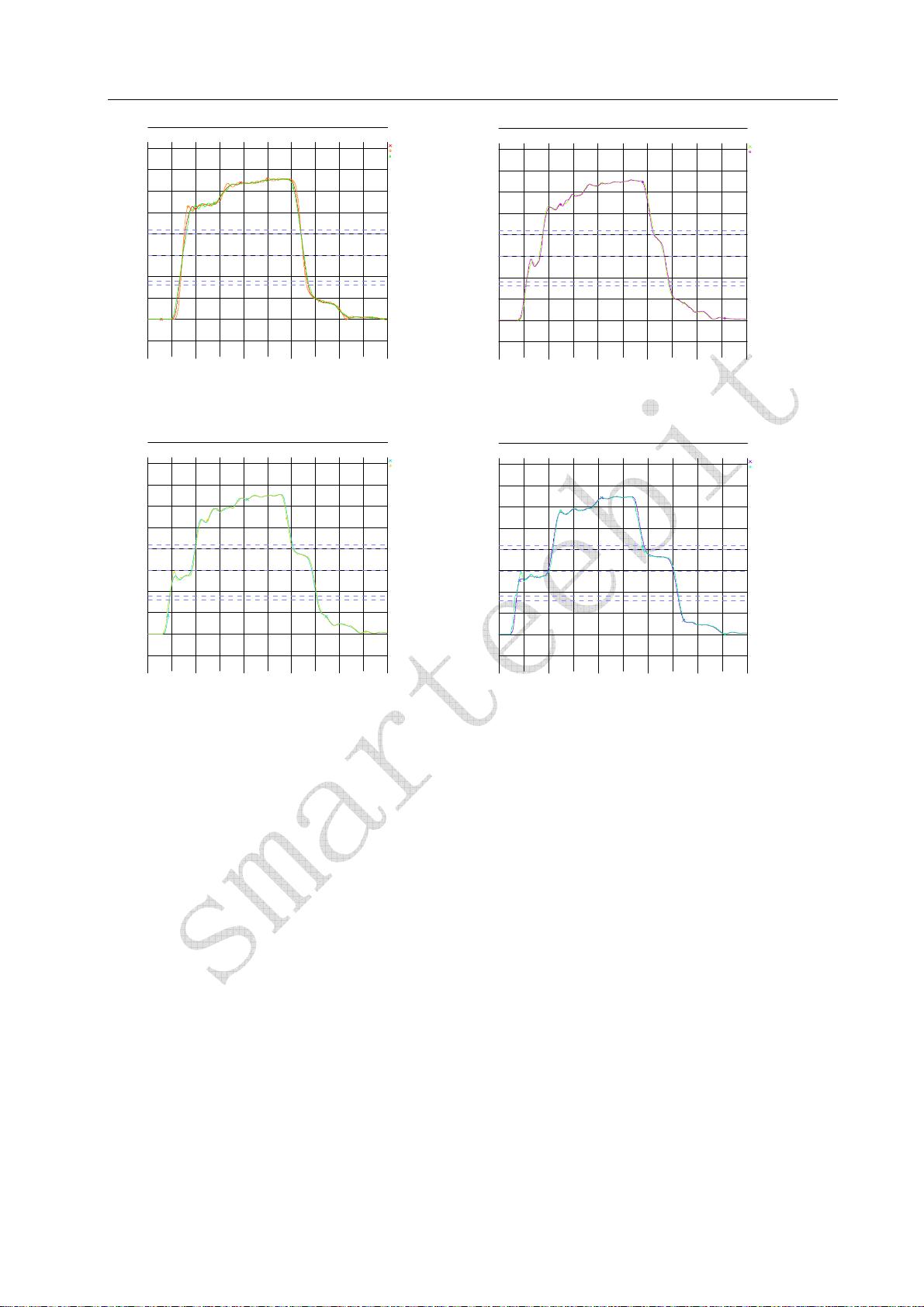

文章首先强调了"信号完整性"在高速数字设计中的核心地位,它是衡量信号在传输过程中质量和可靠性的一个关键指标。信号完整性问题主要表现为过冲、振铃和非单调性。过冲是信号沿长线路传播时常见的问题,如果没有适当的匹配,可能导致信号电平超出接收端器件的阈值,对器件造成潜在损伤,影响其使用寿命和产品稳定性。例如,Altera的CycloneIII系列器件虽然标称的最大正耐压值为3.95V,但在考虑过冲情况下的限制更为严格,设计师必须遵循厂商提供的瞬态过冲参数,确保信号在规定的极限内。

文章通过图表详细解释了如何计算和限制过冲时间,以确保设备在长时间工作中的可靠性和安全性。这涉及到对器件耐久性的理解以及对设计规范的精确执行。对于读者来说,具备基本的高速数字设计理论知识是前提,但本文更侧重于实践经验,帮助工程师掌握解决实际问题的方法。

本文提供了一系列高速电路设计的经典案例,着重讲解了信号完整性和过冲问题的处理策略,是硬件工程师在进行高速数字设计时不可或缺的参考资源。通过阅读和学习,工程师们可以提升自己的技能,减少在复杂设计中遇到的挑战,从而推动产品性能的优化和市场的竞争力。

点击了解资源详情

点击了解资源详情

点击了解资源详情

278 浏览量

122 浏览量

553 浏览量

2012-07-19 上传

点击了解资源详情

289 浏览量

清风瘦竹

- 粉丝: 0

- 资源: 1

最新资源

- cesium js 指北针

- PRIMA-CRM客户关系管理系统源代码

- 数据_扇形FBP_ct数据_扇形CT_giftcja_FBP

- phylopeachtree.github.io:Peachtree-在树上绘制流行病学和对齐字符

- 开课吧 vue面试题训练营

- 易语言超级列表框排序源码,易语言超级列表框排序_增加时间排序源

- Dark Patterns-crx插件

- boxy:使用Phaser 3的演示平台游戏

- staffdashboard

- Textarea Lift-off-crx插件

- TSSOS:基于矩SOS层次结构的稀疏多项式优化工具

- audio-flac:audioflac 包

- wAppbar:Windows桌面应用程序栏(appbar),基于Nim和wNim Framework

- MCQTabbedAppPOC

- Color-Identifying-Game:通过查看红色,绿色和蓝色值来识别颜色

- 易语言超级列表框指定行着色