高速数字电路实践:经典案例与信号完整性分析

需积分: 10 171 浏览量

更新于2024-07-26

收藏 1.24MB PDF 举报

"高速数字电路经典案例,通过实例讲解高速数字设计中的信号完整性问题,适合有一定理论基础的读者。"

本文主要围绕高速数字电路中的关键概念——信号完整性展开讨论,通过对实际案例的分析来帮助硬件工程师理解并解决相关问题。高速数字设计在各个领域广泛应用,如航空、雷达、汽车电子、无线通信等,而信号完整性的理解和处理是确保系统稳定性和可靠性的重要环节。

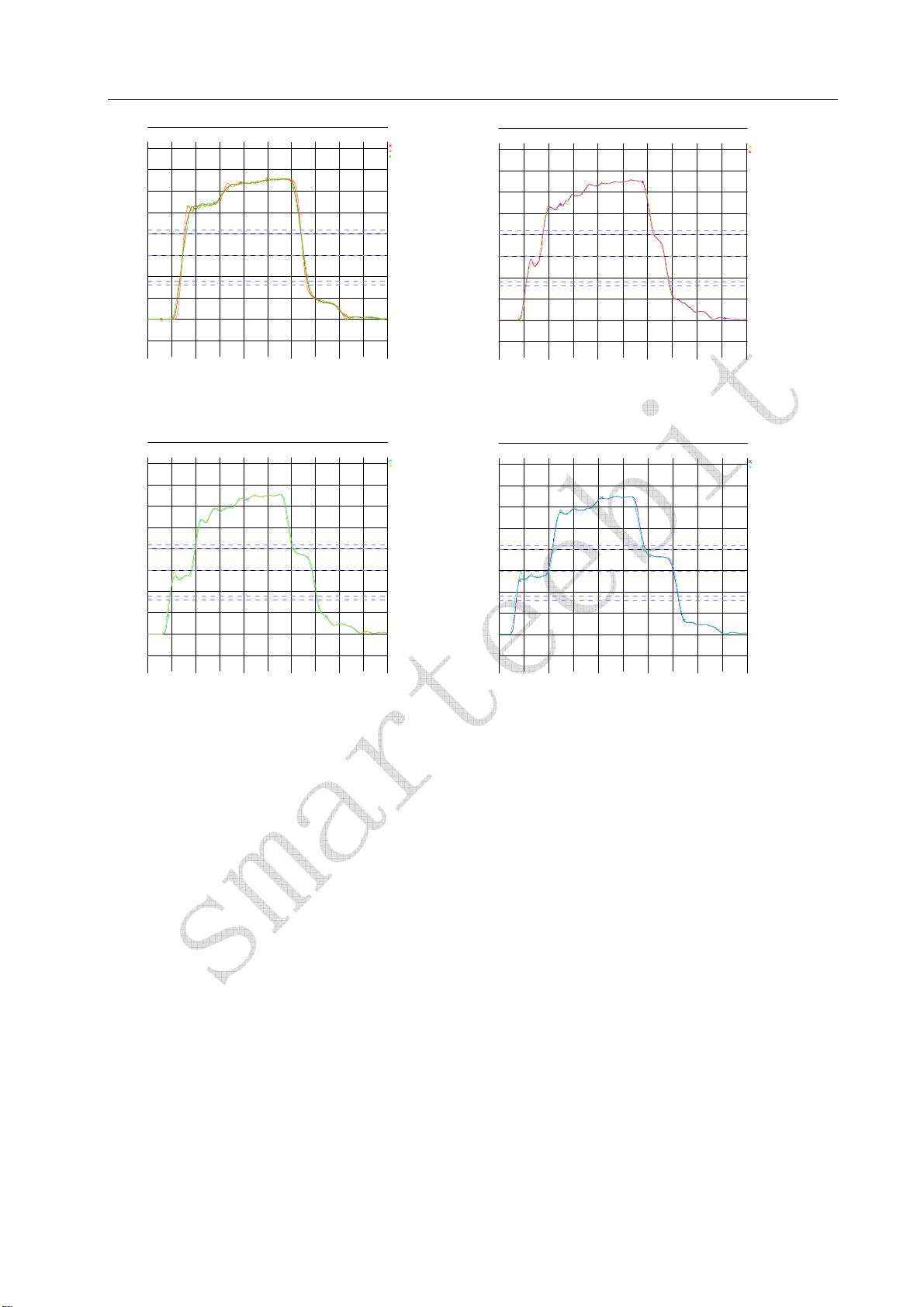

信号完整性问题主要包括过冲(OVERSHOOT)、振铃(RING)和非单调性(NONMONOTONIC)。过冲发生在快速信号驱动长走线时,若无有效匹配,可能导致信号电平超出接收端器件的输入范围,影响器件寿命和产品稳定性。例如,Altera的CycloneIII器件允许一定瞬态过冲,但有严格的参数限制,超出规定时间累积的过冲电压可能会对器件造成损害。

振铃是指信号在上升或下降沿期间产生的高频振荡,可能干扰相邻信号,影响系统的噪声容限。非单调性则是指信号波形在上升或下降过程中出现的不连续或波动,这可能导致错误的数据采样,降低传输效率。

为了解决这些问题,设计者需要考虑以下策略:

1. **阻抗匹配**:通过匹配传输线的特性阻抗,减少反射,降低过冲和振铃的发生。

2. **适当的去耦和电源完整性**:确保足够的电源稳定性,减少电源纹波对信号质量的影响。

3. **使用缓冲器和均衡器**:在必要时,添加缓冲器可以改善信号驱动能力,而均衡器可以补偿通道损耗。

4. **布局布线优化**:合理规划电路板布线,避免长距离直角走线,减少信号传播延迟和辐射。

5. **时序分析**:确保信号在正确的时间到达接收端,避免因时序裕量不足导致的误码。

实际案例分析中,作者会详细探讨如何应用这些方法解决具体问题,帮助读者理解高速数字设计的实际操作和问题解决过程。对于初学者来说,这样的实战经验分享能够弥补理论学习的不足,提供宝贵的实际操作指导。

本文面向有一定高速数字设计基础的读者,通过真实的案例和数据,深入浅出地讲解了信号完整性的重要性及其解决方案,旨在帮助工程师提升在高速数字设计领域的实践技能,避免设计陷阱,提高设计成功率。

2020-07-18 上传

2019-07-31 上传

2013-03-27 上传

2012-07-09 上传

2012-07-19 上传

点击了解资源详情

2011-11-17 上传

点击了解资源详情

点击了解资源详情

abcd326

- 粉丝: 0

- 资源: 7

最新资源

- 硬盘高级维修技巧硬盘维修整理资料汇总

- Foundations Of Qt Development (英文/PDF)

- 让你的ADSL开机自动拨号

- 软件开发项目计划(实践)

- C#设计模式(word文档)

- flex事件机制详解

- text_porcess_in_python

- data mining and KDD: promise and challenges

- flex cookbook中文

- 事业单位考试绝密资料

- AJAX开发框架GWT

- Serial Port Complete-COM Ports, USB Virtual COM Ports, and Ports for Embedded Systems, 2nd Edition.pdf

- java 的面试试题

- 埃特梅尔AT89S52 单片机 参数资料

- § 1.2 Java的 特 点

- 线性代数(同济四版)习题答案