11th international Workshop on Compact Modeling 19

An Analytic Model for Nanowire Tunnel-FETs

Ying Liu

1

, Jin He

1,*

Mansun Chan

2

, Caixia Du

3

, Yun Ye

1

, Wei Zhao

1

, Wen Wu

1

, and Wenping Wang

1

1

Peking University Shenzhen SOC Key Laboratory, PKU-HKUST Shenzhen-Hong Kong Institution, Shenzhen, China

2

Department of Electronic and Computer Engineering, Hong Kong University of Science and Technology, Kowloon, Hong Kong

3

Shenzhen Huayue Teracale Chip Electronic Limited Co., Shenzhen, China

Abstract

—

In this paper, an analytical model of the

gate-all-around (GAA) silicon nanowire tunnel-FETs

(NW-TFETs) is proposed based on the surface potential

solutions at the channel direction and considering band to band

tunneling (BTBT) efficiency. The 3-D Poisson’s equation is

solved to obtain the surface potential distribution in the partition

regions along the channel direction for NW-TFET device and

then a tunneling current model using Kane’s expression is

developed. The validity of the developed model is proved by the

good agreement between the model predictions and TCAD

simulation results.

Keywords — Gate-All-Around (GAA); nanowire tunnel-FETs

(NW-TFETs); band to band tunneling (BTBT); analytic model.

I. INTRODUCTION

unnel-FETs (TFET) has been got great attention in the

semiconductor academic and industry fields in recent

years for the superior performance in sub-threshold region.

Compared with the conventional MOSFETs, TFET is

competitive and chosen due to its high ON-OFF current ratio,

below 60 mV/dec sub-threshold swing (SS) and low leakage

power consumption [1]. However, TFETs have a small

amount of band to band tunneling (BTBT) efficiency in the

large band gap of silicon body leading to a low ON-current.

To obtain the high ON-current and small SS, the GAA

NW-TFETs are considered as an efficient device candidate. In

recent several years, NW-TFET process technology and

fabrication measures have been matured, many research

papers have been published so far [6]-[8]. However, the

compact model of NW-TFET for circuit performance

prediction and simulation has made a few progress,Most

works only focus on NW-TFET empirical model development

[6],[9],[12]]. So far, there is no a complete analytical model of

GAA NW-TFET for device scientists and circuit designers to

test and simulation such a device based circuit performance.

In this paper, an analytical model of GAA silicon

NW-TFETs has been developed based on the

three-dimensional (3-D) potential solution and the Kane’s

expression. For the purpose of observing the validity of the

model and the different structure parameter impact on the

device performance, we have also compared the analytical

model prediction with the TCAD SenTaurus simulation

results of the device to verify the model validity.

II. STRUCTURE AND MODEL

A. Structure of GAA NW-TFET

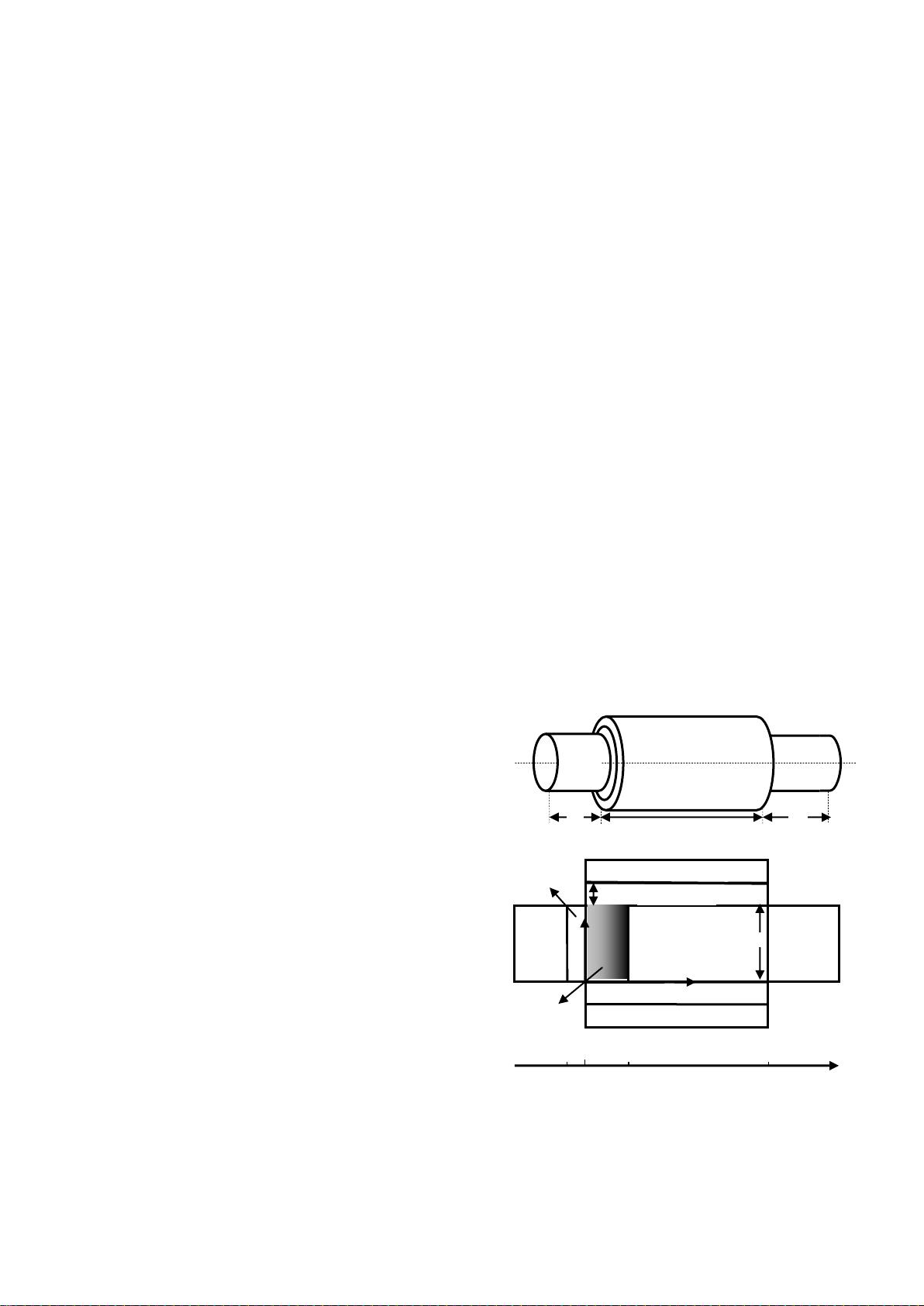

The Fig.1 shows the structure of GAA TFET with silicon

nanowire body. As is shown in Fig.1.(a), the source

electrode length is

(10nm), the drain electrode length

is

(10nm), the gate electrode length is

(50nm), the

oxide (

) thickness is

and the channel radium is

.

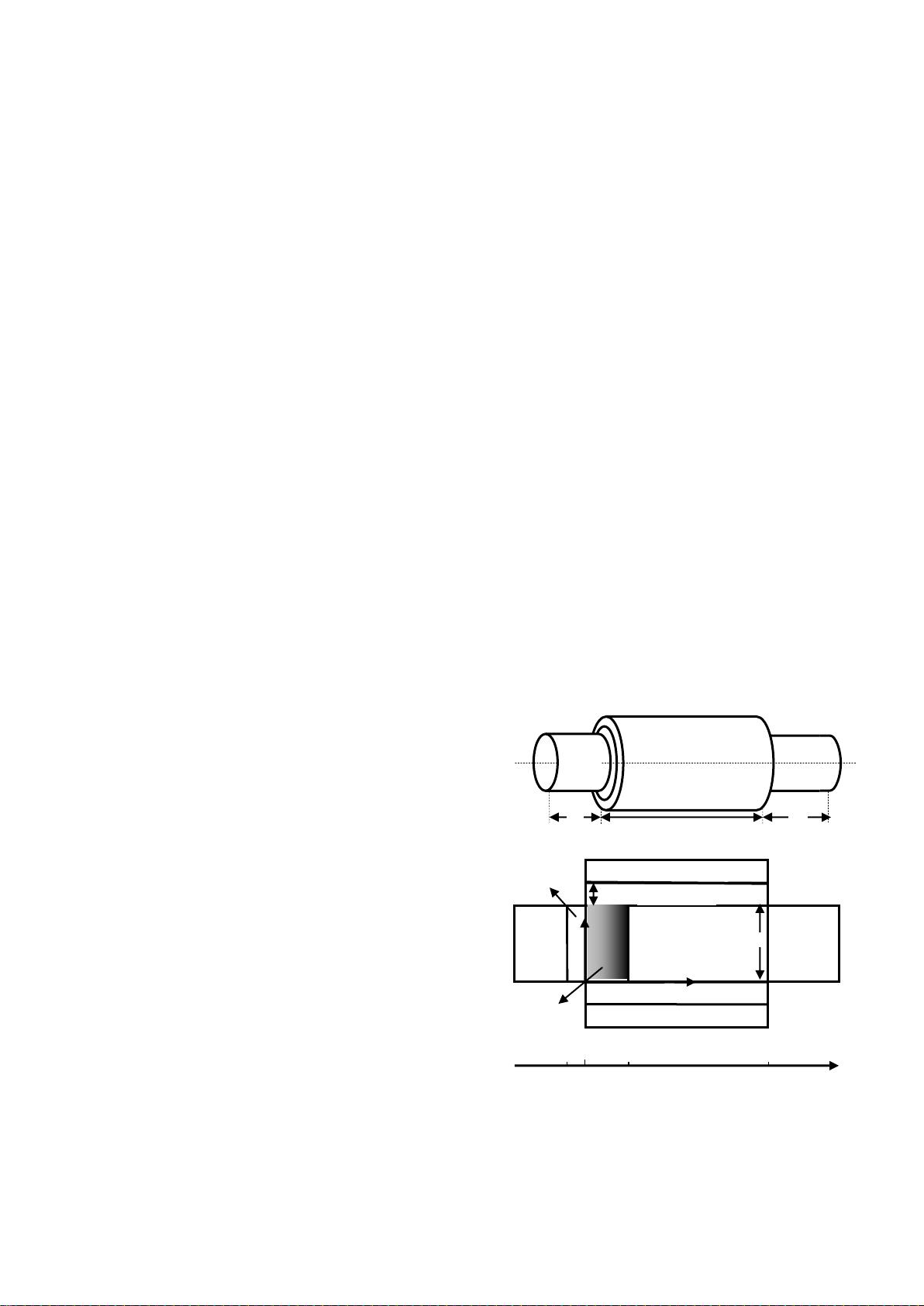

Fig.1. (b) shows the cross-section of the device with

n-channel. In this paper, the n-TFET is considered so that

the doping profile along the axis direction of the nanowire

with the

doping in source (

),

doping in

channel (

) and

doping in drain

(

). Band-to band tunneling (BTBT) happens

in the P-N junction at the source-channel region. Based on

the drift-diffusion (DD) theory, the electrons are moved

toward the drain thus the device can be divided into three

regions: the depletion region Ⅰ (

), the

tunneling region Ⅱ (

) and the surplus channel

region Ⅲ (

).

Fig.1. (a) 3-D structure of the n-channel GAA Silicon NW-TFET (b)

Cross-section of the device and its division into a depletion region (Ⅰ), a

tunneling region (Ⅱ) and a conventional GAA MOSFET region (Ⅲ).