Synopsys Design Compiler:综合流程与目标优化

需积分: 50 68 浏览量

更新于2024-07-18

1

收藏 1.8MB PDF 举报

Design Compiler,简称DC,是Synopsys公司提供的一种高级综合工具,用于电子设计自动化(EDA)过程中的逻辑综合阶段。它的核心作用是在满足设计目标如功能、速度和面积限制的前提下,将高级硬件描述语言(HDL,如VHDL或Verilog)编写的电路描述转换为实际可制造的晶体管级电路。这个过程包括三个主要阶段:转译、优化和映射。

1. **转译(Translation)**:这是将HDL描述的电路逻辑转化为通用工艺库(GTECH库)中的元素,这些元素仅表示逻辑功能,不具体绑定到特定厂商的工艺库。这样做的好处是设计者可以独立于具体工艺进行设计,便于实现跨平台兼容性。

2. **优化(Optimization)**:在这一阶段,DC会根据设计者设定的延迟、面积等约束条件,对电路进行调整,以尽可能地满足性能需求,例如降低功耗、提高速度,同时考虑面积效率。

3. **映射(Mapping)**:最后,DC将用GTECH库元件构建的电路映射到特定制造商的工艺库,引入LibraryCells,考虑到实际制造过程中的物理特性和工艺限制。

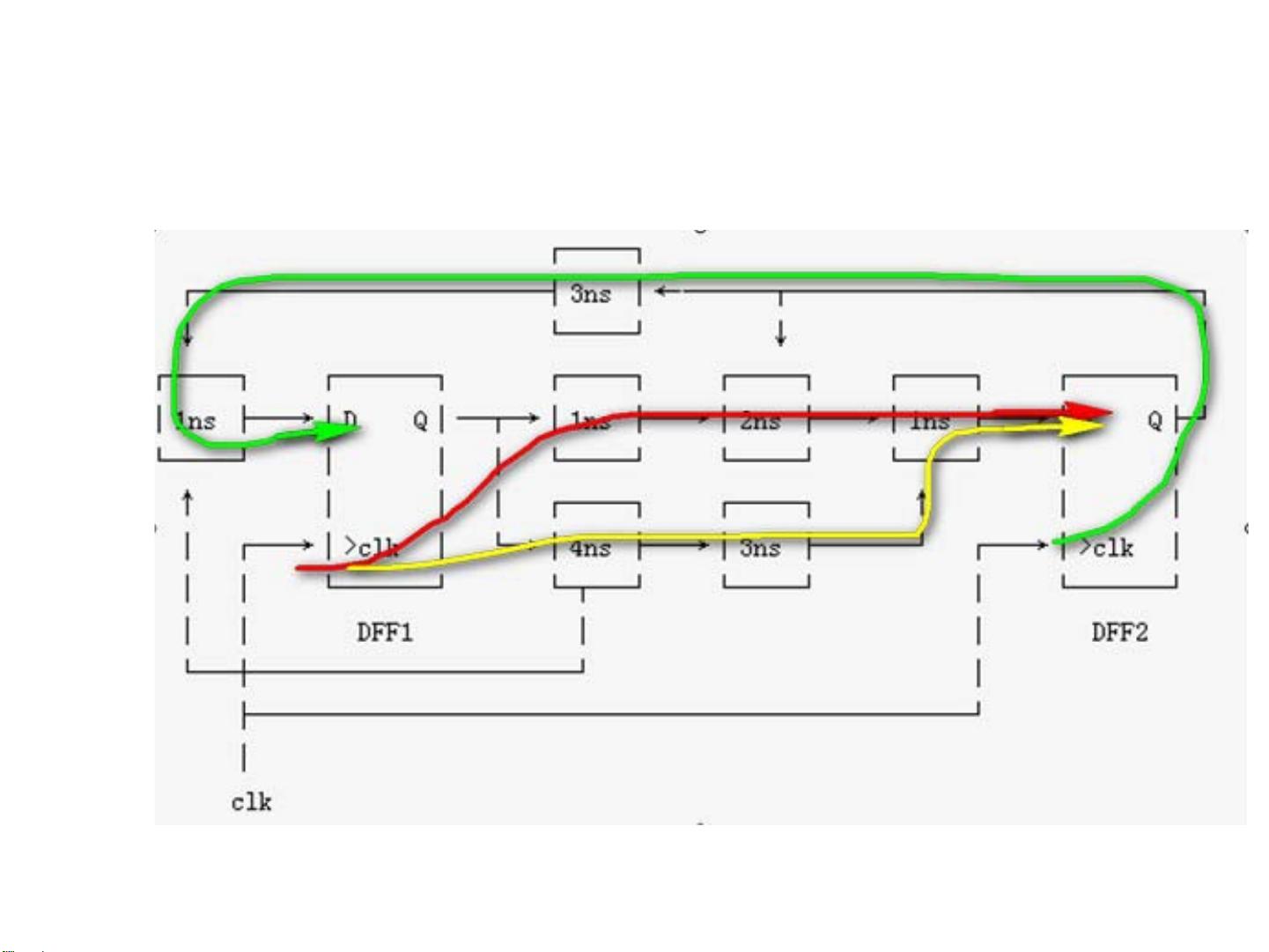

综合的目标是生成一个功能完整且在时序上满足要求的网表,追求面积最小化、功耗最小化和性能最大化。为了确保时序满足性,DC会分析电路,将其划分为不同的时序路径,包括基本输入到寄存器路径、触发器到触发器路径、触发器到输出路径以及基本输入到基本输出路径。每个路径的关键路径分析是至关重要的,需要计算数据到达时间(DataArrivalTime)、要求到达时间(DataRequiredTime)和时序裕度(slack),即实际到达时间与要求到达时间的差值。

建立时间和保持时间(setup time和hold time)是衡量电路稳定性的两个重要参数,它们定义了信号必须在何时到达以避免触发错误。设计者需要确保这些时间参数符合电路的时序规则,以保证信号的正确同步和电路的正常工作。

DC时序通路的划分基于电路的输入和输出节点,从所有基本输入端和时钟输入端开始,到所有基本输出端和数据输入端结束。通过精确分析这些路径,工程师可以有效地管理和优化设计,确保最终实现的电路能够在实际应用中表现出最佳性能。在整个设计流程中,DC作为关键的工具,帮助设计师将抽象的电路描述转化为可在实际硬件上实现的高效电路设计。

2024-10-26 上传

2024-10-25 上传

2024-10-01 上传

2024-10-26 上传

2024-10-26 上传

2024-11-16 上传

qq_41495424

- 粉丝: 0

- 资源: 1

最新资源

- 网络通信 组播技术白皮书

- 用友软件公司内部《编程规范》

- Javascript题目

- hibernate经典书籍

- Struts中文手册详解.pdf

- Good Features to Track.pdf

- checkstyle standard

- arm7中文技术参考 高清pdf

- IPv6 Advanced Protocols Implementation

- 常用ARM指令集及汇编 pdf

- c#聊天系统加解密.txt

- KMP 字符串模式匹配详解

- i3(internet indirection infrastructure).pdf

- 中国联通互联网短信网关协意

- JDBC API 数据库编程 实作教程

- c语言学习教程--高质量c编程指南