Vivado设计套件:BlockMemory Generator v8.4用户指南

需积分: 10 50 浏览量

更新于2024-07-09

收藏 3.57MB PDF 举报

"Xilinx公司的Vivado Design Suite中关于Block Memory Generator v8.4的LogiCORE IP产品指南(PG058)"

Xilinx的Block Memory Generator (BMG) v8.4是一款专为FPGA设计的核心组件,用于在Vivado Design Suite中创建和定制片上存储器资源。该IP核提供了灵活的功能,可生成适用于多种应用的块存储器,如数据缓冲、图像处理和算法加速等。

**章节1:概述**

1. **特性总结**:BMG v8.4提供了原生块内存生成器和AXI4接口块内存生成器两种选项,支持不同的系统接口需求。

2. **原生块内存生成器特性**:专为直接硬件访问设计,提供高效的内存访问性能。

3. **AXI4接口块内存生成器特性**:采用高级接口标准AXI4,支持AXI4-Lite或AXI4-Full,适合高性能并行数据传输。

4. **应用**:广泛应用于嵌入式系统、图像处理、数字信号处理等领域。

5. **许可和订购**:详细介绍了IP的许可策略和订购信息。

**章节2:产品规格**

1. **性能**:详细说明了内存块的性能参数,如读写速度、延迟和带宽。

2. **资源利用率**:阐述了BMG在FPGA逻辑资源、时钟网络、I/O端口等方面的占用情况。

**章节3:设计指导**

1. **一般设计准则**:包括了设计时的一般注意事项和最佳实践,以确保高效且可靠的实现。

2. **UltraScale架构特性**:针对Xilinx UltraScale架构设备,描述了特有的功能和设计考虑。

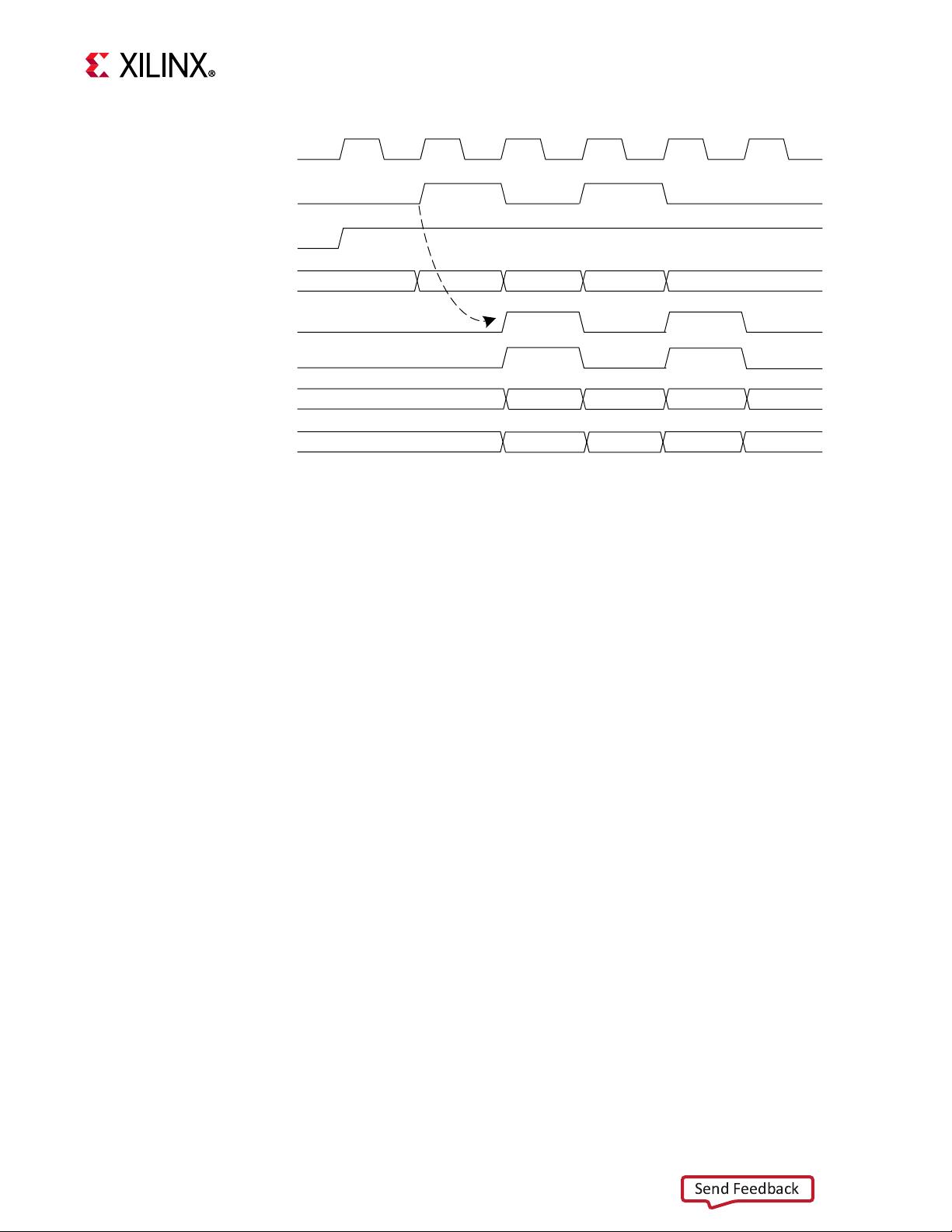

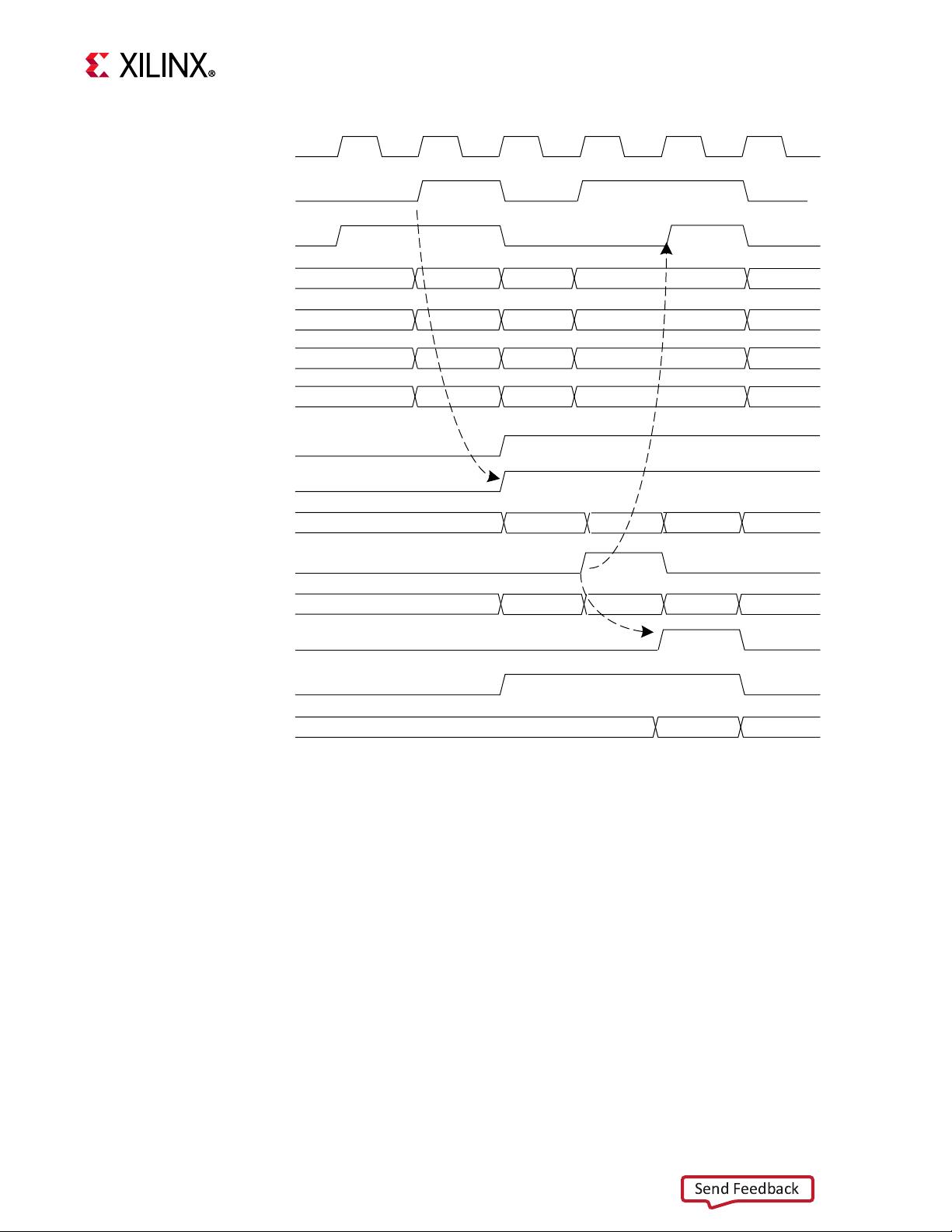

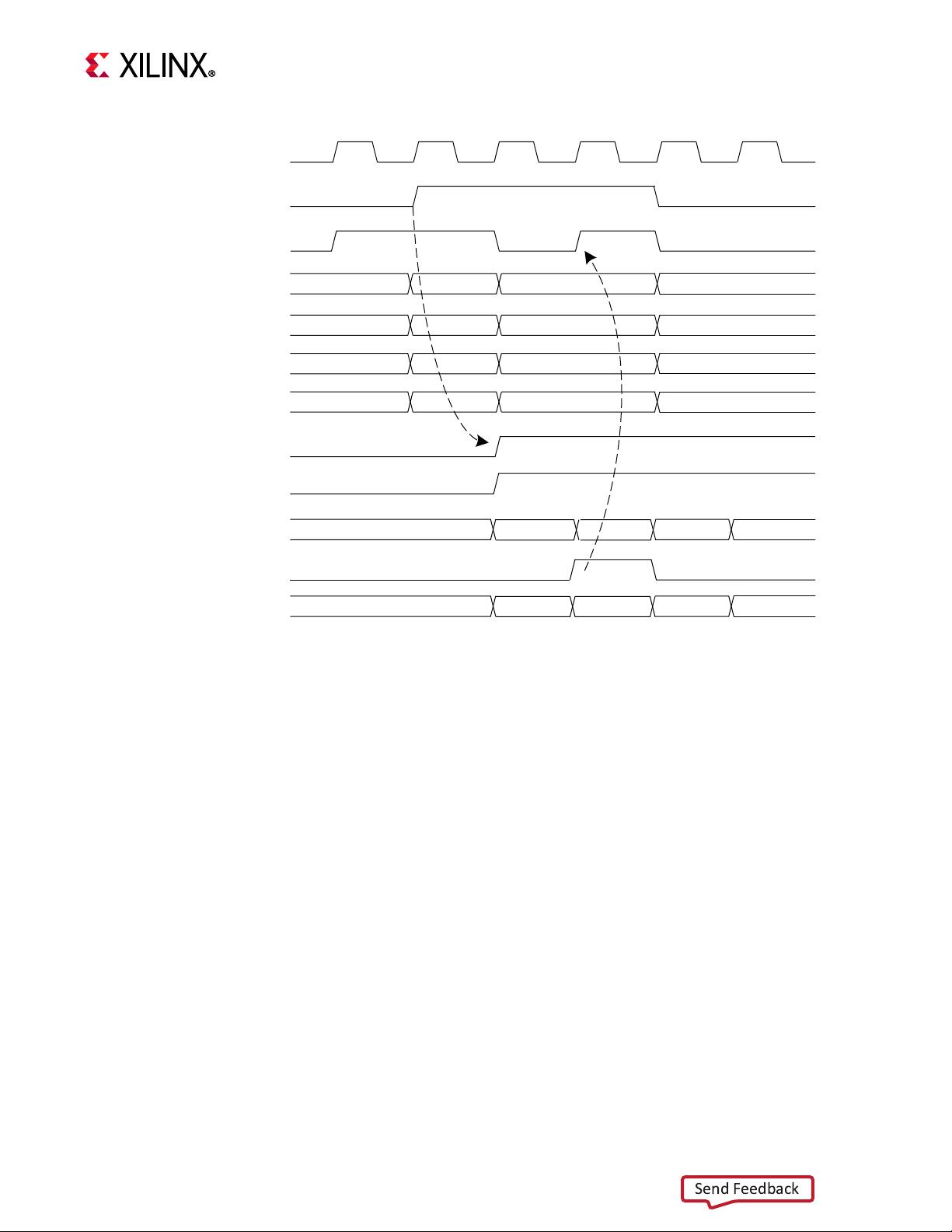

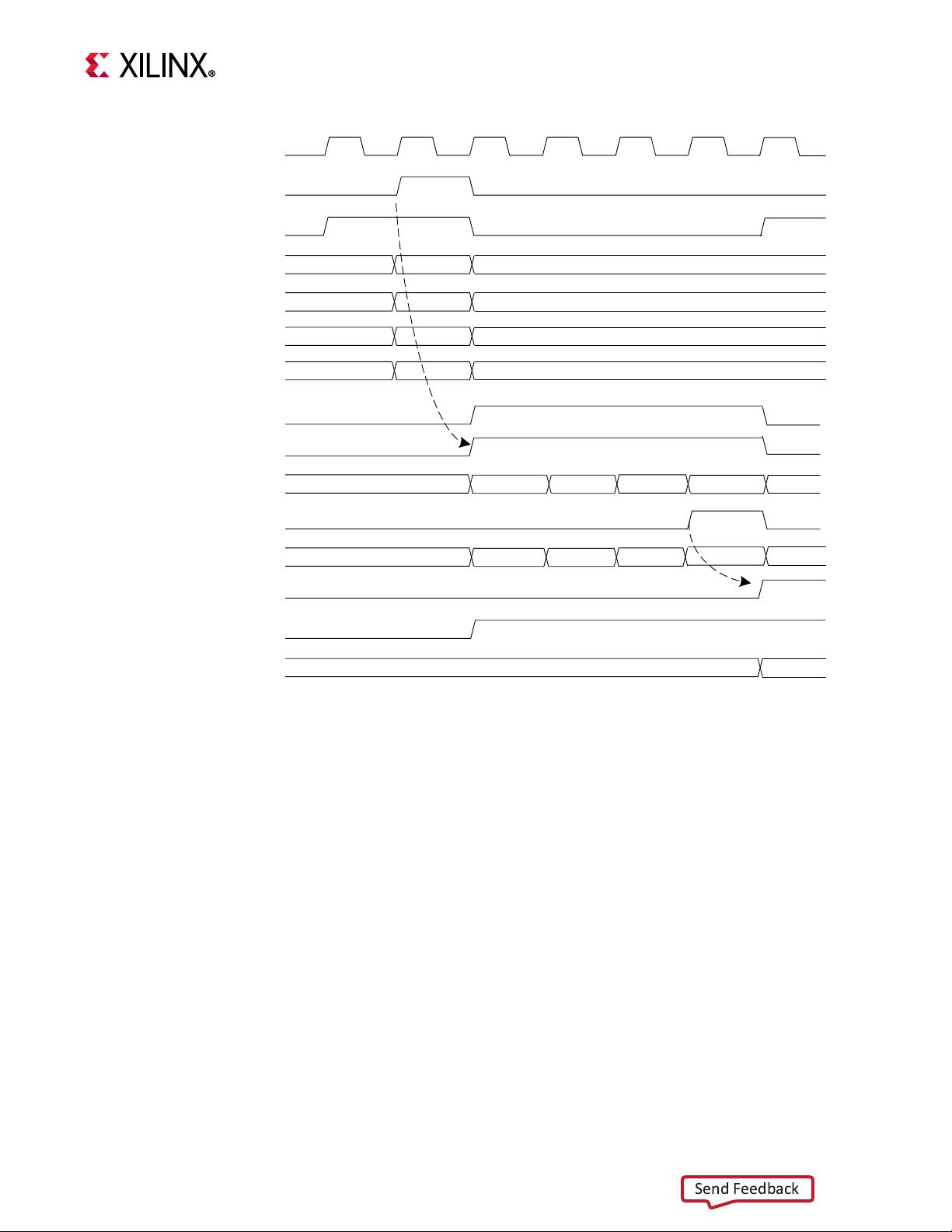

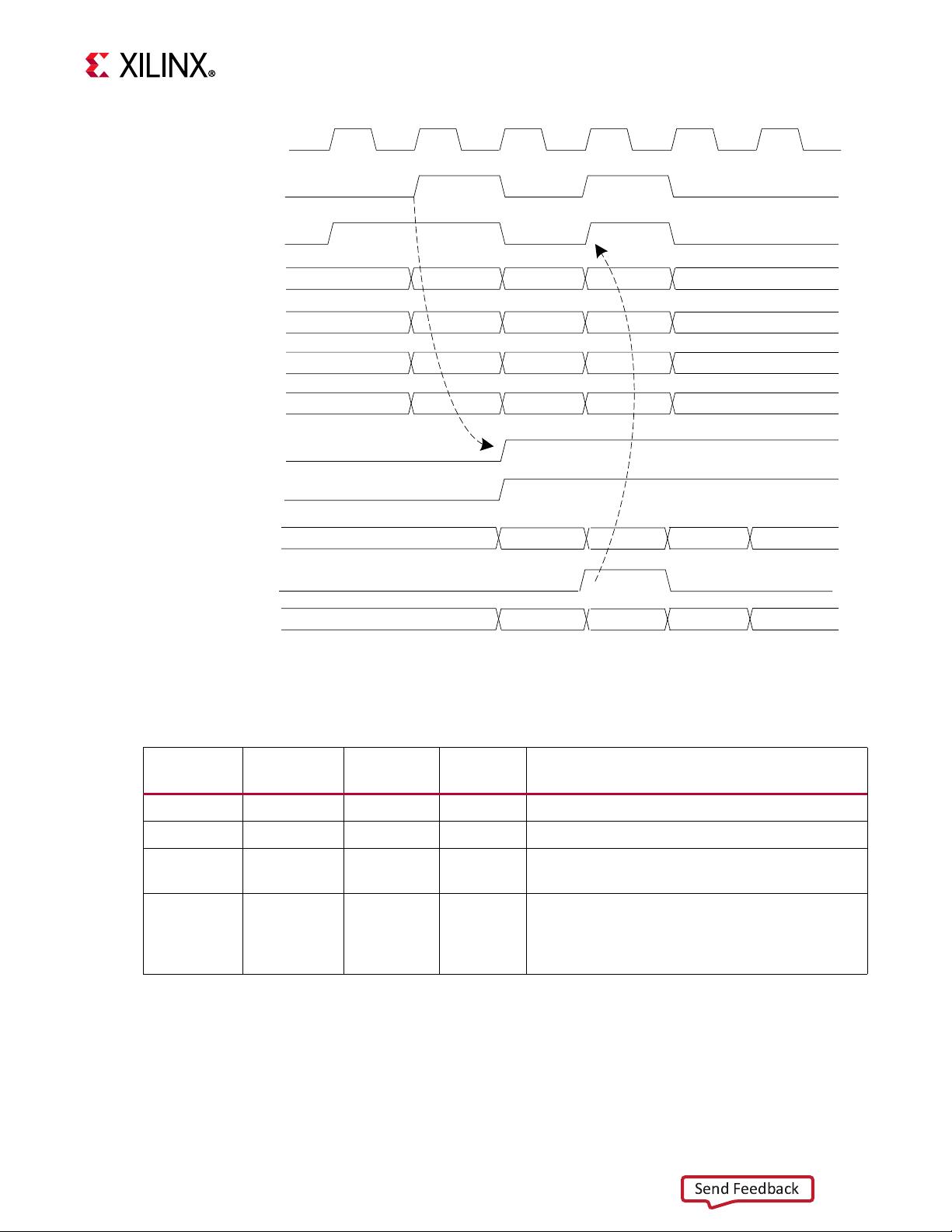

3. **时钟**:详细解释了时钟管理,包括多时钟域、同步和异步设计。

4. **复位**:涵盖了复位信号的配置和使用,确保系统正确初始化。

**章节4:设计流程步骤**

1. **自定义和生成核心**:描述了如何在Vivado环境中配置和生成BMG IP核。

2. **约束核心**:提供了设置设计约束的指导,以满足特定的性能目标。

3. **仿真**:介绍了如何进行功能仿真和时序仿真,验证设计的正确性。

4. **综合和实现**:指导用户通过综合和实现步骤,将设计转化为可编程逻辑的比特流。

**章节5:详细示例设计**

本章节提供了实际的设计例子,帮助用户理解和应用BMG IP核。

**章节6:测试平台**

1. **带有原生接口的核心**:展示了如何搭建测试平台以测试原生接口的BMG。

2. **带有AXI4接口的核心**:同样,也提供了AXI4接口BMG的测试平台搭建方法。

3. **消息和警告**:解释了可能遇到的错误消息和警告,以及如何解决这些问题。

**附录A:验证、符合性和互操作性**

1. **仿真**:包含了验证设计是否符合预期行为的仿真方法。

**附录B:升级**

1. **迁移到Vivado Design Suite**:提供了从其他设计环境迁移至Vivado的指导。

2. **Vivado中的升级**:解释了在Vivado环境中如何更新或升级现有的BMG设计。

PG058是Xilinx Vivado Design Suite中关于Block Memory Generator v8.4的详尽指南,涵盖了从设计到实现的全过程,对于使用FPGA开发需要高性能内存功能的项目具有极高的参考价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-07-15 上传

2019-08-16 上传

2021-04-03 上传

2020-12-29 上传

2023-06-13 上传

2021-03-22 上传

Ji'Nan_Mas

- 粉丝: 0

- 资源: 2

最新资源

- sebii : mighty failing ranger en live-crx插件

- appman-api-spec:RESTful API for Appman的规范

- nypority,源码转补码的c语言程序,c语言

- PaintCodeStar:个人资源

- AnaLight

- chromedriver-win32-V124.0.6367.91 稳定版

- 数据结构

- Driving-School-Test-System:该系统解决了潜水学校测试学生学习成绩的问题。 该系统可以方便地为老师生成试卷,学生可以在Internet上答复试卷

- linkedin mieux-crx插件

- 2000-2020年白城市500米植被净初生产力NPP数据

- credit

- kettle 的war包下载,webspoon9.0,kettle基于web的数据清洗工具

- 矩芯 sdk 矩芯 sdk 矩芯 sdk 矩芯 sdk

- 46005671,会员管理系统c语言源码,c语言

- 登山雪山风格网站模板

- resume:我的简历