FPGA实现部分响应CPM信号解调技术

162 浏览量

更新于2024-08-28

收藏 572KB PDF 举报

"本文主要探讨了基于FPGA的二进制部分响应L=2的连续相位调制(CPM)信号解调器的设计。文章分析了CPM信号的基本原理,利用VHDL硬件描述语言在FPGA上实现了解调器。解调过程包括信号接收、基带解调、似然序列估计和Viterbi译码等步骤。"

在现代通信系统中,为了提升数据传输速率和频谱利用率,采用高效编码和调制技术至关重要。连续相位调制(Continuous Phase Modulation,CPM)因其恒定的包络特性、紧凑的带宽以及高能量利用率而备受关注。CPM信号的相位轨迹连续变化,使得其在带宽效率上表现优异,适用于各种应用场景。

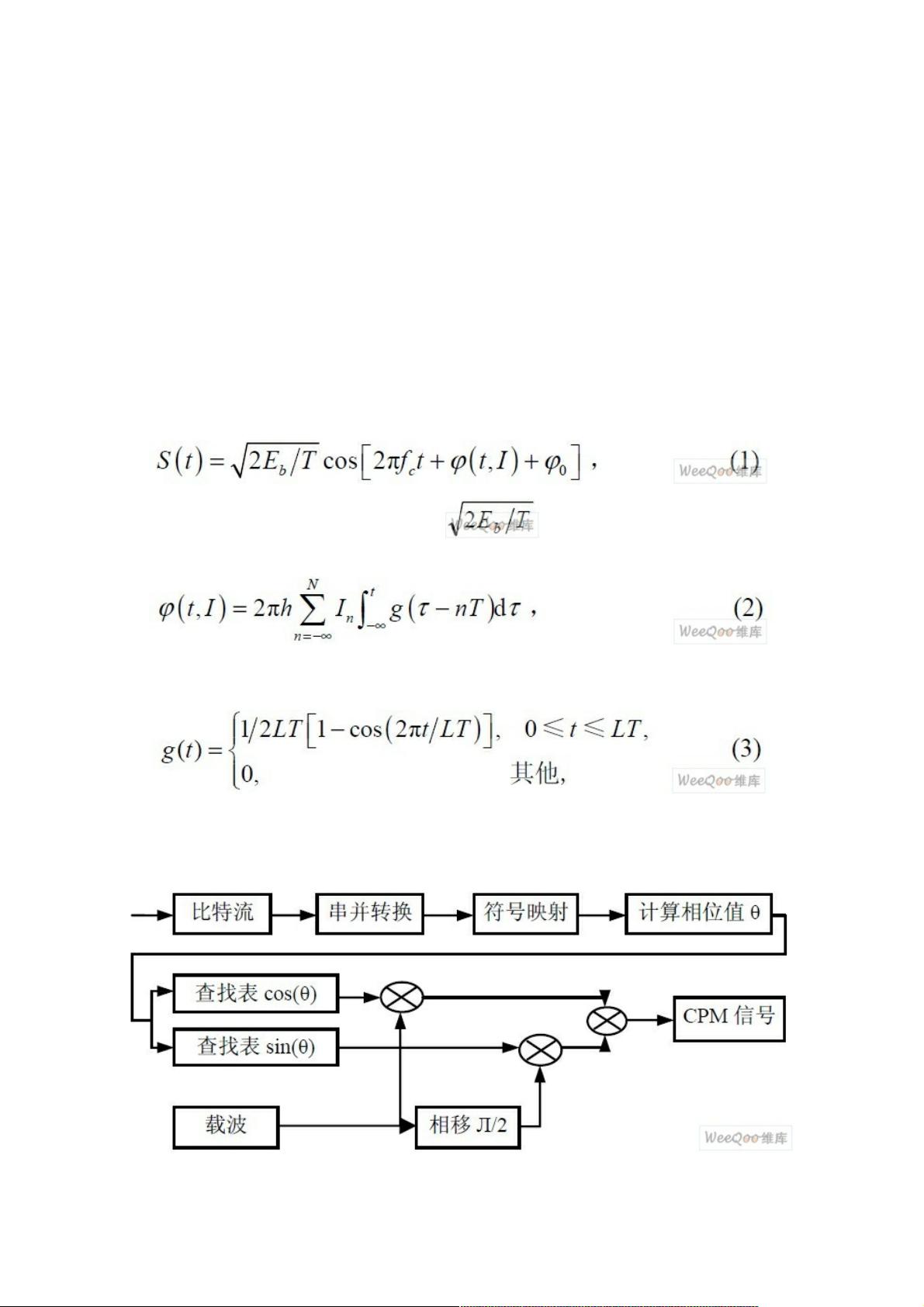

文章深入研究了二进制部分响应L=2的CPM调制方式。在这种调制模式下,信号的相位变化由信息序列决定,通过调制指数h和成形脉冲函数g(t)来控制。成形脉冲通常选择升余弦函数,以减少带外辐射和提高信号质量。调制后的CPM信号可以表示为载波频率cf乘以带有信息的相位函数,再乘以信号码元能量bE的正弦或余弦函数。

设计的FPGA解调器采用VHDL编程,其工作流程包括以下几个关键步骤:

1. **接收与下变频**:接收的复包络信号被分为I/Q两路,通过下变频转换到基带。

2. **相关运算**:基带I/Q信号分别与参考信号cos(ψ(t,a))和sin(ψ(t,a))进行相关运算,以提取相位信息。

3. **似然序列估计**:根据CPM信号的特性,通过似然比计算,估计出最有可能的信息序列。

4. **Viterbi译码**:利用Viterbi算法,对经过似然序列估计的信号进行硬判决或软判决解码,以恢复原始信息。

5. **判决**:最后,根据Viterbi译码结果进行判决,得出最终的数据比特流。

这种FPGA实现的解调器设计具有灵活性和高效性,能够适应实时通信环境的需求。通过硬件实现,可以大大提高解调速度,同时FPGA的可重配置特性使得设计可以针对不同调制参数进行优化。

基于FPGA的CPM解调器设计是通信系统中的一种重要技术,它充分利用了FPGA的并行处理能力和CPM信号的特性,以实现高效、低延迟的数据解调,对于提高通信系统的性能和可靠性具有重要意义。

141 浏览量

点击了解资源详情

1013 浏览量

141 浏览量

点击了解资源详情

点击了解资源详情

421 浏览量

2025-03-06 上传

weixin_38645266

- 粉丝: 4

最新资源

- 掌握PerfView:高效配置.NET程序性能数据

- SQL2000与Delphi结合的超市管理系统设计

- 冲压模具设计的高效拉伸计算器软件介绍

- jQuery文字图片滚动插件:单行多行及按钮控制

- 最新C++参考手册:包含C++11标准新增内容

- 实现Android嵌套倒计时及活动启动教程

- TMS320F2837xD DSP技术手册详解

- 嵌入式系统实验入门:掌握VxWorks及通信程序设计

- Magento支付宝接口使用教程

- GOIT MARKUP HW-06 项目文件综述

- 全面掌握JBossESB组件与配置教程

- 古风水墨风艾灸养生响应式网站模板

- 讯飞SDK中的音频增益调整方法与实践

- 银联加密解密工具集 - Des算法与Bitmap查看器

- 全面解读OA系统源码中的权限管理与人员管理技术

- PHP HTTP扩展1.7.0版本发布,支持PHP5.3环境