北京大学高级计算机系统结构:高速缓存与内存层次结构

需积分: 0 26 浏览量

更新于2024-06-30

收藏 5.99MB PDF 举报

"这是一份来自北京大学计算机科学技术系和微处理器研究开发中心的高级计算机系统结构课件,主要讲解了高速缓冲存储器(Cache)在应对微处理器与主存(DRAM)之间延迟差距问题上的作用,以及内存层次结构(Memory Hierarchy)的概念。课程日期为2014年3月17日,由程旭教授讲解。"

在计算机系统中,随着技术的发展,微处理器的速度不断提升,但与之相比,主存储器(如DRAM)的访问速度提升相对较慢,导致了性能瓶颈,即所谓的"延迟差距"。这个差距每年以大约50%的速度增长。为了解决这个问题,架构师引入了高速缓存(Cache)和内存层次结构的概念。

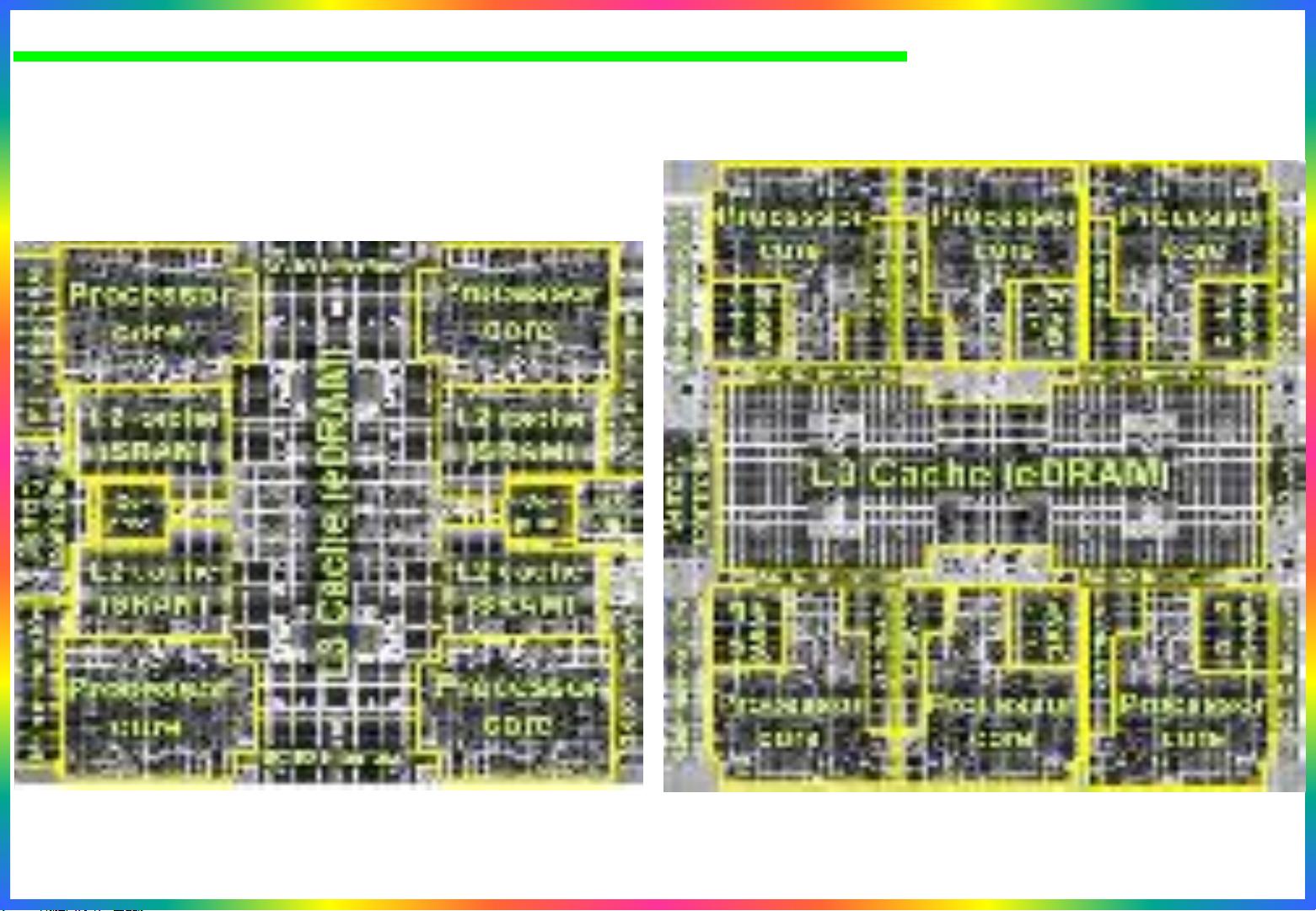

高速缓存是一种小而快速的存储器,位于CPU和主存之间,利用局部性原理(程序执行时倾向于连续访问同一块内存区域),将最近频繁使用的数据或指令暂存起来,以便CPU能快速访问,从而缩短等待时间。根据距离CPU的远近,通常分为多级缓存,如L1、L2和L3缓存,每一级缓存的速度和容量依次递减,成本也相应降低。

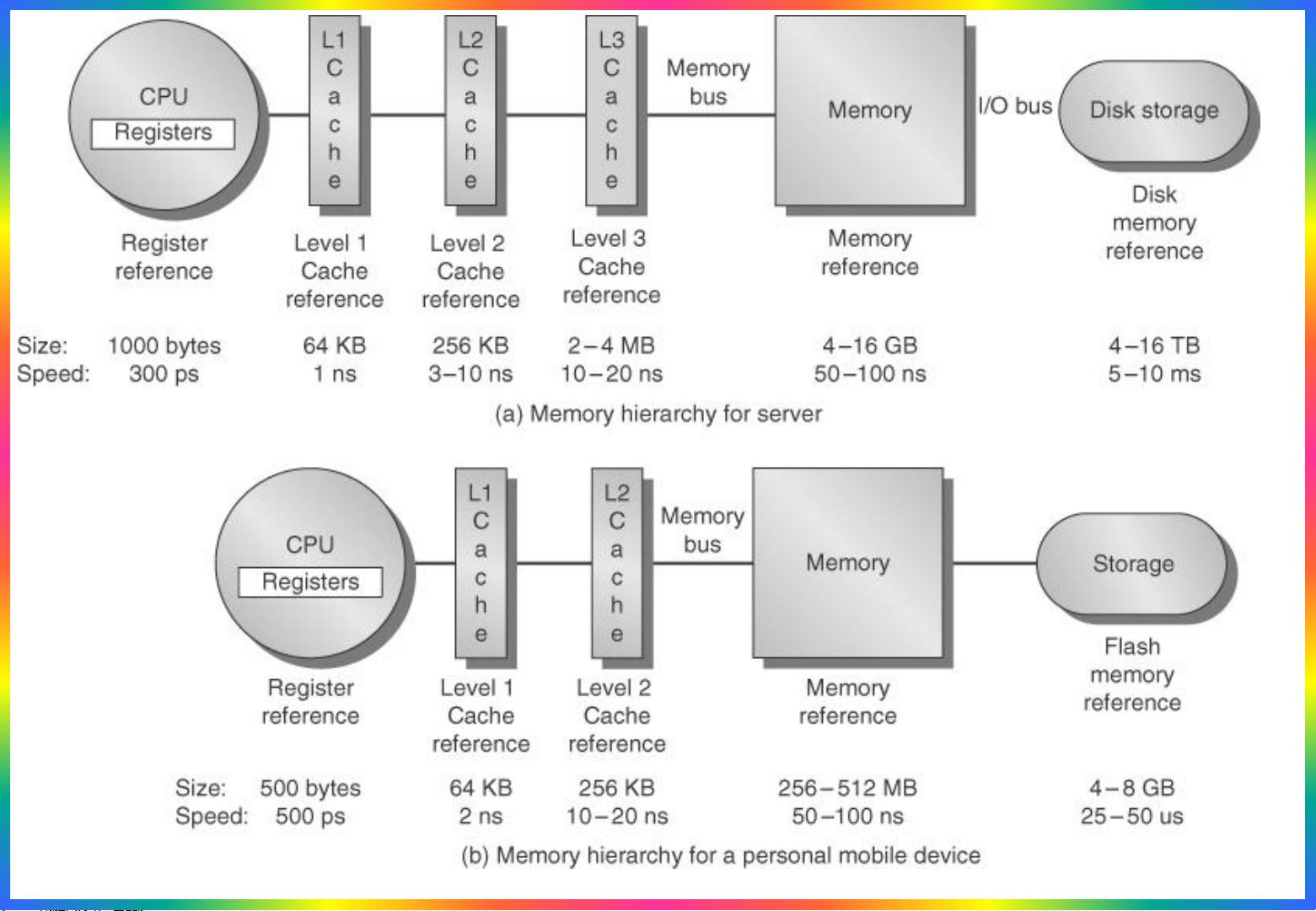

内存层次结构的设计目标是尽可能用最便宜的技术提供尽可能多的内存,并以最快的技术提供最快的访问速度。从最高层次到最低层次,包括寄存器(最快但容量最小)、L1 Cache、L2 Cache、L3 Cache、主内存(DRAM)和二级存储(如硬盘、固态硬盘、相变内存等),再到更慢的 tertiary storage(如磁带、云存储)。

缓存的工作机制包括替换策略(如LRU、LFU等)和一致性协议(如MESI协议),以确保数据的正确性和同步。缓存的命中率直接影响着系统的性能,因此优化缓存设计对于提高计算机系统的整体效率至关重要。

在1977年的例子中,Apple的微处理器速度为1000ns,而DRAM的速度为400ns,这表明即使在那时,处理器与内存之间的速度差异就已经很明显。通过引入缓存和优化内存层次结构,现代计算机能够有效缓解这种差距,保持高性能运行。

这份课件详细介绍了高速缓存作为解决处理器与主存速度差距的关键技术,以及内存层次结构如何协同工作,以平衡性能和成本,是理解计算机系统架构和性能优化的重要资料。

2022-08-03 上传

2022-08-03 上传

2022-08-03 上传

2022-08-03 上传

2022-08-04 上传

2022-08-03 上传

2022-08-03 上传

点击了解资源详情

点击了解资源详情

郑华滨

- 粉丝: 28

- 资源: 296

最新资源

- JavaScript实现的高效pomodoro时钟教程

- CMake 3.25.3版本发布:程序员必备构建工具

- 直流无刷电机控制技术项目源码集合

- Ak Kamal电子安全客户端加载器-CRX插件介绍

- 揭露流氓软件:月息背后的秘密

- 京东自动抢购茅台脚本指南:如何设置eid与fp参数

- 动态格式化Matlab轴刻度标签 - ticklabelformat实用教程

- DSTUHack2021后端接口与Go语言实现解析

- CMake 3.25.2版本Linux软件包发布

- Node.js网络数据抓取技术深入解析

- QRSorteios-crx扩展:优化税务文件扫描流程

- 掌握JavaScript中的算法技巧

- Rails+React打造MF员工租房解决方案

- Utsanjan:自学成才的UI/UX设计师与技术博客作者

- CMake 3.25.2版本发布,支持Windows x86_64架构

- AR_RENTAL平台:HTML技术在增强现实领域的应用