FPGA实现的位同步时钟提取技术研究

需积分: 10 40 浏览量

更新于2024-09-09

收藏 1.06MB PDF 举报

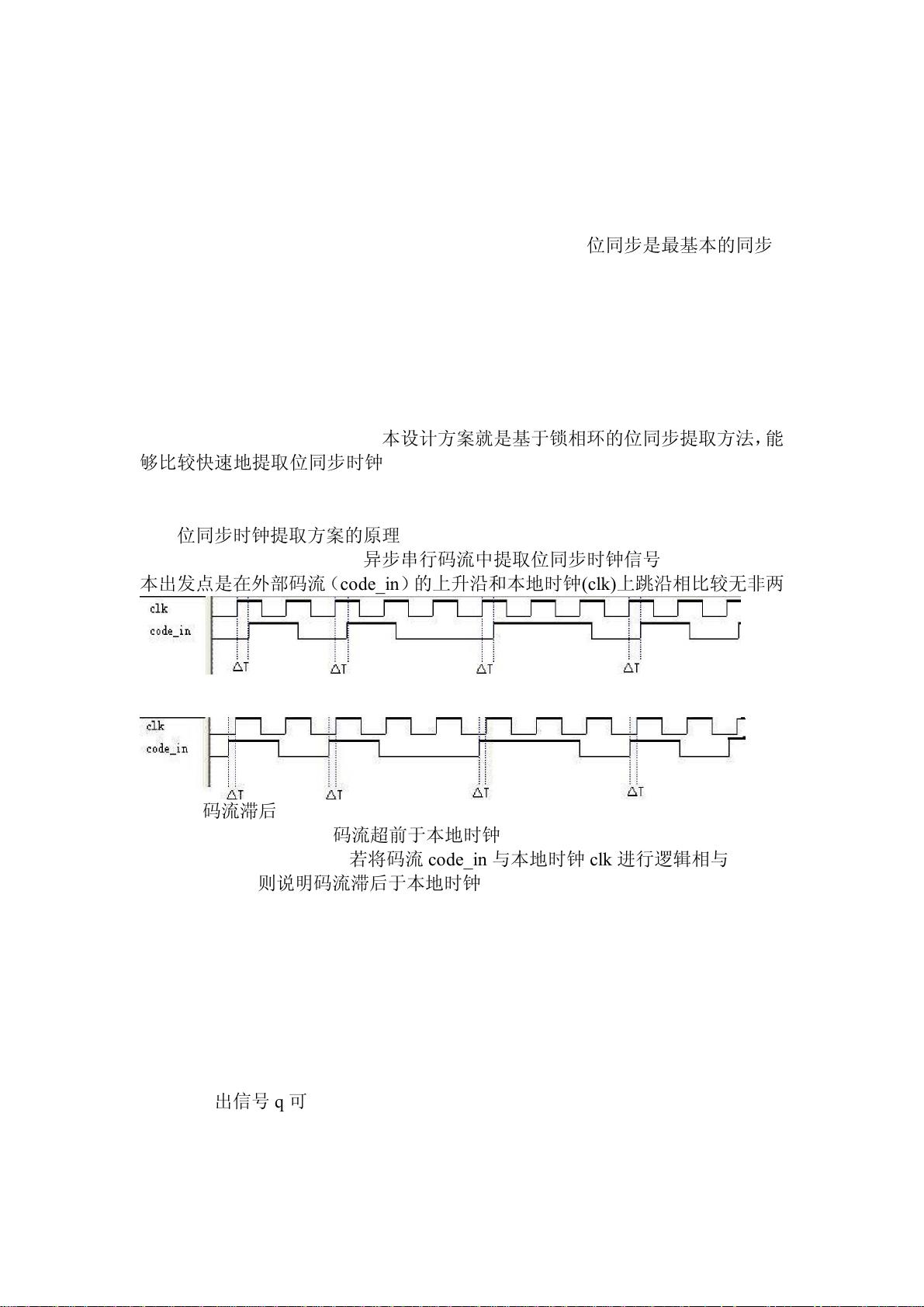

"该文介绍了一种基于FPGA的新型位同步时钟提取方案,主要应用于数字通信系统中,以解决同步系统模块化和芯片化的需求。方案利用锁相环技术,通过鉴相器和控制计数器检测并校正码流与本地时钟的相位差,从而实现位同步。设计在QuartusII软件中进行仿真,并使用Altera的CycloneII系列FPGA芯片实现。"

本文讨论的核心知识点包括:

1. **同步技术**:在数字通信系统中,位同步是确保数据正确传输的基础,它提供了接收端与发送端之间一致的时序参考,使得数据能够在正确的时间点被采样和解码。

2. **锁相环**(Phase-Locked Loop, PLL):是一种常用的位同步信号提取方法,通过比较接收到的码流和本地时钟的相位差,调整本地时钟频率以跟踪码流,从而实现位同步。锁相环具有快速锁定、设计灵活等优点。

3. **FPGA**(Field-Programmable Gate Array):是一种可编程逻辑器件,能够实现设计中的数字逻辑电路。在本文中,FPGA被用于实现位同步时钟提取的硬件逻辑,可以方便地进行参数修改和功能优化。

4. **位同步时钟提取**:文章提出的方案是从异步串行码流中提取位同步时钟。通过比较码流和本地时钟的上升沿,确定码流相对于本地时钟的超前或滞后状态,并据此调整相位。

5. **VHDL语言**:硬件描述语言,用于描述数字逻辑系统的行为和结构。在文中,VHDL代码用于描述如何根据码流和本地时钟的相与结果判断相位差,并生成控制信号。

6. **系统架构**:设计方案包含鉴相器、控制计数器和相位调整选择模块。鉴相器检测码流与本地时钟的相位差,控制计数器根据鉴相器输出的信号调整计数方向,相位调整选择模块则根据计数器输出进行相应的相位调整。

7. **仿真与实现**:使用Altera的QuartusII设计工具对系统进行仿真验证,最终选用CycloneII系列的Ep2c5 FPGA进行硬件实现,这体现了FPGA在数字逻辑设计中的灵活性和实用性。

综上,本文介绍的基于FPGA的位同步时钟提取方案,结合了锁相环技术和FPGA的优势,实现了高效、灵活的位同步时钟提取,对于现代高速数字通信系统具有重要的应用价值。

162 浏览量

475 浏览量

229 浏览量

2021-11-07 上传

101 浏览量

343 浏览量

2020-10-18 上传

2020-10-19 上传

chj_2012

- 粉丝: 1

最新资源

- 华为编程规范与实践指南

- 电脑键盘快捷键全解析:速成操作指南

- 优化JFC/Swing数据模型:减少耦合与提高效率

- JavaServerPages基础教程 - 初学者入门

- Vim 7.2用户手册:实践为王,提升编辑技能

- 莱昂氏UNIX源代码分析 - 深入操作系统经典解读

- 提高单片机编程效率:C51编译器中文手册详解

- SEO魔法书:提升搜索引擎排名的秘籍

- Linux Video4Linux驱动详解:USB摄像头的内核支持与应用编程

- ArcIMS Java Connector二次开发指南

- Java实现汉诺塔算法详解

- ArcGISServer入门指南:打造企业级Web GIS

- 从零开始:探索计算机与系统开发的发现之旅

- 理解硬件描述语言(HDL):附录A

- ArcGIS开发指南:ArcObjects与AML基础编程

- 深入浅出Linux:RedHat命令手册解析