Ultruscale FPGA配置Flash技术详解

需积分: 10 161 浏览量

更新于2024-08-05

1

收藏 320KB DOCX 举报

"这篇文档是关于Ultruscale系列FPGA如何操作配置Flash的学习笔记,主要探讨了SPI和BPI启动方式,以及如何利用FLASH的空余空间进行数据存储和远程更新镜像文件。文中提到了Xilinx VCU108开发板上的一个参考设计,该设计使用MicroBlaze软核和AXI外部存储器控制器来实现对BPIFlash的读写访问。验证流程包括使用BIN文件配置FPGA,通过Xmodem协议更新比特流,并利用STARTUPE3原语重新配置FPGA。此外,还介绍了时钟拓扑和AXIEMC内核的设置。"

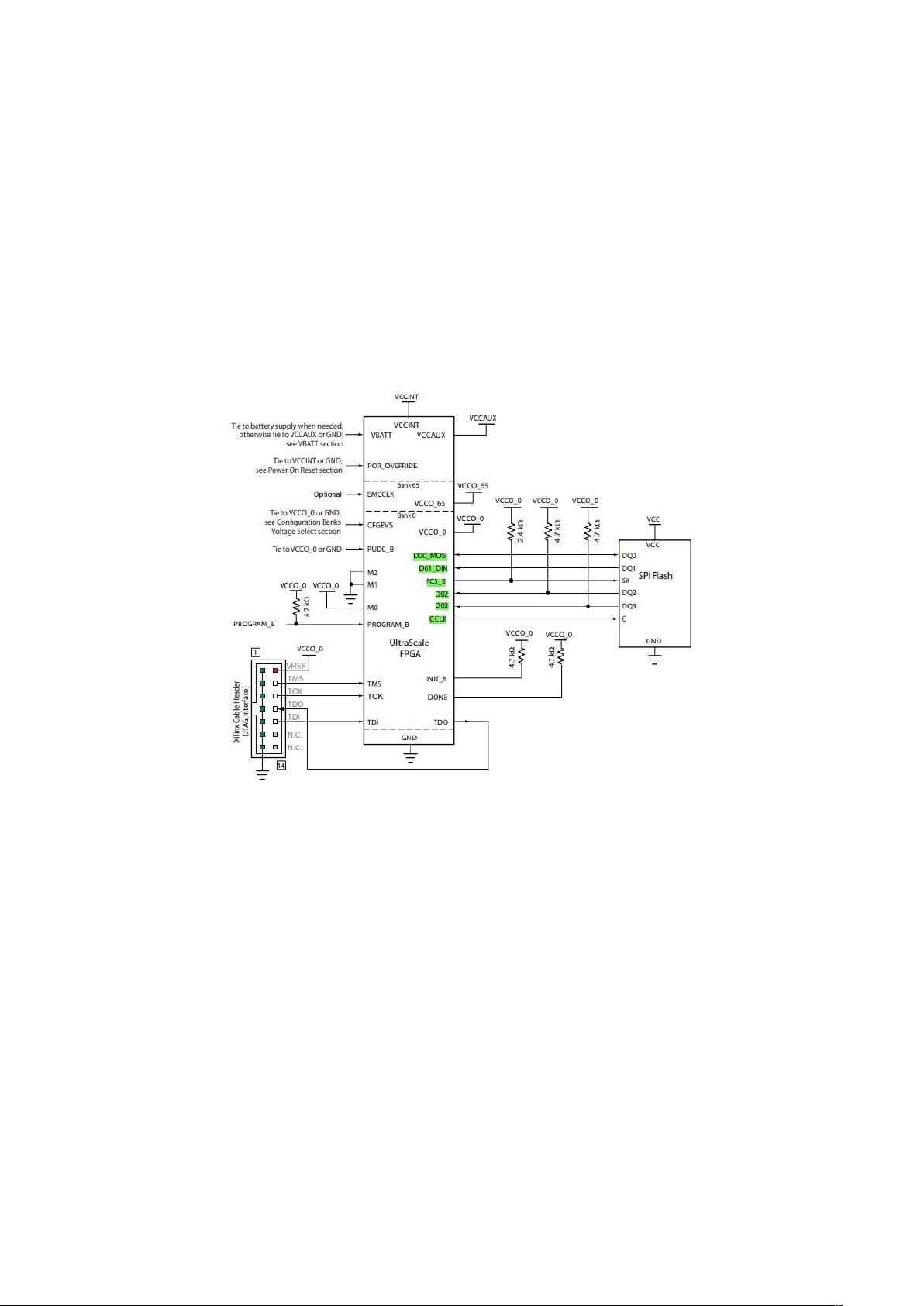

在Ultruscale系列FPGA中,配置Flash主要有两种启动方式:SPI(Serial Peripheral Interface)和BPI(Byte Parallel Interface)。SPI启动利用FPGA的bank0上的SPI数据线,而BPI启动则通过bank0上的DQ0-DQ3数据线。这两种启动方式允许FPGA在上电后加载配置数据,但同时也提供了额外的功能,即在程序加载完成后,可以利用未使用的Flash空间存储其他数据或进行远程更新。

为了实现这一功能,Xilinx提供了一个基于VCU108开发板的参考设计,其中MicroBlaze软核与AXI外部存储器控制器(AXIEMC)连接,通过STARTUPE3原语实现了对BPIFlash的配置后读写访问。STARTUPE3原语是一个关键组件,它允许在配置过程中控制时钟和初始化过程,使得FPGA能够在运行时访问并修改配置存储器。

参考设计中的系统时钟拓扑采用了外部300MHz差分时钟,经过MMCM(Multiplexer-based Memory Clock Manager)进行分频,生成100MHz和50MHz时钟。50MHz时钟被用于AXIEMC、处理器系统复位和axi_hwicap模块,而100MHz时钟服务于AXI外设互连和其他外设。AXIEMC需要与BPIFlash使用相同的时钟,因此50MHz时钟也被路由至STARTUPE3,确保正确同步。

在验证流程中,首先使用存储在BPIFlash中的BIN文件配置FPGA,这个BIN文件包含了STARTUPE3原语、接口逻辑、IP核和约束。之后,MicroBlaze运行的应用程序可以通过Xmodem协议从主机下载新的比特流更新。这个过程通过串口软件进行,如CRC校验的1024字节数据包写入BPIFlash。然后执行IPROG操作,更新BIN文件并重新配置FPGA,从而替换原来的BIN文件。

AXIEMC的设置对于正确访问BPIFlash至关重要。其时钟设置确保了与BPIFlash一致的50MHz时钟,同时为AXI接口的事件计时和写入操作提供支持。AXIEMC配置需要仔细调整,以确保与BPIFlash通信的正确性和稳定性。

这份学习笔记详细阐述了Ultruscale系列FPGA中如何操作配置Flash,包括启动方式的选择、MicroBlaze和AXIEMC的使用,以及STARTUPE3原语在动态更新配置文件中的作用。这些知识对于理解和实现FPGA的可编程性和灵活性至关重要。

200 浏览量

599 浏览量

131 浏览量

2022-10-22 上传

179 浏览量

2021-10-11 上传

天下无敌小霸王

- 粉丝: 159

- 资源: 19

最新资源

- webservice

- EXTJS 中文手册

- ubuntu8.04速成手册1.0

- Installing & Configuring Developing With XAMPP

- c#中treeview的使用方法

- 《华为认证网络工程师》自测题

- c#中进度条的使用技巧

- cn_foundation_Actionscript3.0_Animation

- R1762_R2632_R2700 RGNOS10.2配置指南_第四部分 应用协议配置指南

- 一个中专生的程序员之路

- R1762_R2632_R2700 RGNOS10.2配置指南_第三部分 IP地址与服务配置指南

- 详解西门子间接寻址详解西门子间接寻址

- 微 软 C 编 程 精 粹

- MyEclipse 6 Java 开发中文教程

- C#完全手册.pdf

- VARIANT的用法