16

LMK04616

ZHCSG70B –MARCH 2017–REVISED JULY 2019

www.ti.com.cn

Copyright © 2017–2019, Texas Instruments Incorporated

(1) Isolation in the victim channel is measured at aggressor frequency in power spectrum relative to the carrier (victim). Measured with

< 100-Hz resolution bandwidth. Internal LDO must be enabled.

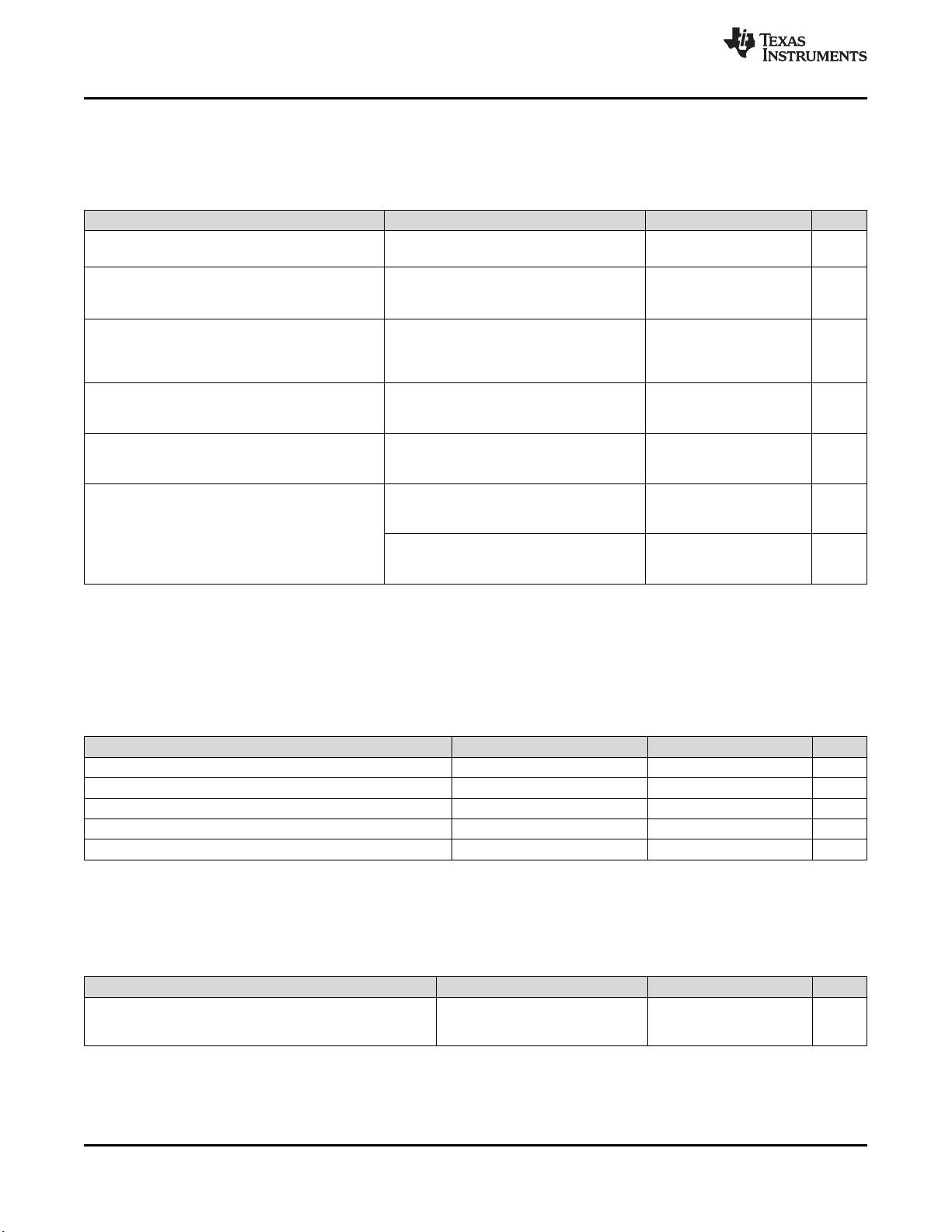

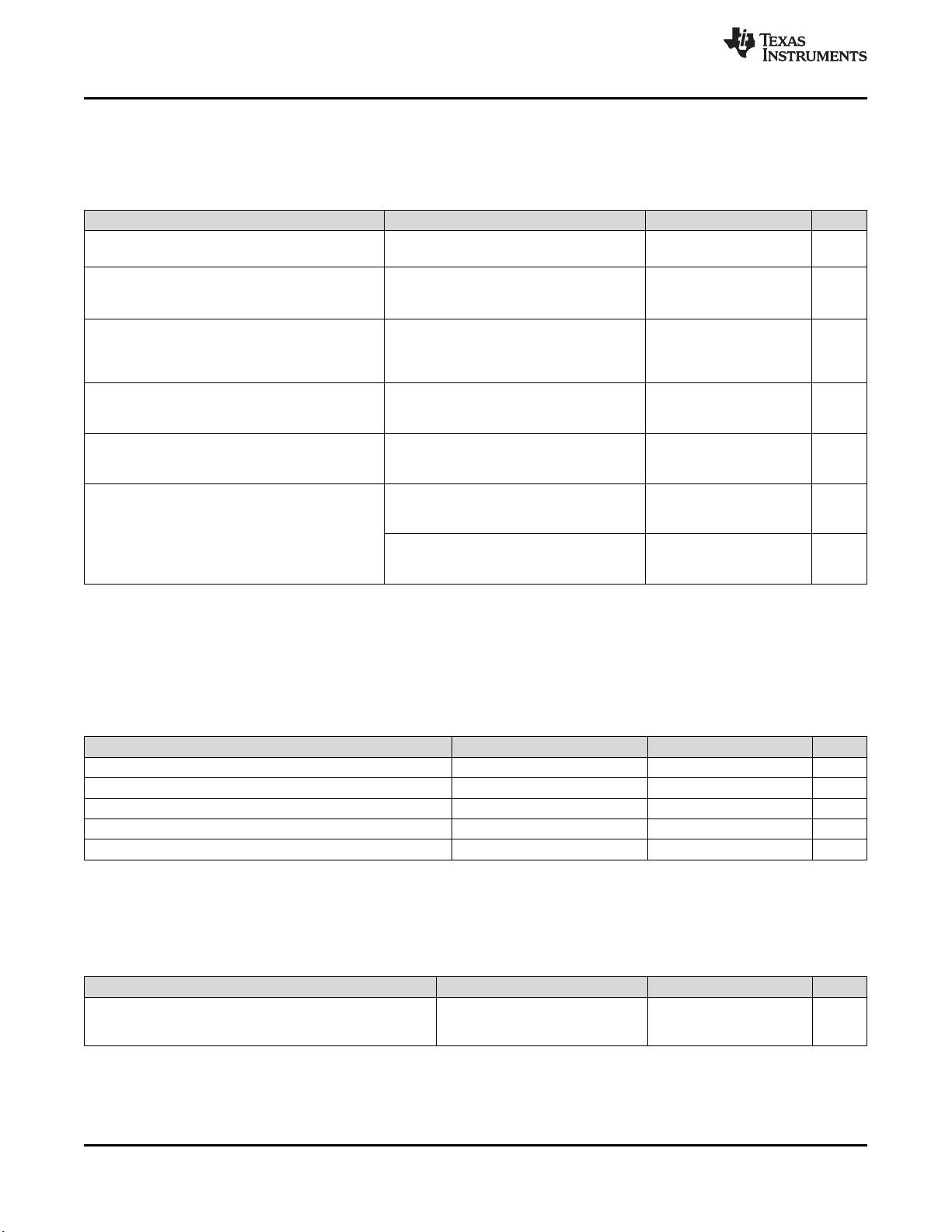

7.13 Clock Output Skew and Isolation Characteristics

3.135 V < VDD_PLL2OSC, VDD_PLL1, VDD_PLL2CORE, VDD_CORE < 3.465 V;

1.7 V < VDD_IO, VDD_OSC, VDDO_x < 3.465 V; –40°C < T

A

< 85°C and T

PCB

≤ 105°C. Typical values at VDD_PLL2OSC,

VDD_PLL1, VDD_PLL2CORE, VDD_CORE = 3.3 V, VDD_IO, VDD_OSC, VDDOx = 1.8 V, T

A

= 25°C, at the Recommended

Operating Conditions and are not assured.

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

|T

SKEW

|

Maximum CLKoutX to

CLKoutY

Same format, after SYNC

F

CLK

= 245.76 MHz, R

L

= 100 Ω, AC-coupled

60 95 |ps|

t

PD

CLKin0_

CLKoutX

Absolute propagation delay

from CLKin0 to CLKout0

Buffer mode

fin=fout=122.88 MHz

CLKout0_TYPE = HSDS 8 mA

3 ns

isolation

SYSref-

DeviceCLK

typ

Isolation between a SYSref

signal to a DeviceClk signal

(1)

CLKout2 = 7.68 MHz (SYSref, HSDS 8 mA,

aggressor)

CLKout3 = 122.88 MHz (DeviceClk, HSDS 8

mA, victim)

–94 dBc

isolation

CLKoutX

typ

Isolation between 2 adjacent

CLKout channels

(1)

CLKoutX = 153.6 MHz (HSDS 8 mA,

aggressor)

CLKoutY = 122.88 MHz (HSDS 8 mA, victim)

–70 dBc

isolation

OSCout-

CLKout

typ

Isolation between OSCout and

CLKoutX channels

(1)

OSCout = 30.72 MHz (HSDS 8 mA,

aggressor)

CLKoutY = 122.88 MHz (HSDS 8 mA, victim)

–99 dBc

isolation

PLL2PFD-

DeviceCLK

typ

Isolation between PLL2 PFD

update and CLKoutX

channels

(1)

PLL2 PFD update frequency = 122.88 MHz

(aggressor)

CLKoutX = 491.52 MHz (HSDS 8 mA, victim)

–80 dBc

PLL2 PFD update frequency = 122.88 MHz

(aggressor)

CLKoutX = 1228.8 MHz (HSDS 8 mA, victim)

–80 dBc

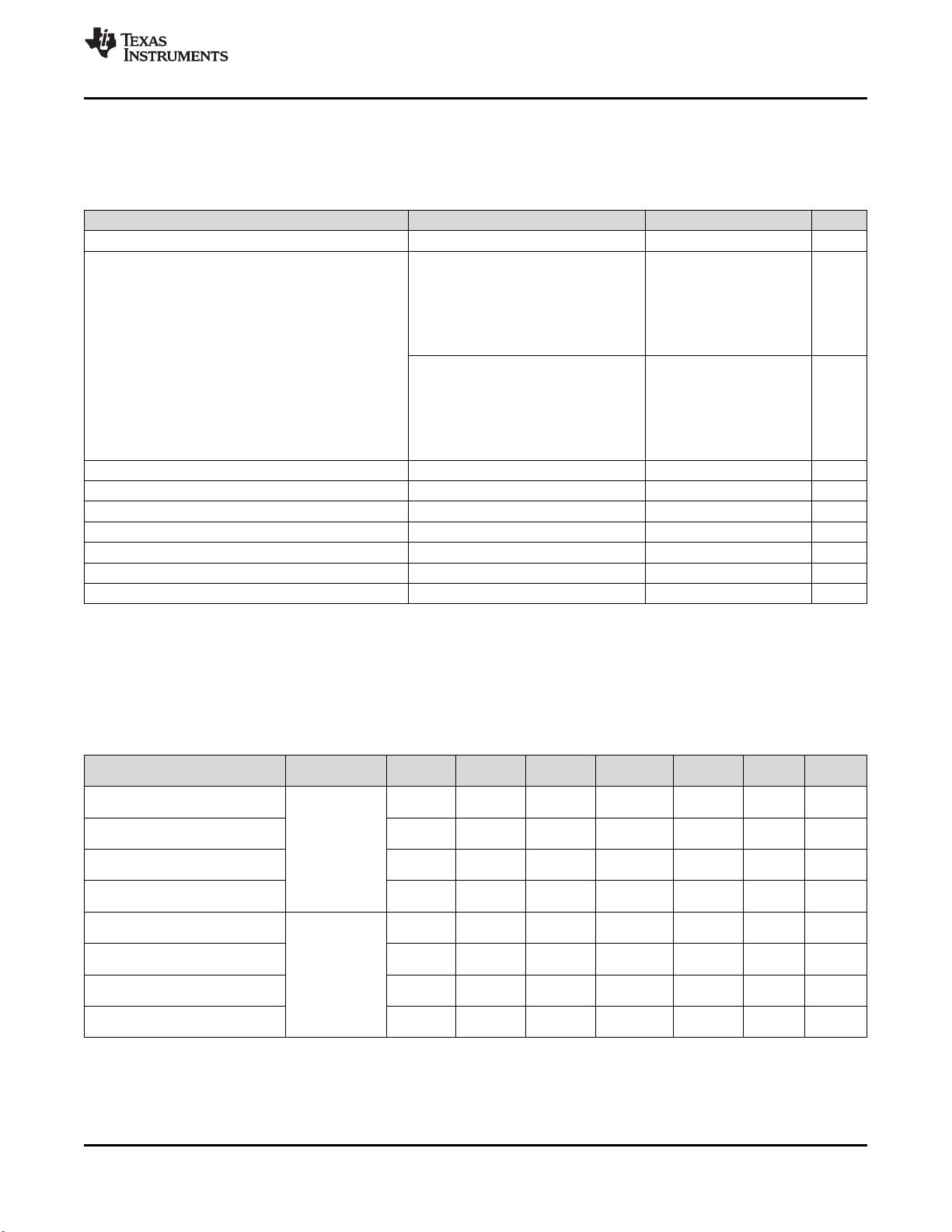

7.14 Clock Output Delay Characteristics

3.135 V < VDD_PLL2OSC, VDD_PLL1, VDD_PLL2CORE, VDD_CORE < 3.465 V;

1.7 V < VDD_IO, VDD_OSC, VDDO_x < 3.465 V; –40°C < T

A

< 85°C and T

PCB

≤ 105°C. Typical values at VDD_PLL2OSC,

VDD_PLL1, VDD_PLL2CORE, VDD_CORE = 3.3 V, VDD_IO, VDD_OSC, VDDOx = 1.8 V, T

A

= 25°C, at the Recommended

Operating Conditions and are not assured.

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

f

ADLY

max Maximum analog delay frequency 200 MHz

tstep

ADLY

1st 1

st

Analog delay step size 300 ps

tstep

ADLY

variation Analog delay step size variation Variation over all steps 66 ps

tstep

DDLY

1.47456GHz Digital delay step size at 1.47456 GHz Half-step enabled 339 ps

tstep

DDLY

variation Digital delay step size variation 0 ps

(1) Assured by characterization. ATE tested at 122.88 MHz.

(2) OSCout will oscillate at start-up at the frequency of the VCXO attached to OSCin port. All other outputs are disabled.

7.15 DEFAULT POWER on RESET CLOCK OUTPUT Characteristics

3.135 V < VDD_PLL2OSC, VDD_PLL1, VDD_PLL2CORE, VDD_CORE < 3.465 V;

1.7 V < VDD_IO, VDD_OSC, VDDO_x < 3.465 V; –40 °C < T

A

< 85°C and T

PCB

≤ 105°C. Typical values at VDD_PLL2OSC,

VDD_PLL1, VDD_PLL2CORE, VDD_CORE = 3.3 V, VDD_IO, VDD_OSC, VDDOx = 1.8 V, T

A

= 25°C, at the Recommended

Operating Conditions and are not assured.

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

f

CLKout-startup

Default OSCout clock frequency at device

power on after RESETN = 1

(1) (2)

SYNC pin pulled Low at start up

VCXO used is a 122.88-MHz

Crystek CVHD-950-122.880

122.88 MHz