FPGA内部结构与工作原理探索

需积分: 9 90 浏览量

更新于2024-09-08

收藏 305KB DOCX 举报

"FPGA内部原理,包括其组成、工作原理和开发流程的详细解析"

FPGA,全称为现场可编程门阵列,是集成电路(ASIC)设计中的一个重要工具,它结合了定制电路的优势和可编程器件的灵活性。FPGA在PAL、GAL、EPLD等早期可编程器件的基础上发展而来,提供了更丰富的门电路数量,以满足复杂系统的需求。

FPGA的结构主要由三大组件构成:输入输出单元(IOE)、逻辑阵列块(LAB)和内部连接(Interconnect)。

1. 输入输出单元(IOE)

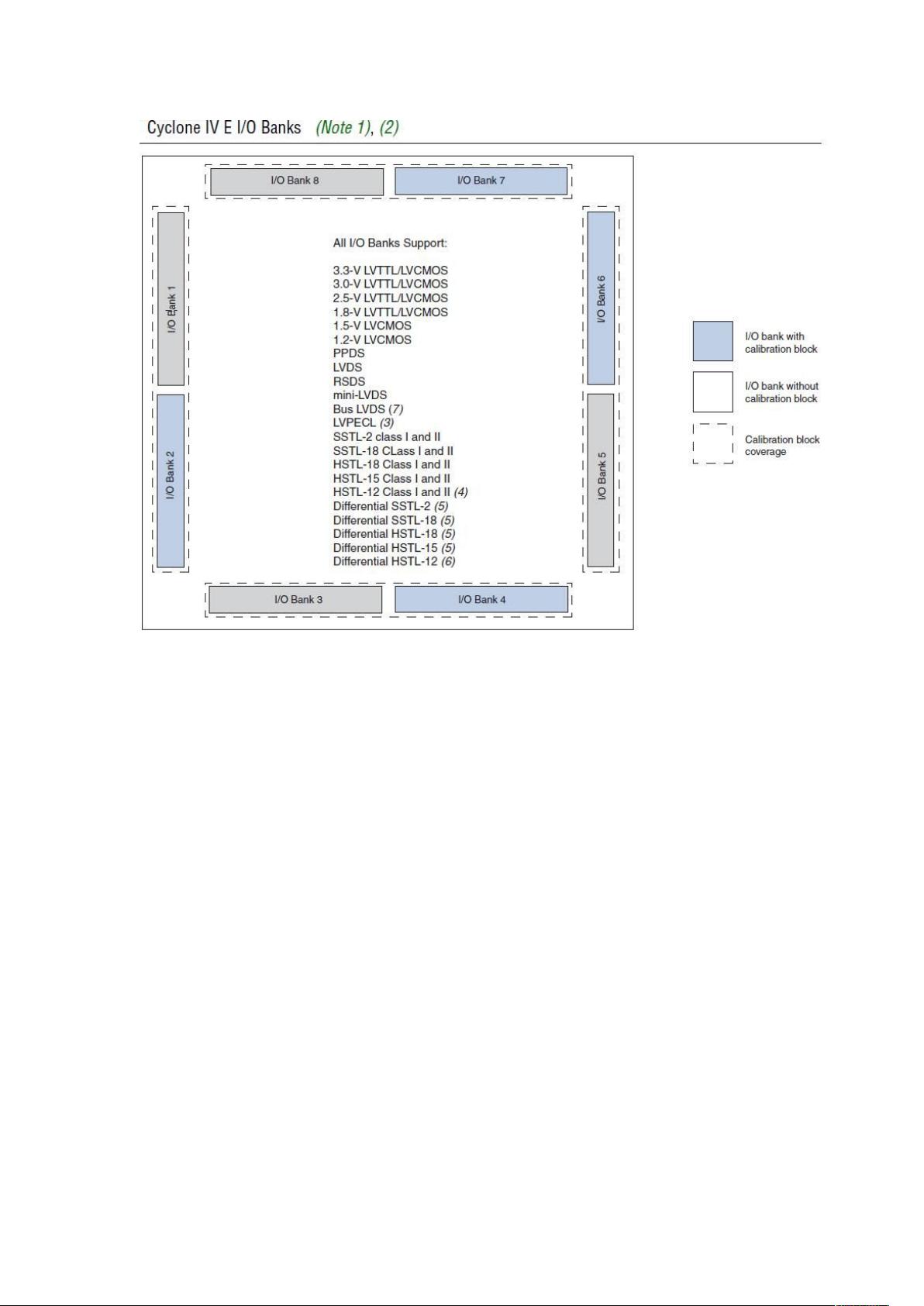

IOE是FPGA与外部电路交互的关键部分,负责处理输入和输出信号的电气匹配。它支持多种I/O标准,如LVTTL、LVCMOS、PCI、LVDS、RSDS等,并能适应不同的电压等级(如5V、3.3V、2.5V、1.8V、1.5V)。例如,ALTERA的Cyclone IV E系列设备EP4CE115F29拥有8个IO组,每个组都可配置为不同的I/O标准,且能调整驱动电流和上下拉电阻。

2. 逻辑阵列块(LAB)

LAB是FPGA的基础逻辑构建模块,包含可配置逻辑元素(LE)、LAB控制信号、LE进位链、寄存器链和局部互连。LE是Cyclone IV设备中最基本的逻辑单元,由查找表(LUT)和寄存器组成。LUT通常为4输入,相当于一个16x1的SRAM,用于存储逻辑函数的结果,实现快速的逻辑运算。每个LE还有与其关联的寄存器,用于数据的暂存和时序控制。

3. 内部连接(Interconnect)

Interconnect是FPGA内部的布线资源,负责连接IOE、LAB以及内部其他资源。它提供了一种灵活的布线机制,可以根据设计需求配置路径,实现复杂的逻辑连接。

FPGA的工作原理和开发流程:

当设计者用硬件描述语言(如Verilog或VHDL)描述逻辑电路后,通过开发工具(如Xilinx的Vivado或ALTERA的Quartus II)进行编译和综合。这些工具会将设计转化为适合FPGA的配置数据,然后写入FPGA的配置存储器。在系统运行时,配置数据控制FPGA的IOE、LAB和Interconnect,根据预设的逻辑关系执行操作。

开发流程一般包括设计输入、逻辑综合、布局布线、时序分析、配置及验证等多个步骤。设计者需要确保设计满足功能要求,同时优化性能、功耗和面积(通常称为“功耗-面积-速度”权衡)。

FPGA的应用广泛,涵盖了通信、计算、图像处理、嵌入式系统等多个领域,其灵活性使得FPGA在原型验证、快速原型设计和高性能计算等方面有着显著优势。随着技术的发展,FPGA不断融合新的特性,如硬核处理器系统(HPS)和高带宽内存(HBM),使其在系统级集成中扮演着越来越重要的角色。

2478 浏览量

186 浏览量

107 浏览量

494 浏览量

224 浏览量

2012-10-17 上传

101 浏览量