基于FPGA的高效通信系统帧同步提取策略

144 浏览量

更新于2024-08-30

收藏 141KB PDF 举报

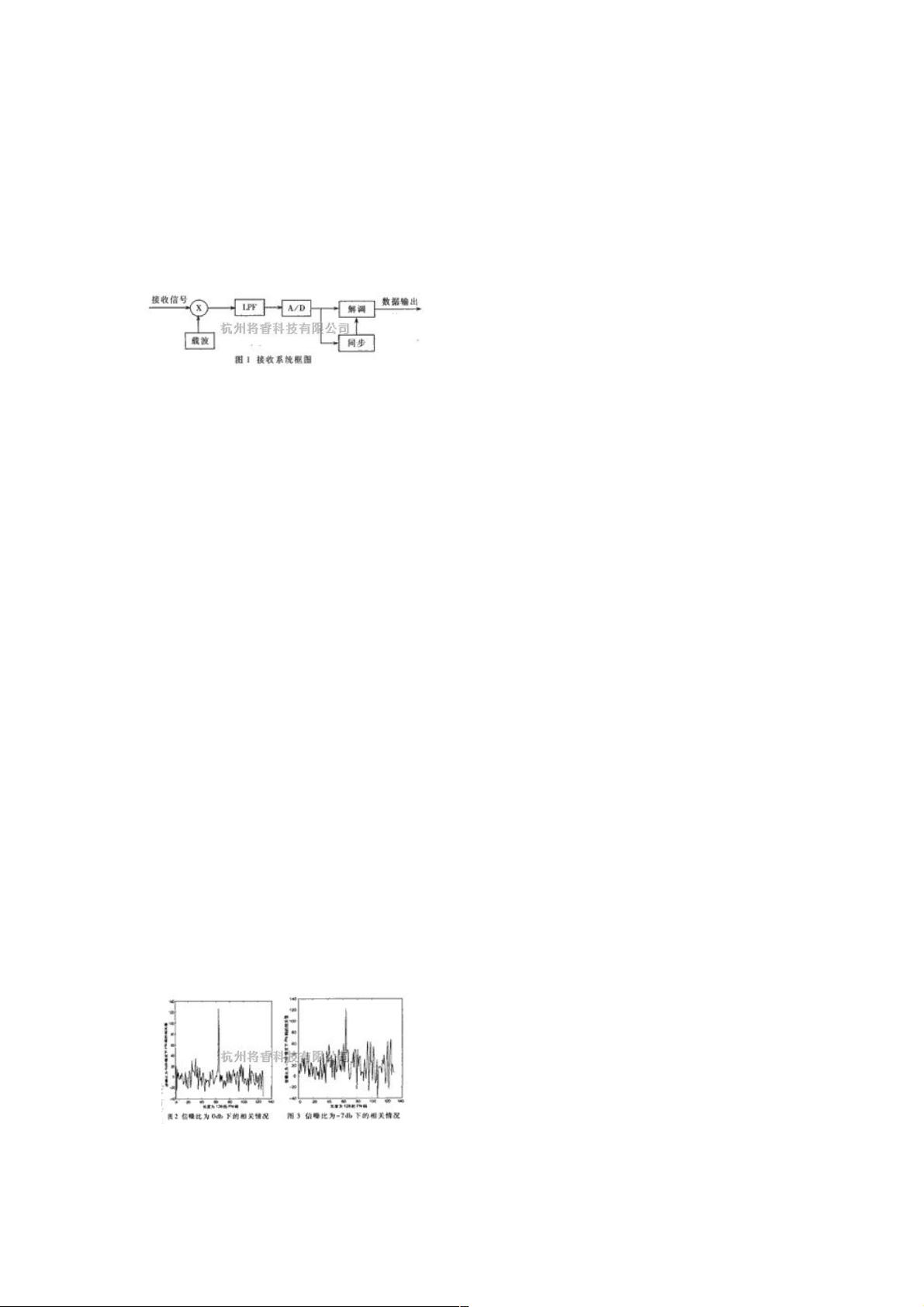

本文主要探讨了在电子设计自动化(EDA)和可编程逻辑器件(PLD)领域中,如何利用现场可编程门阵列(FPGA)技术来实现高效的帧同步提取方法。通信系统中,确保发送端和接收端之间的时钟同步至关重要,这有助于正确的信息解调和数据传输。FPGA作为一种创新的可编程ASIC,它融合了门阵列的通用结构与PLD的现场可编程特性,使得设计者能够灵活定制,且具有高集成度、快速开发和便捷编程的优点。

文章的核心内容集中在基于FPGA的同步方案设计上,特别强调了同步序列码的选择。同步序列码如m序列码因其良好的自相关性和互相关特性,如表一所示,相比Gold系列码,m序列码具有更强的抗干扰能力和更低的截获概率。在实际应用中,通过在每个帧的开头添加扩频码,如M序列码,可以增加同步的鲁棒性,并确保在强噪声环境下仍能准确识别帧边界,从而保证数据通信的可靠性。

M序列码是通过在原始m序列码后填充零来形成PN码,以便实现相等匹配,因为M序列码中1的个数总比0多一个。在同步提取过程中,通过相关法检测数据,当数据中的同步头与本地同步头对齐时,相关函数会出现明显的峰值,但实际峰值可能低于理论值,这是因为数据传输过程中存在噪声和其他干扰因素。

总结来说,本文的研究提供了FPGA在通信系统中实现高效帧同步的方法,特别是在选择合适的同步序列码,如M序列码,以及利用FPGA的灵活性和高性能特性来设计和优化同步系统。这一研究成果对于提高通信系统的稳定性和效率具有重要意义,特别是在现代高速和复杂网络环境中。

175 浏览量

505 浏览量

232 浏览量

175 浏览量

505 浏览量

125 浏览量

174 浏览量

2020-12-05 上传

248 浏览量

weixin_38729108

- 粉丝: 5

最新资源

- C#实现程序A的监控启动机制

- Delphi与C#交互加密解密技术实现与源码分析

- 高效财务发票管理软件

- VC6.0编程实现删除磁盘空白文件夹工具

- w5x00-master.zip压缩包解析:W5200/W5500系列Linux驱动程序

- 数字通信经典教材第五版及其答案分享

- Extjs多表头设计与实现技巧

- VBA压缩包子技术未来展望

- 精选多类型导航菜单,总有您钟爱的一款

- 局域网聊天新途径:Android平台UDP技术实现

- 深入浅出神经网络模式识别与实践教程

- Junit测试实例分享:纯Java与SSH框架案例

- jquery xslider插件实现图片的流畅自动及按钮控制滚动

- MVC架构下的图书馆管理系统开发指南

- 里昂理工学院RecruteSup项目:第5年实践与Java技术整合

- iOS 13.2真机调试包使用指南及安装