Allegro设计规则设置指南V1.2:约束规则设置详解

需积分: 19 142 浏览量

更新于2024-07-28

收藏 735KB PDF 举报

Allegro中的约束规则设置详解

Allegro是一个专业的PCB设计软件,具有强大的 Constraint Rules 设置功能,可以帮助设计师快速地实现PCB设计。以下是Allegro中的约束规则设置详解。

一、Physical(Line/vias)rule物理特性约束设置

物理特性约束设置是Allegro中的一个重要设置,用于控制PCB设计中的物理特性,例如线宽、过孔等。该设置可以分为三步:

1. “Setvalues”设置约束特征值:在该步骤中,设计师可以设置物理特性的默认值,例如线宽、过孔等。

2. “Attachproperty”绑定约束:在该步骤中,设计师可以将物理特性的约束绑定到具体的设计元素上,例如线路、元件等。

3. “Assignmenttable”约束规则分配:在该步骤中,设计师可以将物理特性的约束规则分配到具体的设计元素上,例如线路、元件等。

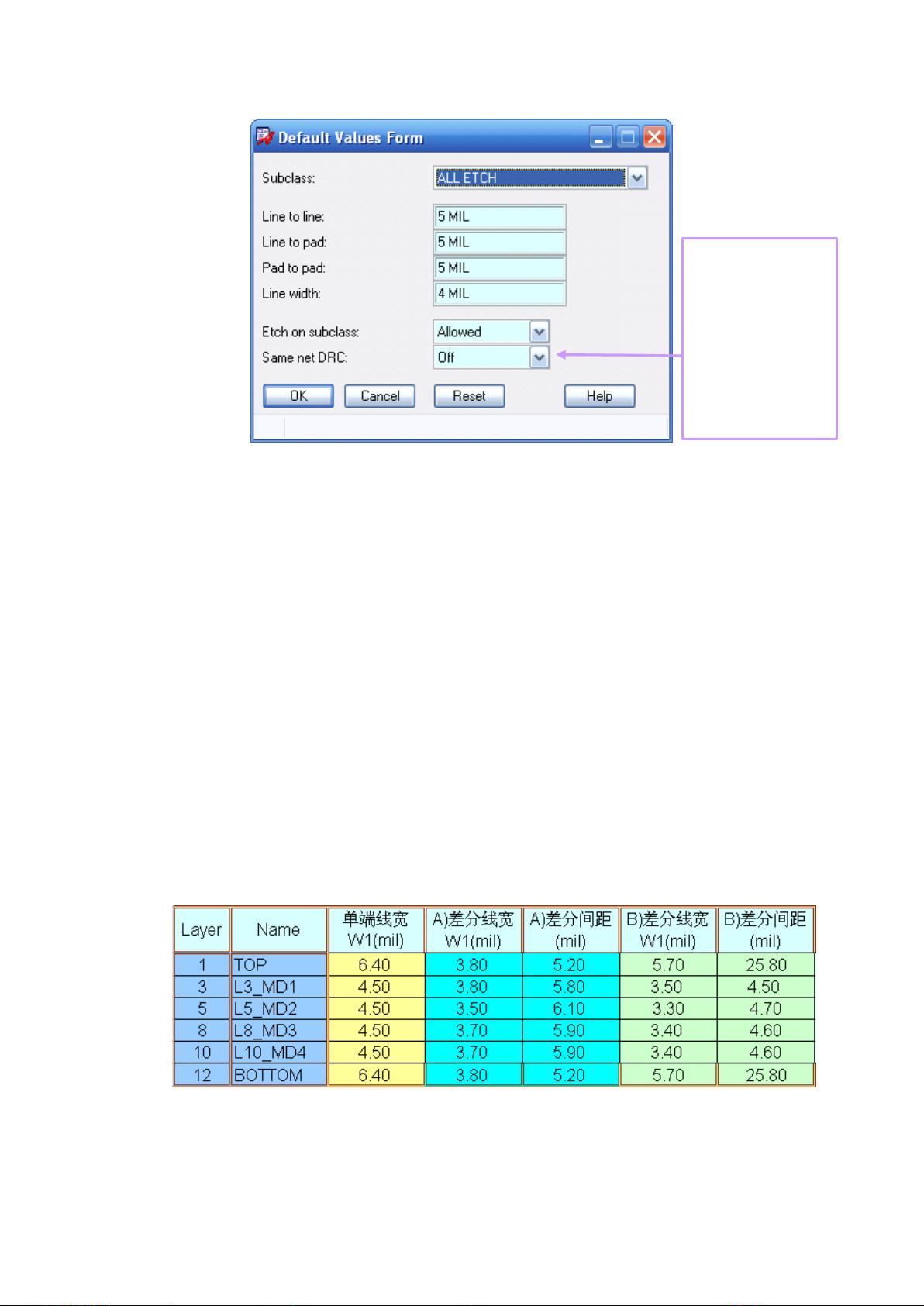

二、Spacing rule间距约束设置

间距约束设置是Allegro中的一个重要设置,用于控制PCB设计中的间距,例如线路之间的间距、元件之间的间距等。该设置可以分为三步:

1. “Setvalues”设置约束特征值:在该步骤中,设计师可以设置间距的默认值,例如线路之间的间距、元件之间的间距等。

2. “Attachproperty”绑定约束:在该步骤中,设计师可以将间距的约束绑定到具体的设计元素上,例如线路、元件等。

3. “Assignmenttable”约束规则分配:在该步骤中,设计师可以将间距的约束规则分配到具体的设计元素上,例如线路、元件等。

三、Constraint areas区域约束设置

区域约束设置是Allegro中的一个重要设置,用于控制PCB设计中的区域约束,例如走线长度、线宽等。该设置可以分为多步:

1. 区域约束设置:在该步骤中,设计师可以设置区域约束的默认值,例如走线长度、线宽等。

2. 线路长度设置:在该步骤中,设计师可以设置线路长度的约束规则,例如差分线等长设置、一组Net等长、XNet等长等。

四、Allegro中走线长度的设置

走线长度的设置是Allegro中的一个重要设置,用于控制PCB设计中的走线长度,例如差分线等长设置、一组Net等长、XNet等长等。该设置可以分为多步:

1. 差分线等长设置:在该步骤中,设计师可以设置差分线的等长约束规则。

2. 一组Net等长:在该步骤中,设计师可以设置一组Net的等长约束规则。

3. XNet等长:在该步骤中,设计师可以设置XNet的等长约束规则。

五、ConstraintsSys窗口设置

ConstraintsSys窗口是Allegro中的一个重要设置窗口,用于控制PCB设计中的约束规则设置。该窗口可以分为两个级别:

1. 第一级别:Standard design rules和Extended design rules。Standard design rules仅有一级分类,点击“Set standard values”设置默认约束值。

2. 第二级别:ConstraintsSys窗口分为多个tab页,例如Physical rule、Spacing rule、Constraint areas等,每个tab页都可以设置不同的约束规则。

Allegro中的约束规则设置是一个复杂的过程,需要设计师具备深入的PCB设计知识和Allegro操作经验。但是,通过详细的约束规则设置,设计师可以快速地实现PCB设计,提高设计效率和质量。

207 浏览量

435 浏览量

点击了解资源详情

207 浏览量

435 浏览量

2021-10-19 上传

261 浏览量

2021-10-19 上传

2021-10-19 上传

adolphzm

- 粉丝: 0

- 资源: 1