使用MAX+PLUSII设计8位全加器

“实验一用原理图输入法设计8位全加器,电信工程系通信072班谭正东的MAX+PLUSII设计项目”

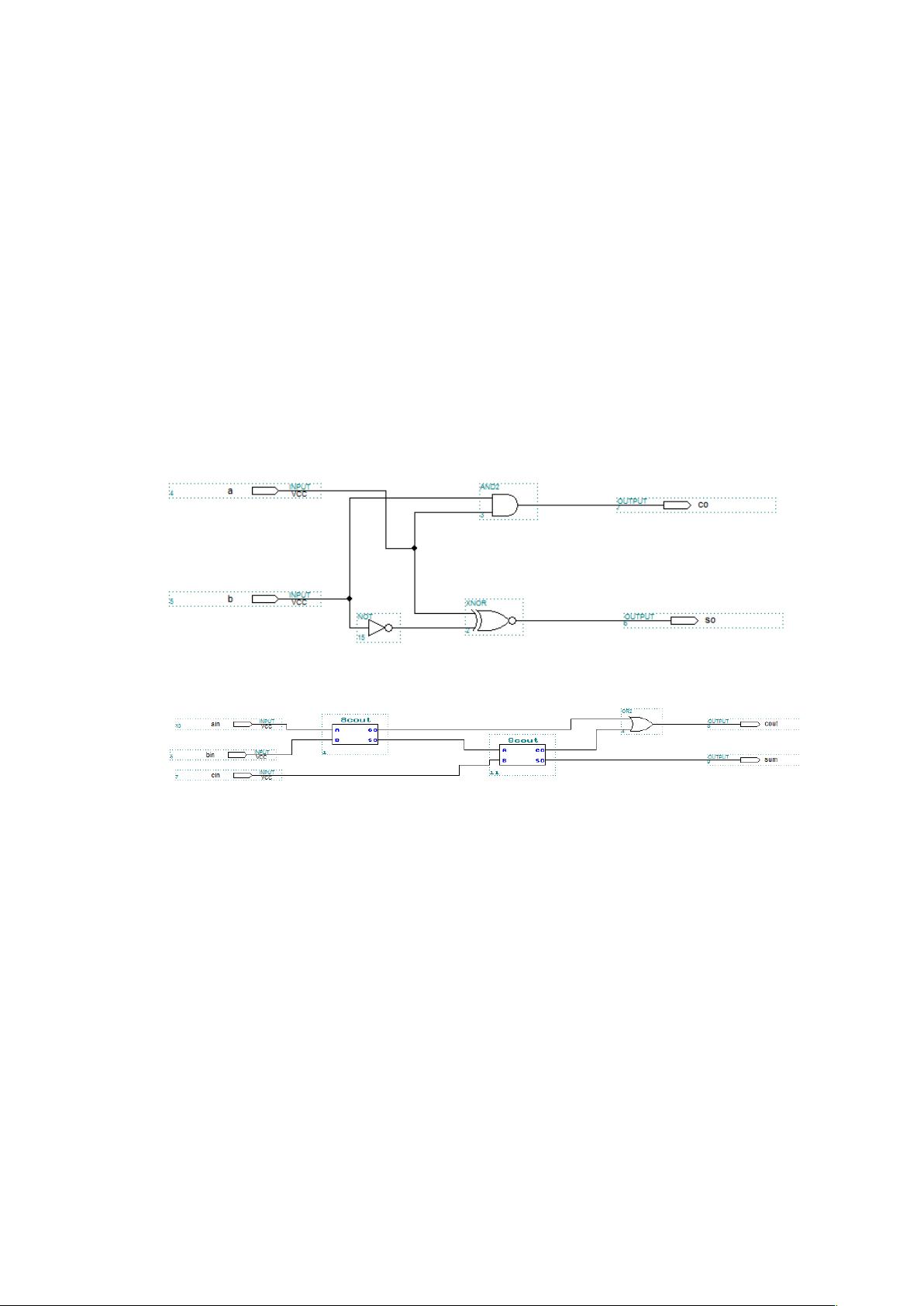

本文主要介绍了如何使用原理图输入法在MAX+PLUSII软件中设计一个8位全加器。8位全加器是数字逻辑电路中的基本组件,用于执行二进制数的加法运算。设计过程涉及了多个层次,从基本的半加器和全加器单元,到构建完整的8位全加器。

1. **全加器的结构**:

八位全加器由7个1位全加器和1个半加器组成。1位全加器能处理两个输入位(A和B)以及一个进位输入(cin),并产生两个输出:和(S)与进位输出(cout)。半加器仅处理两个输入位,没有进位输入,但仍有和与进位输出。在8位全加器中,低位的全加器的cout连接到高位全加器的cin,形成进位的串行传递。

2. **实验目标**:

- 熟悉MAX+PLUSII软件的原理图输入方法,用于设计简单的组合逻辑电路。

- 掌握层次化设计方法,通过8位全加器的设计实践了解电子线路设计的完整流程。

3. **实验原理**:

- 1位半加器和1位全加器的电路结构和工作原理。

- 通过串联连接7个1位全加器和1个半加器,实现8位全加器的进位逻辑。

4. **实验内容**:

- 设计并验证半加器和全加器的功能,包括绘制原理图、编译、综合、适配和仿真。

- 在更高层次上构建8位全加器,利用已设计的全加器和半加器元件,通过元件管脚的适当延长和重命名实现连接,简化原理图。

5. **实验步骤**:

- 启动MAX+PLUSII环境,创建新的编辑输入界面。

- 将设计文件设置为工程文件并保存,注意文件命名。

- 对工程文件进行编译,检查并修正可能的错误。

- 对无误的工程文件进行仿真,验证设计的正确性。

6. **实验结果**:

- 通过提供的图片,可以看到从半加器和全加器的仿真结果,到8位全加器的最终仿真输出,表明设计的全加器能够正确执行加法运算。

这个实验不仅锻炼了学生对数字逻辑电路的理解,还提升了他们使用EDA工具进行实际电路设计的能力。通过这样的实践,学生能够更好地理解和应用基本的数字逻辑概念,并为更复杂的数字系统设计打下基础。

相关推荐

tzd529585047

- 粉丝: 3

最新资源

- 计算机组成原理期末试题及答案(2011参考)

- 均值漂移算法深入解析及实践应用

- 掌握npm与yarn在React和pg库中的使用

- C++开发学生信息管理系统实现多功能查询

- 深入解析SIMATIC NET OPC服务器与PLC的S7连接技术

- 离心式水泵原理与Matlab仿真教程

- 实现JS星级评论打分与滑动提示效果

- VB.NET图书馆管理系统源码及程序发布

- C#实现程序A监控与自动启动机制

- 构建简易Android拨号功能的应用开发教程

- HTML技术在在线杂志中的应用

- 网页开发中的实用树形菜单插件应用

- 高压水清洗技术在储罐维修中的关键应用

- 流量计校正方法及操作指南

- WinCE系统下SD卡磁盘性能测试工具及代码解析

- ASP.NET学生管理系统的源码与数据库教程