基于DSP+CPLD结构的TMS320F2812硬件平台设计

14 浏览量

更新于2024-08-30

收藏 220KB PDF 举报

基于CPLD的TMS320F2812硬件平台设计

本篇文章介绍了基于CPLD的TMS320F2812硬件平台设计,系统采用DSP+CPLD结构,结合了DSP的数据运算能力和CPLD的高集成性、硬件可重编程性,设计过程更加合理、紧凑和简化。该系统经过扩展后可以应用在工业控制的多种场合,具有一定的实际参考价值。

1. CPLD在TMS320F2812系统中的应用

CPLD(Complex Programmable Logic Device)是一种高集成度、可编程的逻辑器件,具有高速度、低功耗、可重编程等特点。TMS320F2812数字信号处理器是基于F24X的高性能定点芯片,具有高性能的静态CMOS技术,高性能的32位中央处理器,高容量存储器,高速外设接口等特点。

2. TMS320F2812介绍

TMS320F2812数字信号处理器是一种高性能的定点芯片,具有以下特点:

* 采用高性能的静态CMOS技术,主频可以工作在150MHZ(时钟周期可达6.67ns)

* 高性能的32位中央处理器,可以进行16位X16位以及32位X32位的乘且累加操作

* 片内大容量存储器,128K×16bits的Flash和18K×16bits的数据/程序存储器

* 高速外设接口,最多可扩展1.5M×16bit存储器

* 3个32-bitCPU定时器,其中CPU定时器1和CPU定时器2被保留用作实时操作系统OS。CPU定时器0可供用户使用,作为独立的,全局性的定时中断控制

* 具有12-bit的ADC流水线变换时间最小60ns,单变换200ns;可选择两个时间管理器触发功能

* 改进的eCAN2.0B接口模块

* 多种串行通信接口(2个UART、1个SPI及1个MCBSP)

* 高性能低功耗,采用1.8V内核电压和3.3V外围接口电压

3. 硬件结构介绍

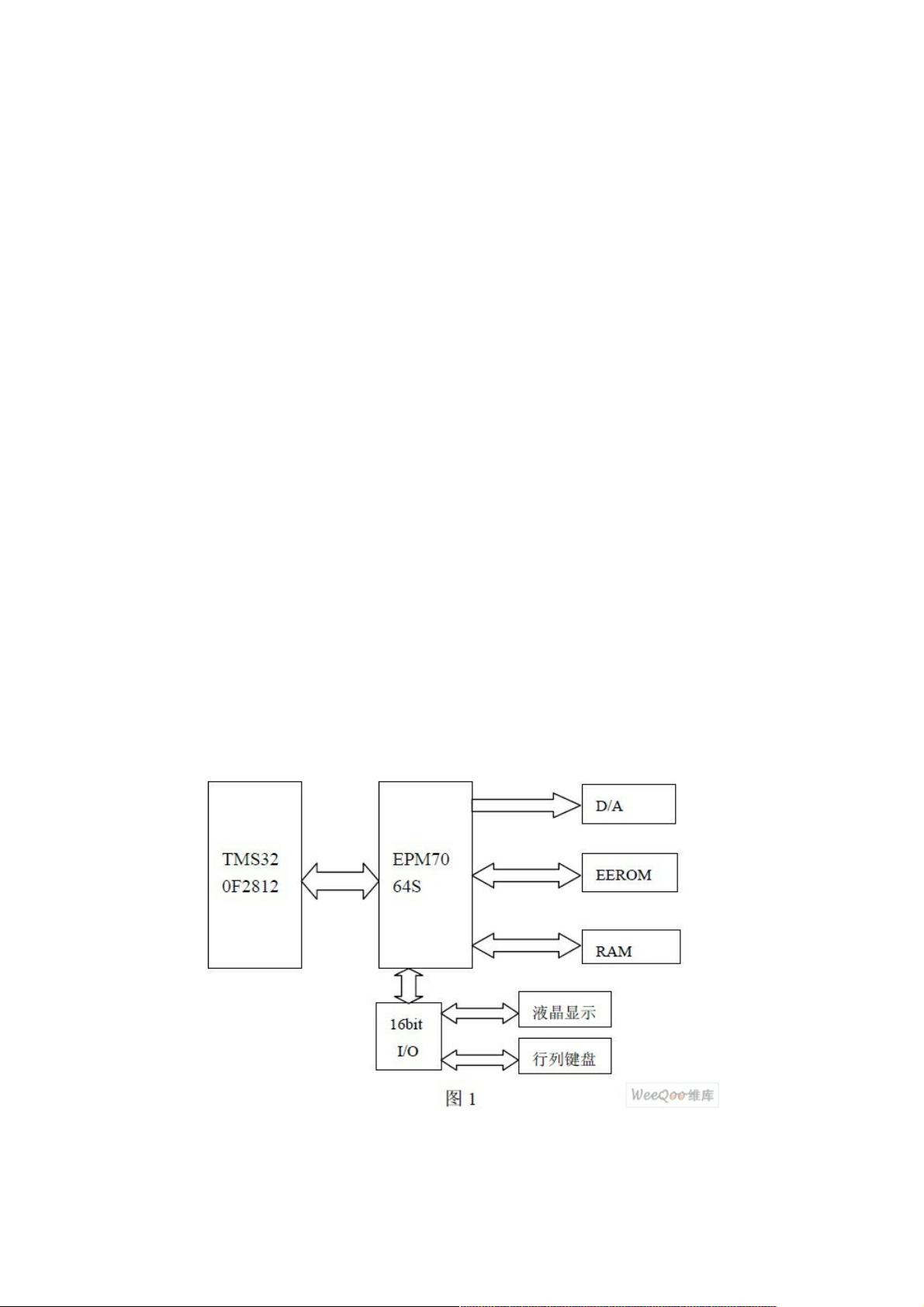

TMS320F2812应用系统需要外扩一些必要的电路,包括支持内部程序运行的RAM和EEROM,以及D/A转换电路等。系统结构框图如图1所示。

4. 数模转换器的应用

在TMS320F2812中,片外扩展是通过TMS320F2812中的外设接口XINTF来实现的。它类似于C240X的外部接口,但也做了改进:

* 在C240X中,程序存储空间、数据存储空间和I/O空间映射在相同的地址(0000~FFFF),对它们的访问通过控制线(DS,PS,IS)来区分;而在F2812中,外部存储器接口分成了5个固定的存储映像区域,可寻址1MB的片外存储器空间,具有独立的地址,没有了控制线(DS,PS,IS)。

本系统设计采用CPLD和DSP的结合,具有高集成性、可重编程性和高性能的特点,能够应用在工业控制的多种场合,具有一定的实际参考价值。

134 浏览量

点击了解资源详情

194 浏览量

2020-11-02 上传

2021-02-03 上传

127 浏览量

2020-07-25 上传

2020-10-24 上传

333 浏览量

weixin_38725625

- 粉丝: 3

- 资源: 919

最新资源

- Gdal 2.2.2 for .Net And .NetCore

- 微生物肥料项目计划书.zip

- mhygepdf:多元超几何概率密度函数。-matlab开发

- 寄存器查看工具,十六进制,十进制显示二进制值

- EchartConvert:图表生成

- gestionStudent

- Typersion:最好的打字练习游戏! 在免费游戏和冒险模式之间进行选择,后者是一种rpg式的砍杀模式,目标是达到第100阶段! 每五个阶段都会受到迷你小老板的挑战,在您面对越来越强的敌人时提高打字速度!

- 联体别墅设计施工图

- CUDA MEX:在 MATLAB 中编译 CUDA! 只需编写 cuda_mex filename.cu 就可以了。-matlab开发

- redisclient-win32.x86.2.0.rar

- PRNICT:硬件

- Platzi徽章

- MySQL-python-1.2.5-cp27-none-win-amd64.whl的zip安装包

- 两款css+html打造的超炫酷的网站在线客服代码,鼠标划过可以弹出在线客服窗口

- SDL2 i.MX6ULL移植包

- 基于vue2.0实现的滑动进度条