Σ-ΔA/D转换器数字抽取滤波器设计与优化

191 浏览量

更新于2024-08-31

收藏 381KB PDF 举报

"设计了一种应用于Σ-ΔA/D转换器的数字抽取滤波器,通过梳状滤波器和半带滤波器级联的结构实现,具有降低功耗和复杂度的效果,同时提供了98dB的信噪比,满足高精度转换需求。"

在Σ-Δ模数转换器(Σ-Δ A/D Converter)的设计中,数字抽取滤波器扮演着至关重要的角色。这种转换器通常采用过采样技术,通过调制器和数字滤波器两部分来提高信号处理的精度。过采样技术可以将量化噪声移到信号带宽之外,并通过数字滤波器进一步降低,最终实现高分辨率的转换。

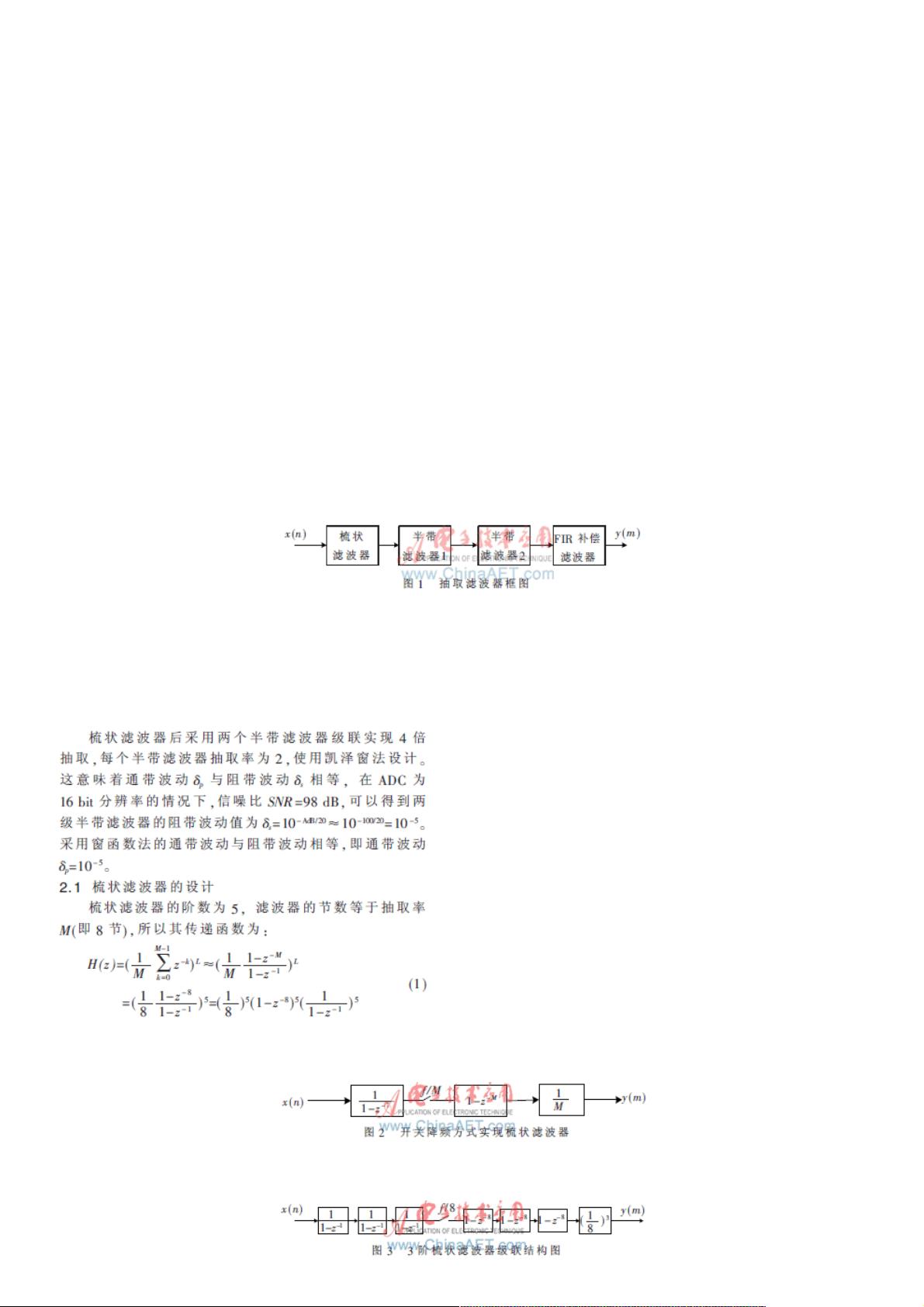

数字抽取滤波器的主要任务包括噪声整形、降频和数据编码。在本设计中,滤波器采用了多级结构,具体由梳状滤波器和半带滤波器级联组成。梳状滤波器利用开关降频和流水线级联方式,有效地降低了系统的功耗和复杂性。其独特的结构使得输入频率与过渡带宽的比例减小,减少了所需的滤波器系数,简化了设计。

半带滤波器则采用了多相结构,这可以将数据量减少约50%,进一步优化了计算效率。半带滤波器特别适合用于降频过程,但由于其较宽的过渡带,可能会影响通带内的幅度,因此在设计中通常会配合其他滤波器进行补偿。

在过采样率为32的情况下,数字抽取滤波器执行32:1的降频操作。第一级通常采用梳状滤波器,利用其窄带特性,随后的各级则采用半带滤波器,以逐步完成降频和信号整形。在最后,为了弥补可能的幅度损失和保证通带性能,可以使用一个FIR滤波器进行校正。

在实际设计和仿真过程中,滤波器的目标是减少运算量和存储需求,同时确保足够的信噪比。本设计中的抽取滤波器达到了98dB的信噪比,这完全符合高精度A/D转换器的要求,能够提供高质量的数字输出。

这种数字抽取滤波器设计体现了在保证转换精度的同时,对系统复杂性和功耗的有效控制,是Σ-Δ模数转换器设计中的一个重要创新。通过合理的滤波器结构组合,实现了高效且高性能的信号处理,对于现代电子设备中的高精度数据转换具有广泛的应用前景。

2021-04-16 上传

2020-10-22 上传

点击了解资源详情

点击了解资源详情

2021-01-20 上传

2021-02-20 上传

点击了解资源详情

2009-06-08 上传

2020-07-18 上传

weixin_38652636

- 粉丝: 6

- 资源: 896

最新资源

- StarModAPI: StarMade 模组开发的Java API工具包

- PHP疫情上报管理系统开发与数据库实现详解

- 中秋节特献:明月祝福Flash动画素材

- Java GUI界面RPi-kee_Pilot:RPi-kee专用控制工具

- 电脑端APK信息提取工具APK Messenger功能介绍

- 探索矩阵连乘算法在C++中的应用

- Airflow教程:入门到工作流程创建

- MIP在Matlab中实现黑白图像处理的开源解决方案

- 图像切割感知分组框架:Matlab中的PG-framework实现

- 计算机科学中的经典算法与应用场景解析

- MiniZinc 编译器:高效解决离散优化问题

- MATLAB工具用于测量静态接触角的开源代码解析

- Python网络服务器项目合作指南

- 使用Matlab实现基础水族馆鱼类跟踪的代码解析

- vagga:基于Rust的用户空间容器化开发工具

- PPAP: 多语言支持的PHP邮政地址解析器项目