华为VHDL同步设计实践与技巧

需积分: 10 195 浏览量

更新于2024-07-18

收藏 1.05MB PDF 举报

"华为VHDL设计风格和实现"

在电子设计自动化(EDA)领域,VHDL(Very High-Speed Integrated Circuit Hardware Description Language)是一种广泛使用的硬件描述语言,用于描述数字系统的逻辑功能。华为作为全球领先的ICT解决方案提供商,其在VHDL设计方面也积累了丰富的经验和规范。本资料主要探讨了华为在VHDL设计中推崇的风格和实现方法,旨在为IC设计工程师提供指导。

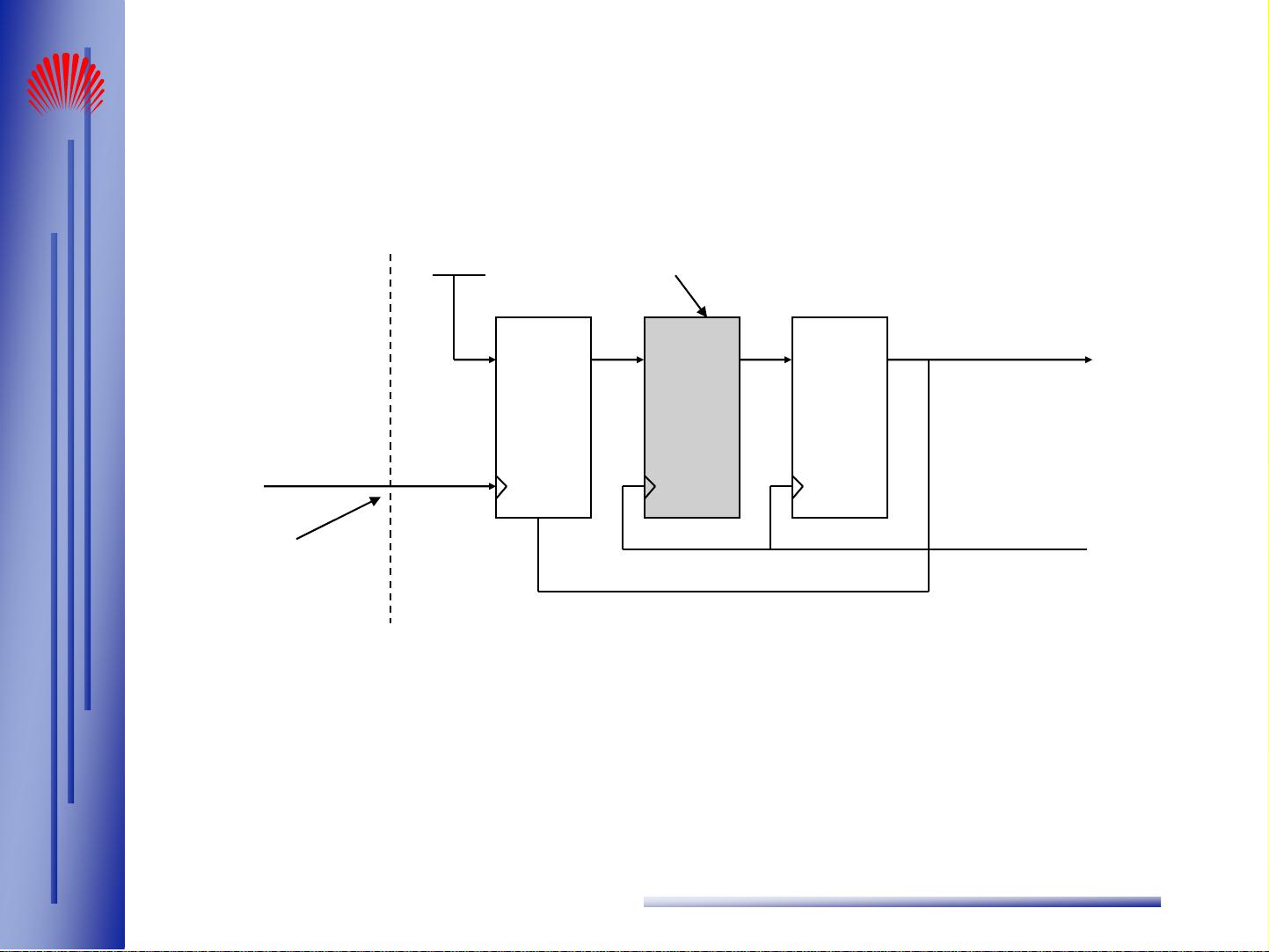

1. **同步设计**

同步设计是VHDL设计的核心原则,它确保数据在不同逻辑单元之间的传递通过统一的时钟信号同步。这样可以避免数据采样错误,提高系统稳定性。同步设计的优势在于减少了因时钟不同步而产生的数据竞争和不确定性,降低了设计的复杂性和风险。

异步设计虽然在某些情况下可能简化逻辑,但其不稳定性和潜在的数据错误使得同步设计成为首选。在同步设计中,应避免将组合逻辑产生的信号用作时钟、异步复位/置位,以减少毛刺和不确定性的影响。

2. **速度与效率**

在VHDL设计中,速度是一个重要的考量因素。设计应尽可能优化以满足时延要求,确保下游逻辑单元能正确采样到上游数据。这通常涉及到逻辑优化、时钟树综合和布线等方面的考虑。

3. **资源利用**

在有限的硬件资源下,高效地利用FPGA或ASIC上的逻辑资源至关重要。设计者需要考虑如何在满足功能和性能要求的同时,减少门级逻辑的数量,降低功耗,提升设计的面积效率。

4. **其他设计原则**

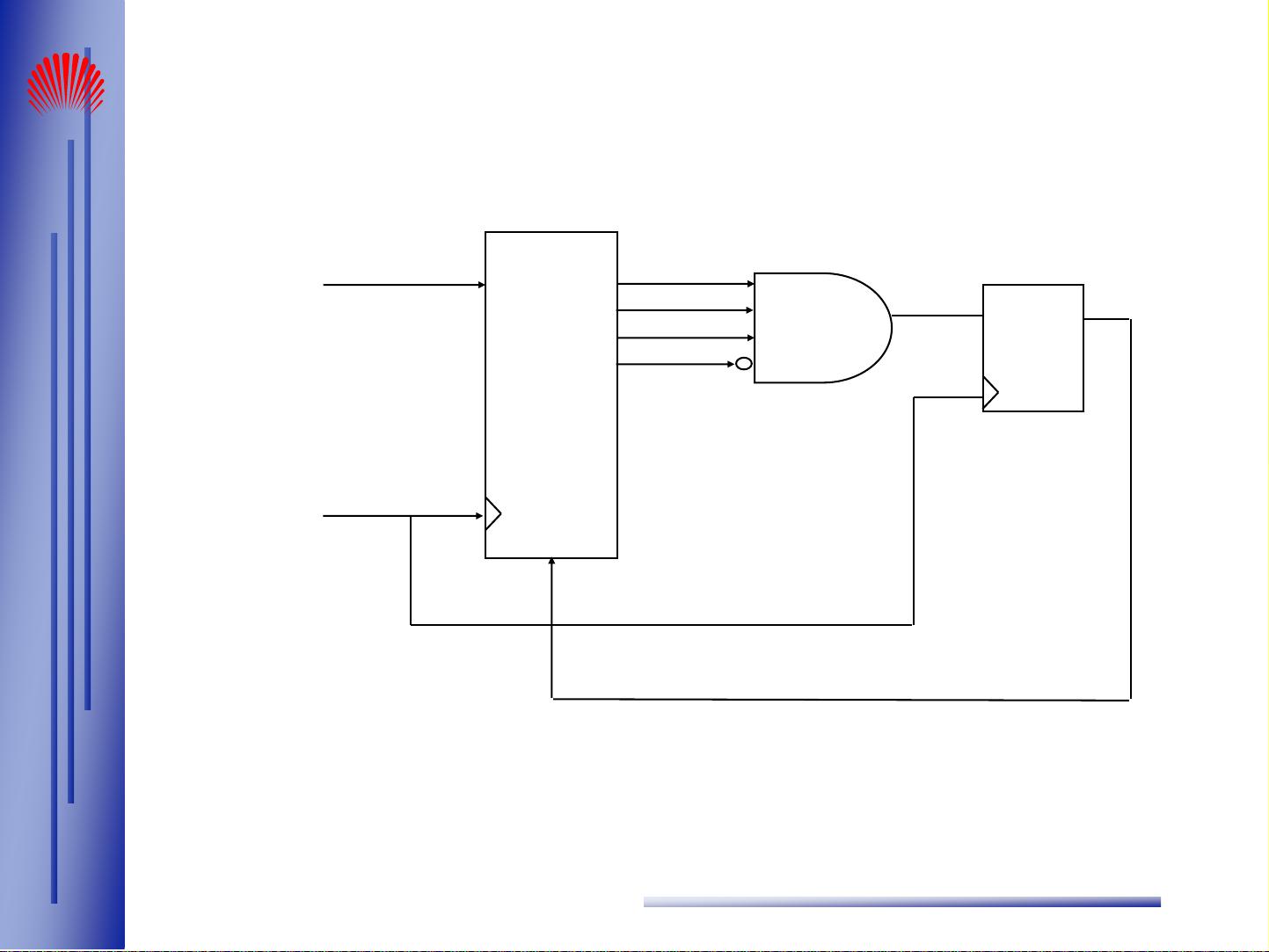

- **时钟管理**:时钟信号的质量直接影响设计的稳定性,应避免时钟路径中的延迟不匹配和毛刺。

- **复位和置位信号**:异步复位/置位信号可能引入毛刺,设计时需确保这些信号的同步处理,以防止逻辑错误。

- **触发器的使用**:在高速设计中,触发器对非常窄的毛刺信号敏感,设计时应考虑消除这些潜在问题。

- **测试和验证**:通过时间仿真进行设计验证是必要的,但实际应用中还需要考虑上板调试,因为异步设计可能在仿真中表现良好但在实际系统中出现问题。

5. **VHDL代码示例**

提供的VHDL代码片段展示了如何避免使用组合逻辑产生的时钟信号,例如通过使用边沿触发的D触发器来捕获无毛刺的时钟,以确保寄存器的正确操作。

华为的VHDL设计风格强调了同步设计的稳定性和可预测性,同时也关注设计的效率和资源利用率。理解和遵循这些设计原则,有助于提高数字系统的可靠性和可维护性。

2010-01-26 上传

2011-06-06 上传

2020-07-14 上传

点击了解资源详情

点击了解资源详情

2019-08-28 上传

2010-10-02 上传

2009-03-31 上传

2024-04-24 上传

suifanchang

- 粉丝: 1

- 资源: 13

最新资源

- 新型智能电加热器:触摸感应与自动温控技术

- 社区物流信息管理系统的毕业设计实现

- VB门诊管理系统设计与实现(附论文与源代码)

- 剪叉式高空作业平台稳定性研究与创新设计

- DAMA CDGA考试必备:真题模拟及章节重点解析

- TaskExplorer:全新升级的系统监控与任务管理工具

- 新型碎纸机进纸间隙调整技术解析

- 有腿移动机器人动作教学与技术存储介质的研究

- 基于遗传算法优化的RBF神经网络分析工具

- Visual Basic入门教程完整版PDF下载

- 海洋岸滩保洁与垃圾清运服务招标文件公示

- 触摸屏测量仪器与粘度测定方法

- PSO多目标优化问题求解代码详解

- 有机硅组合物及差异剥离纸或膜技术分析

- Win10快速关机技巧:去除关机阻止功能

- 创新打印机设计:速释打印头与压纸辊安装拆卸便捷性