TMS320F280x DSP系列芯片详解

需积分: 9 82 浏览量

更新于2024-07-24

收藏 1.78MB PDF 举报

"DSP2802原装芯片资料,包括TMS320F2809、TMS320F2808、TMS320F2806、TMS320F2802等系列DSP的硬件设置与应用介绍。"

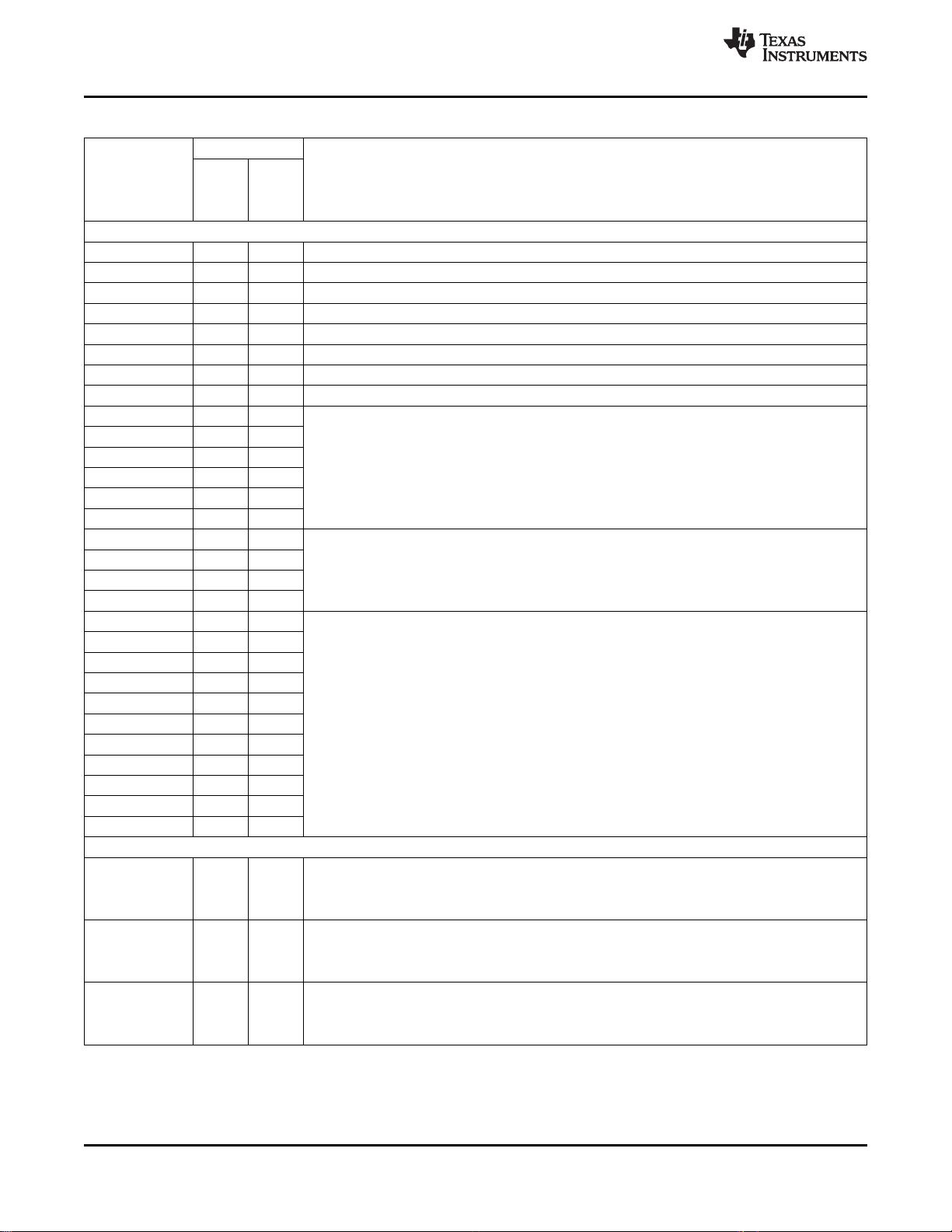

TMS320F2802是德州仪器(Texas Instruments, TI)推出的一款数字信号处理器(DSP),属于C28x家族,该系列芯片在工业控制、自动化、通信等领域有广泛应用。文档提供的信息主要涵盖以下几个方面:

1. **产品规格与特性**:

DSP280x系列芯片具备高性能计算能力,适用于实时信号处理。其特性可能包括高速浮点运算、低功耗、丰富的外设接口以及高效能的内存架构。具体到TMS320F2802,它可能拥有特定的性能指标,如工作频率、I/O端口数量、内存大小等,但这些信息在摘要中未直接给出。

2. **开始使用**:

开始使用这部分通常会介绍如何初始化芯片,包括上电设置、复位电路设计、时钟配置等基本步骤,以确保芯片能够正常运行。

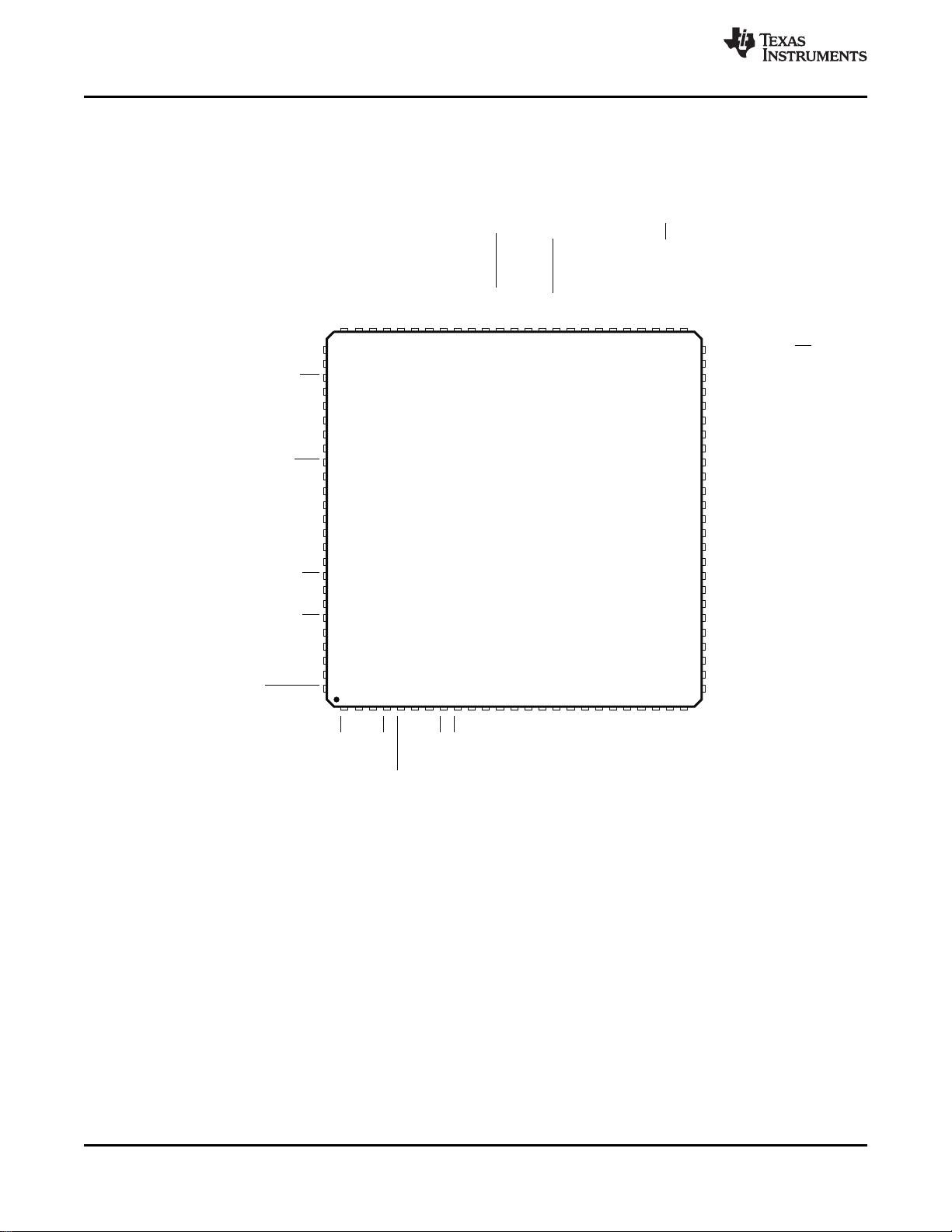

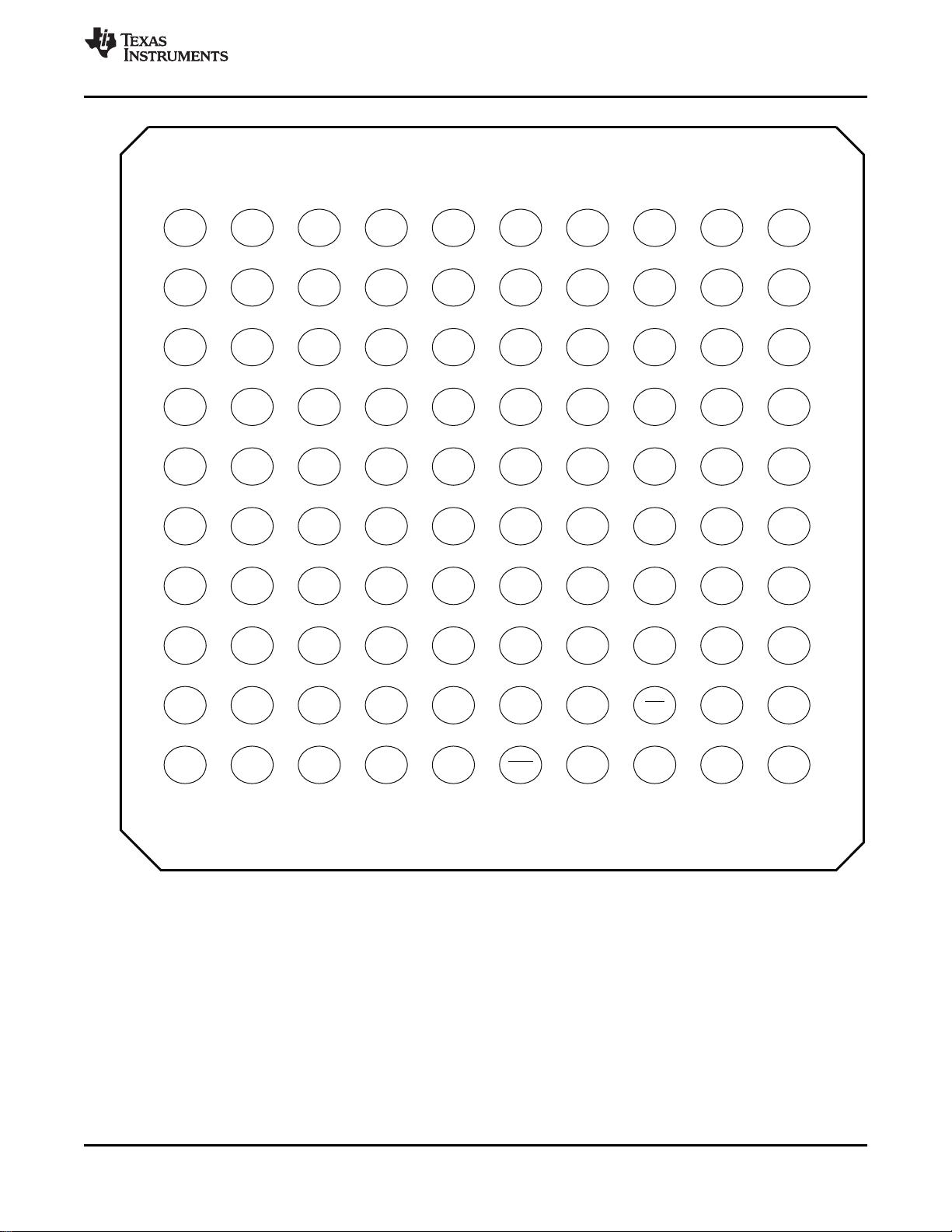

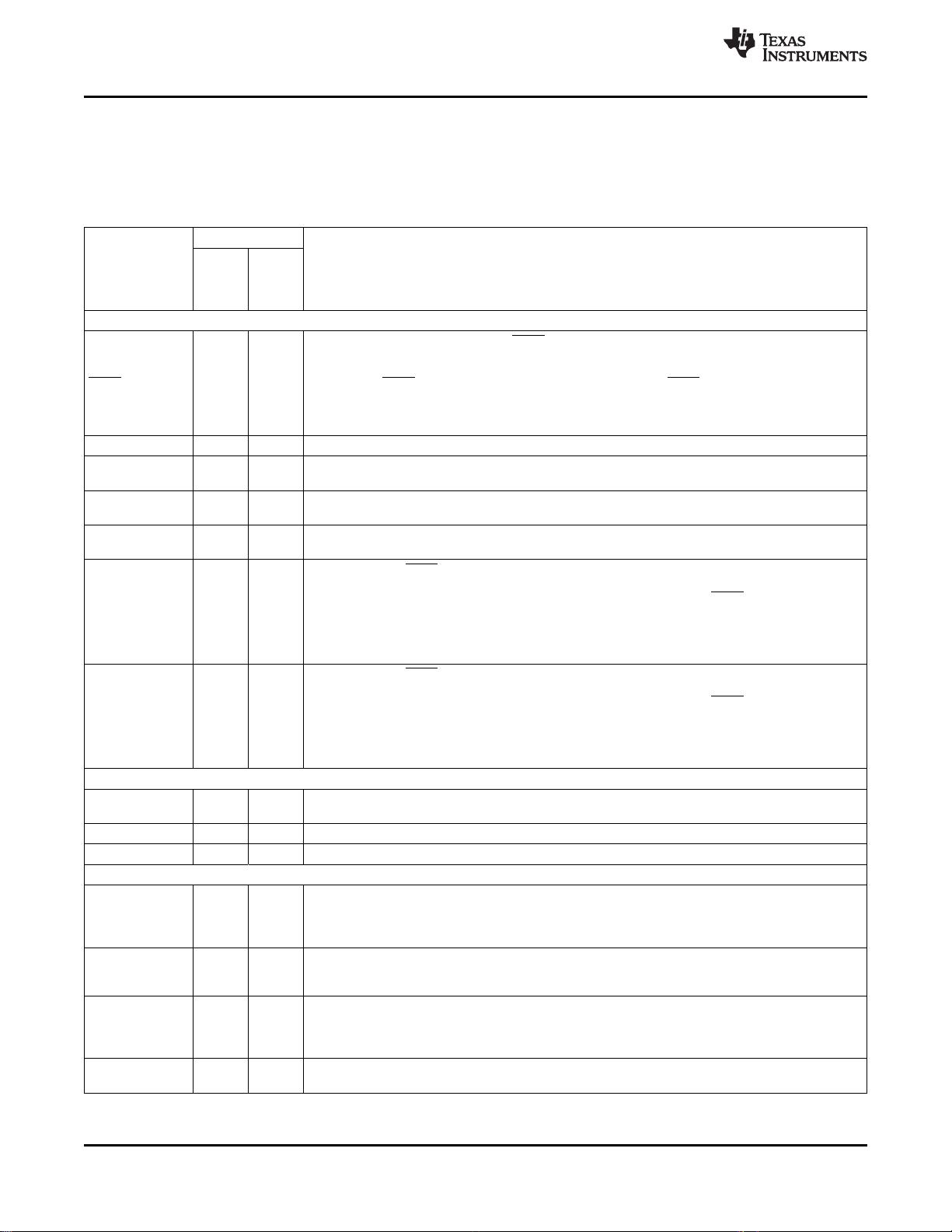

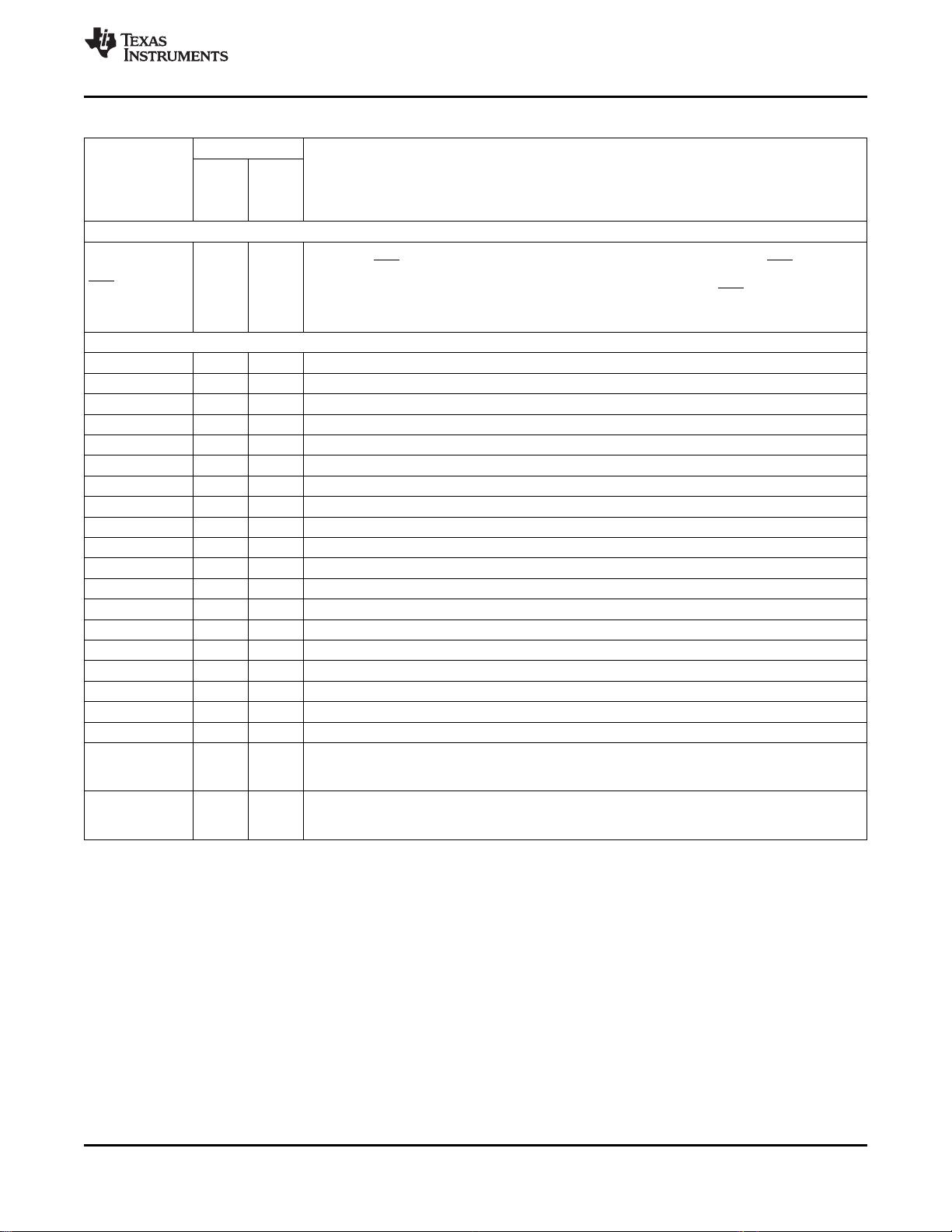

3. **引脚分配与信号说明**:

引脚分配部分详细列出了每个引脚的功能,这对于硬件设计至关重要,因为它决定了如何连接外部电路。信号说明则解释了每个信号的作用,帮助理解系统如何与外界交互。

4. **功能概述**:

这部分深入讨论了芯片的内部结构和功能模块。例如,C28x CPU是核心处理单元,执行指令并控制整个系统;内存总线和外设总线构成了哈佛架构,分别用于数据和控制信号的传输;实时JTAG和分析接口用于调试和性能评估;闪存存储程序代码,而SARAM(静态RAM)用于数据存储和运行时工作空间;引导ROM用于加载启动程序;安全性可能涉及加密和保护机制;PIE(Peripheral Interrupt Expansion)块扩展了中断处理能力;外部中断和振荡器/PLL则负责系统时钟管理和响应外部事件;安全设备确保芯片在异常情况下的稳定运行;外设时钟为各个外设提供独立的时序;低功率模式则是为了节省能源。

5. **硬件设置**:

对于DSP2802,硬件设置包括但不限于电源管理、时钟配置、中断设置、外设接口配置等。这些设置直接影响到系统的性能和稳定性,需要根据具体应用进行优化。

6. **应用**:

虽然摘要没有提供具体的应用案例,但DSP2802系列常用于电机控制、电源转换、通信解调、图像处理等场合,其强大的计算能力和实时性使得它成为许多复杂系统的关键组件。

以上信息是基于摘要内容推测的,实际的DSP2802资料应包含更详细的技术参数、编程指南、示例代码和应用实例,以帮助开发者充分利用这款芯片的能力。对于需要深入研究或开发基于TMS320F2802系统的人来说,这份资料将是不可或缺的参考。

385 浏览量

179 浏览量

350 浏览量

117 浏览量

2024-12-10 上传

198 浏览量

531 浏览量

feiying_2189

- 粉丝: 0

最新资源

- 西北工业大学卢京潮《自动控制原理》答案解析

- 国际酒店预订HTML网站模板介绍

- 体验更快速清洁的PC:Advanced SystemCare 10 Beta版

- 汽车美容店管理系统:毕业设计与数据库整合

- Tesseract Docker教程:构建古希腊语OCR训练数据

- 探索Android全景图片实现与openGL技术

- 测试文件下载中的空字节与模式检查

- SearchBar-crx插件:Chrome浏览器下的高效搜索工具

- Win98与Win2000桌面透明效果教程

- iOS自定义TabBar实现上下联动导航

- 51单片机常用函数集及其驱动实现

- 中科大834软件工程历年考研真题解析(1995-2016)

- Bootstrap遮罩层实现方法详解

- 掌握PopupViewController:实现视图控制器的覆盖与弹出

- 酷Q机器人软件深度解析:群管理与自动聊天功能

- 提升效率的Qwik Search-crx插件:快速切换搜索引擎