5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

H

:

Enable(DEFAULT)

L

:

Disable

DSWODVREN - On Die DSW VR Enable

*

Note: SUSACK# and SUSWARN# can be tied together if

EC does not want to involve in the handshake mechanism

for the Deep Sleep state entry and exit

CAN be NC ,if not support Deep Sx

DPWROK: Tired toghter with RSMRST#

that do not support Deep Sx

ELPIDA EDJ4216EFBG-GN-F

0

ELPIDA EDJ8416E6MB-GN-F

0

1

0

0M

ICRON MT41K256M16HA-125:E

RAM_ID1 RAM_ID0

RAM P/N

01

11

SAMSUNG K4B4G1646Q-HYK0

HYNIX H5TC4G63AFR-PBA

0

RAM_ID2

0

0

0

0

0

0

0

1

1

0

1

0

1

0

1

1

1

0

1

0

1

1

0

1

0

1

0

1

0

1

0

0

00

SAMSUNG K4B8G1646Q-MYK0

0

MICRON MT41K512M16TNA-125:E

00

TBD1

GPIO59

1

1

GPIO58

1

GPIO57

GPIO56

11

1

1

11

1

1

1

00

01

RAM_ID3

TBD

TBD

TBD

TBD

TBD

TBD

HYNIX H5TC8G63AMR-PBA

1: Intel ME TLS with confidentiality

GPIO15 : TLS Confidentiality

0: Intel ME TLS with no confidentiality

*

(Have internal PD)

GSPI0_MOSI / GPIO86 : Boot BIOS Strap

1: LPC BUS

(Have internal PD)

*

0: SPI BUS

SDIO_D0 / GPIO66 : Top-Block Swap Override

0: DISABLED

1: ENABLED

*

(Have internal PD)

DPWROK can be tied to RSMRST# for platforms

that do not support the Deep Sx state.

10K,3VS

@10K,3VS XDP

10K,+3VALW_PCH

10K,+3VALW_PCH

@10K,+3VALW_PCH

@10K,+3VALW_PCH

10K,3VS

1K,+3VALW_PCH

10K,3VS

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,3VS

10K,3VS

@1K,+3VALW_PCH

10K,3VS

10K,3VS

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,3VS

10K,3VS

10K,3VS

10K,+3VALW_PCH10K,+3VALW_PCH

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,+3VALW_PCH

10K,3VS

10K,3VS@10K,3VS

10K,3VS

@10K,3VS

10K,3VS

10K,3VS

10K,3VS

10K,3VS

10K,3VS

10K,3VS

10K,3VS

10K,3VS

DDR_ID

PU 10K to +3VALW_PCH (DDR3L)

PU down 10K (LP-DDR3)

ESD

ESD

ESD

ESD

ESD

06/30, RC130~RC133 change value to 2.2K ohm

MT41K256M16LY-107

07/07, change to mount

08/21, change to unpop

08/21, change to unpop

08/21, change to unpop

08/21, change to unpop

08/21, change to unpop

08/18, change to mount

H_

PLT_RST#

PM

_SLP_S5#

SY

S_PWROK

SU

SACK#_R

SY

S_RESET#

AP

WROK_R

PC

H_PWROK

EC

_RSMRST#

PC

H_GPIO30

PBT

N_OUT#

AC

_PRESENT

PC

H_GPIO72

DS

WODVREN

DP

WROK

PC

H_PCIE_WAKE#

H_

PLT_RST#

SL

P_S0_N

PCH_GPIO29

AC

_PRESENT

PC

H_GPIO32

PC

H_GPIO61

PM

_SLP_S3#

PM

_SLP_A#

PM

_SLP_S4#

SLP_LAN_N

SL

P_SUS_N

PCH_GPIO76

PC

H_GPIO24

PC

H_GPIO49

PC

H_GPIO13

PC

H_GPIO25

SENSOR_HUB_RST#

RA

M_ID2

RA

M_ID0

RA

M_ID3

RA

M_ID1

PC

H_GPIO8

PC

H_GPIO48

PC

H_GPIO12

PC

H_GPIO15

SPKR

EC

_SCI#

SEN

SOR_HUB_INT#_R

PC

H_GPIO27

PC

H_GPIO28

PC

H_GPIO26

PCH_GPIO17

PC

H_GPIO16

PC

H_GPIO9

PC

H_GPIO10

PCH_GPIO71

H_

THERMTRIP#

SER

IRQ

PC

H_OPIRCOMP

PC

H_GPIO32

EC_SCI#

PCH_GPIO33

SER

IRQ

KB_

RST#

PCH_GPIO48

PC

H_GPIO65

PC

H_GPIO67

PCH_GPIO71

PCH_GPIO16

PCH_GPIO61

PCH_GPIO13

PCH_GPIO30

PCH_GPIO9

PCH_GPIO10

PCH_GPIO72

RAM_ID2RAM_ID3 RAM_ID1 RAM_ID0

PC

H_GPIO15

PC

H_GPIO86

EC

_RSMRST#

PCH_GPIO83

PC

H_GPIO87

PC

H_GPIO86

PC

H_GPIO65

PC

H_GPIO66

PC

H_GPIO67

I2

C1 _SDA_T P

I2

C1 _SCL _TP

I2C 0_SD A_ SEN

I2C 0_SC L_SEN

I2

C0 _SDA_SEN

I2

C0 _SCL _SEN

I2

C1 _SDA_T P

I2

C1 _SCL _TP

PC

H_GPIO38

PCH_GPIO17

PCH_PCIE_WAKE#

PCH_GPIO76

PCH_GPIO8

PCH_GPIO12

PCH_GPIO28

PCH_GPIO49

PC

H_GPIO50

PCH_GPIO25

SENSOR_HUB_RST#

SPKR

PCH_GPIO83

PC

H_GPIO33

PC

H_GPIO38

PC

H_GPIO66

PC

H_GPIO84

PC

H_GPIO85

PCH_GPIO88

PC

H_GPIO89

PC

H_GPIO90

PC

H_GPIO91

PC

H_GPIO92

PCH_GPIO93

PC

H_GPIO94

PC

H_GPIO0

PC

H_GPIO1

PC

H_GPIO2

PCH_GPIO3

PC

H_GPIO84

PC

H_GPIO85

PC

H_GPIO89

PC

H_GPIO90

PC

H_GPIO91

PC

H_GPIO92

PCH_GPIO93

PC

H_GPIO94

PC

H_GPIO1

PC

H_GPIO0

PC

H_GPIO3

PC

H_GPIO2

PCH_GPIO64

PC

H_GPIO68

PCH_GPIO69

PC

H_GPIO68

PC

H_GPIO69

PC

H_GPIO64

SENSOR_HUB_INT#_R

PCH_GPIO27

PCH_GPIO44

PCH_GPIO29

PCH_GPIO44

DDR_

ID

PCH_GPIO50

PC

H_GPIO45

PCH_GPIO45

PCH_GPIO70

PCH_GPIO70

DDR_ID

H_

PLT_RST#

PC

H_PWROK

H_

THERMTRIP#

EC

_RSMRST#

SY

S_RESET#

PCH_GPIO87

SY

S_RESET#

PCH_GPIO26

PCH_GPIO24

EC

_RSMRST#[17]

PM

_SLP_S5# [17]

SY

S_PWROK[17,4]

PC

H_PWROK[17]

PBT

N_OUT#[17]

AC

_PRESENT[17]

SU

SCLK_WLAN [19]

PL

T_RST# [17,19]

PM

_SLP_S3# [17]

PM

_SLP_S4# [17]

SPKR[1

5]

EC

_SCI#[17]

NG

FF_SSD_PRESENT#[18]

SERIRQ [17]

KB_

RST# [17]

PC

IECLKREQ2_N [6]

WL

AN_CLKREQ# [19,6]

PCH_GPIO54 [4]

PCH_GPIO37 [6]

PC

H_GPIO51 [4]

PC

H_GPIO78 [4]

PC

IECLKREQ5_N [6]

PC

IECLKREQ0_N [6]

PC

H_GPIO36 [6]

PC

IECLKREQ1_N [6]

PC

IECLKREQ4_N [6]

PC

H_GPIO53 [4]

PCH_SATALED# [6]

PCH_GPIO34 [6]

PCH_GPIO60 [7]

PCH_GPIO73 [7]

PCH_GPIO11 [7]

I2

C0 _SCL _SEN [16 ]

I2

C0 _SDA_SEN [16]

I2

C1 _SCL _TP [23]

I2

C1 _SDA_T P [23]

PC

H_GPIO77 [4]

PC

H_GPIO79 [4]

BT_OFF# [19,4]

SEN

SOR_HUB_INT#[16,4]

DE

VSLP1[18]

PC

H_GPIO52 [4]

SENSOR_HUB_RST#[16]

+R

TCVCC

+3

VS

+3

VALW_PCH

+1

.05VS_VTT

+3

VS

+3VALW_PCH

+3VALW_PCH

+3VS

+3VALW_PCH

+3VALW_PCH+3VALW_PCH +3VALW_PCH +3VALW_PCH

+3VS

+3VALW_PCH

+3

VS

+3VS

+3

VS

Title

Size Document Number Rev

Date: Sheet of

Se

curity Classification

Co

mpal Secret Data

TH

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Is

sued Date

De

ciphered Date

LA

-B921PR10

1.0

P0

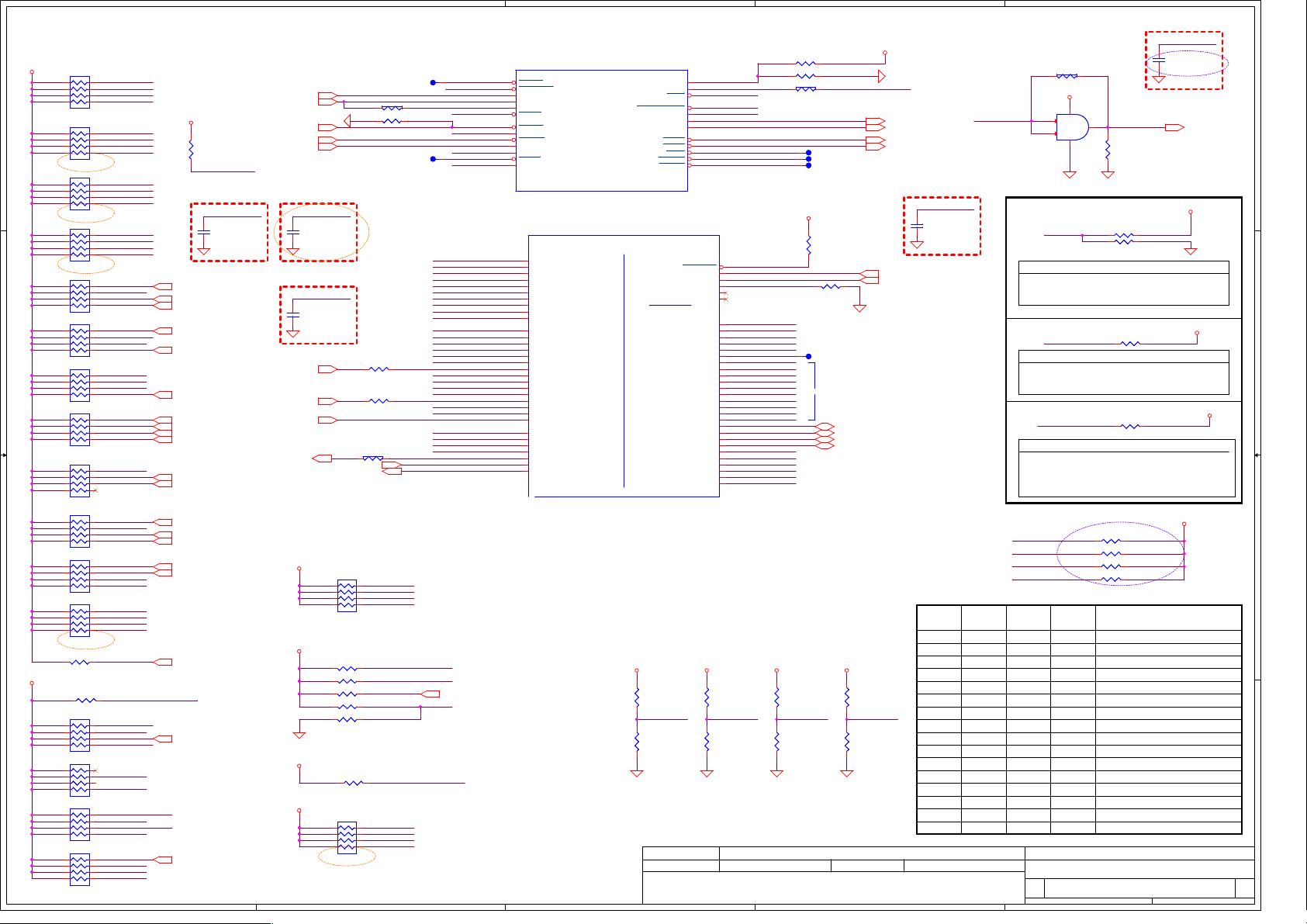

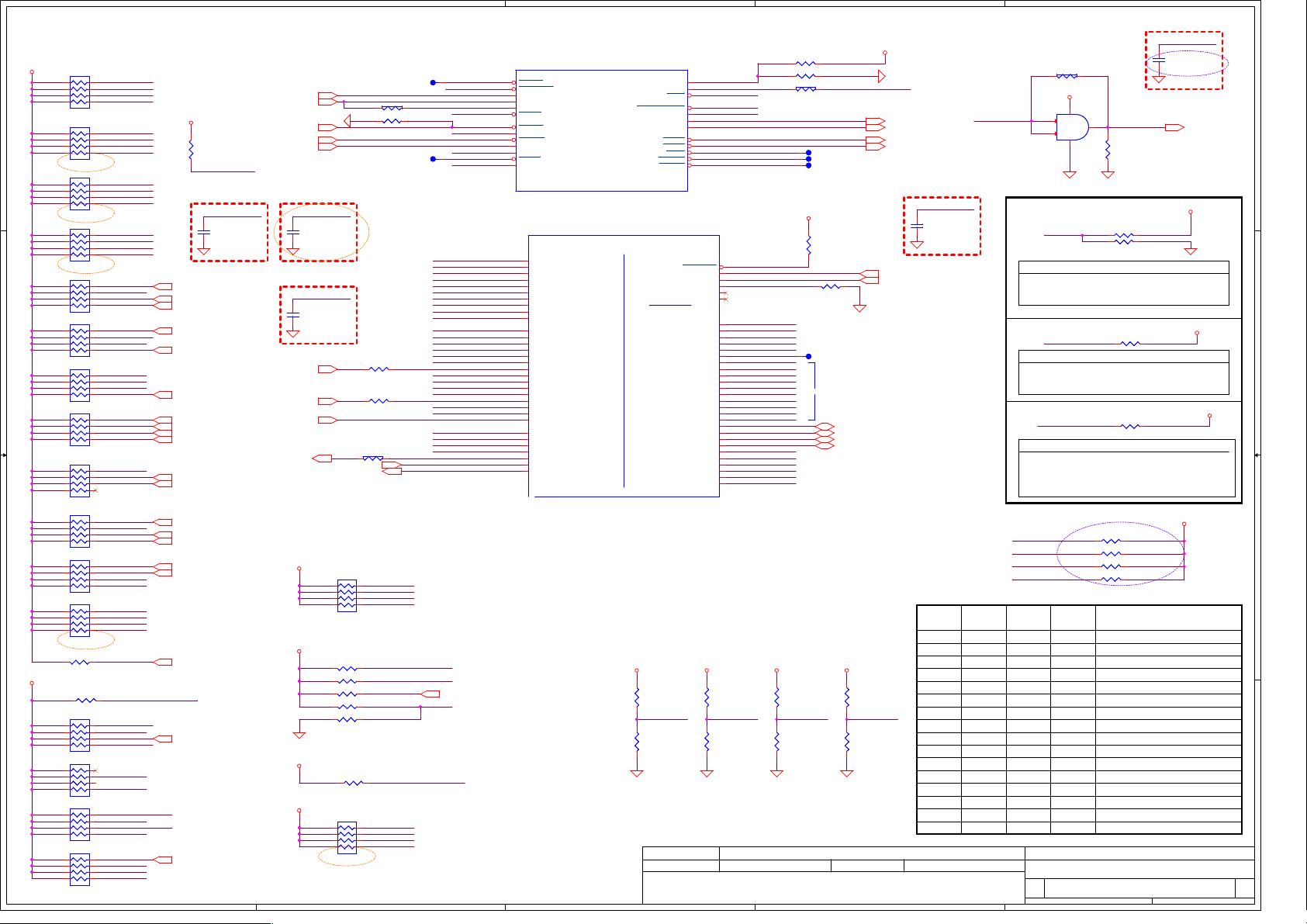

8-BDW MCP(5/9) PM,GPIO,I2C

Custom

836Friday, October 17, 2014

2014/

04/10 2017/04/10

Co

mpal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Se

curity Classification

Co

mpal Secret Data

TH

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Is

sued Date

De

ciphered Date

LA

-B921PR10

1.0

P0

8-BDW MCP(5/9) PM,GPIO,I2C

Custom

836Friday, October 17, 2014

2014/

04/10 2017/04/10

Co

mpal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Se

curity Classification

Co

mpal Secret Data

TH

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Is

sued Date

De

ciphered Date

LA

-B921PR10

1.0

P0

8-BDW MCP(5/9) PM,GPIO,I2C

Custom

836Friday, October 17, 2014

2014/

04/10 2017/04/10

Co

mpal Electronics, Inc.

RP

50 10K_8P4R_5%

RP

50 10K_8P4R_5%

1 8

2 7

3 6

4 5

T5

3

T5

3

RC5

5 0_0402_5%

RC5

5 0_0402_5%

1 2

RP

63 10K_8P4R_5%@

RP

63 10K_8P4R_5%@

1 8

2 7

3 6

4 5

RC5

1

200K_0402_5%

RC5

1

200K_0402_5%

12

RC133 2.2K_0402_5%RC133 2.2K_0402_5%

1 2

RC65 10K_0402_5%RC65 10K_0402_5%

1 2

T5

2

T5

2

RC111 1K_0402_1%RC111 1K_0402_1%

1 2

RC118

10K_0402_5%

X76@

RC118

10K_0402_5%

X76@

12

RP

62 10K_8P4R_5%@

RP

62 10K_8P4R_5%@

1 8

2 7

3 6

4 5

RC60

1K_0402_1%

RC60

1K_0402_1%

12

RC5

3 0_0402_5%

RC5

3 0_0402_5%

1 2

RC67 10K_0402_5%RC67 10K_0402_5%

1 2

RC116

10K_0402_5%

X76@

RC116

10K_0402_5%

X76@

12

RC1

10 1K_0402_1%@

RC1

10 1K_0402_1%@

1 2

RP57 10K_8P4R_5%RP57 10K_8P4R_5%

1 8

2 7

3 6

4 5

RC62 0_0402_5%@RC62 0_0402_5%@

1 2

RC5

6 330K_0402_5%@

RC5

6 330K_0402_5%@

1 2

RC6

1

49.9_0402_1%

RC6

1

49.9_0402_1%

1 2

RC1

12

4.7K_0402_5%

@

RC1

12

4.7K_0402_5%

@

1 2

RC5

9

100K_0402_5%

RC5

9

100K_0402_5%

12

RP52 10K_8P4R_5%@ RP52 10K_8P4R_5%@

1 8

2 7

3 6

4 5

RC5

4 0_0402_5%

RC5

4 0_0402_5%

1 2

RC123

10K_0402_5%

X76@

RC123

10K_0402_5%

X76@

12

CC97

100P_0402_50V8J

@ESD@

CC97

100P_0402_50V8J

@ESD@

12

RC120

10K_0402_5%

X76@

RC120

10K_0402_5%

X76@

12

RC1

31 2.2K_0402_5%

RC1

31 2.2K_0402_5%

1 2

RP54 10K_8P4R_5%RP54 10K_8P4R_5%

1 8

2 7

3 6

4 5

RC147 10K_0402_5%RC147 10K_0402_5%

1 2

RC1

13 1K_0402_1%@

RC1

13 1K_0402_1%@

12

CC9

6

1000P_0402_50V7K

ESD@

CC9

6

1000P_0402_50V7K

ESD@

1

2

RC64 10K_0402_5%RC64 10K_0402_5%

1 2

RC119

10K_0402_5%

X76@

RC119

10K_0402_5%

X76@

12

Sy

stem Power Management

8

OF 20

UCPU1H

BDW-Y-LPDDR3_BGA1234

@

Sy

stem Power Management

8

OF 20

UCPU1H

BDW-Y-LPDDR3_BGA1234

@

SU

SACK

D1

9

SYS_

RESET

E2

6

SYS_

PWROK

A22

PC

H_PWROK

F9

APW

ROK

J22

PL

TRST

M2

3

RS

MRST

F7

SU

SWARN_N_SUSPWRDNACK_GPIO30

D8

PW

RBTN

M2

1

AC

PRESENT_GPIO31

M17

BAT

LOW_N_GPIO72

H17

SL

P_S0

G2

2

SL

P_WLAN_N_GPIO29

J18

DS

WVRMEN

G14

DP

WROK

J7

WA

KE

F1

9

GP

IO32_CLKRUN

B3

5

SU

S_STAT_N_GPIO61

D25

SU

SCLK_GPIO62

B27

SL

P_S5_N_GPIO63

A18

SL

P_S4

H1

9

SL

P_S3

N2

2

SL

P_A

G1

8

SL

P_SUS

D2

7

SL

P_LAN

K1

9

CP

U/MISC

LPIO

GPIO

10

OF 20

UCPU1J

BDW-Y-LPDDR3_BGA1234

@

CP

U/MISC

LPIO

GPIO

10

OF 20

UCPU1J

BDW-Y-LPDDR3_BGA1234

@

BM

BUSY_N_USB3PHY_PC_GPIO76

J30

GP

IO8

C18

LA

N_PHY_PWR_CTRL_GPIO12

J14

GPIO15

K25

GP

IO16

N26

GP

IO17

H31

GP

IO24

C22

GP

IO27

K17

GP

IO28

M25

GP

IO26

B15

GP

IO56

F25

GP

IO57

F23

GP

IO58

F15

GP

IO59

D15

GP

IO44

L18

GP

IO47

B29

GP

IO48

K29

GP

IO49

B31

GP

IO50

F33

HS

IOPC_PCIEPHY_PC_GPIO71

D29

GP

IO13

E14

GP

IO14

M19

GP

IO25

F17

GP

IO45

P23

GP

IO46

L22

GP

IO9

D17

GP

IO10

B17

DE

VSLP0_GPIO33

E30

SD

IO_POWER_EN_GPIO70

R36

DE

VSLP1_GPIO38

K31

DE

VSLP2_GPIO39

J41

SPKR

_GPIO81

A34

TH

ERMTRIP

CG

40

RCI

N_N_GPIO82

C34

SERIRQ

E34

PC

H_OPI_RCOMP

AB4

RS

VD_AJ14

AJ14

RS

VD_AL18

AL18

GS

PI0_CS_N__GPIO83

D40

GS

PI0_CLK_GPIO84

G34

GS

PI0_MISO_GPIO85

L36

GS

PI0_MOSI_GPIO86

K33

GS

PI1_CS_N_GPIO87

L34

GS

PI1_CLK_GPIO88

M31

GS

PI1_MISO_GPIO89

F37

GS

PI_MOSI_GPIO90

H35

UA

RT0_RXD_GPIO91

M35

UA

RT0_TXD_GPIO92

F39

UA

RT0_RTS_N_GPIO93

N43

UA

RT0_CTS_N_GPIO94

N41

UA

RT1_RXD_GPIO0

P29

UA

RT1_TXD_GPIO1

H38

UA

RT1_RST_N_GPIO2

N39

UA

RT1_CTS_N_GPIO3

N30

I2

C0_SDA_GPIO4

N36

I2

C0_SCL_GPIO5

R42

I2

C1_SDA_GPIO6

J37

I2

C1_SCL_GPIO7

M33

SD

IO_CLK_GPIO64

N34

SD

IO_CMD_GPIO65

H40

SD

IO_D0_GPIO66

R40

SD

IO_D1_GPIO67

R38

SD

IO_D2_GPIO68

J39

SD

IO_D3_GPIO69

P31

RP51 10K_8P4R_5%RP51 10K_8P4R_5%

1 8

2 7

3 6

4 5

RC5

7 10K_0402_5%

RC5

7 10K_0402_5%

1 2

UC3

MC

74VHC1G08DFT2G_SC70-5

@

UC3

MC

74VHC1G08DFT2G_SC70-5

@

B

2

A

1

Y

4

P

5

G

3

RP59 10K_8P4R_5%RP59 10K_8P4R_5%

1 8

2 7

3 6

4 5

RP

65 10K_8P4R_5%

RP

65 10K_8P4R_5%

1 8

2 7

3 6

4 5

RC148 10K_0402_5%@RC148 10K_0402_5%@

1 2

RC130 2.2K_0402_5%RC130 2.2K_0402_5%

1 2

RP

49 10K_8P4R_5%@

RP

49 10K_8P4R_5%@

1 8

2 7

3 6

4 5

RP

46 10K_8P4R_5%

RP

46 10K_8P4R_5%

1 8

2 7

3 6

4 5

RC146 10K_0402_5%RC146 10K_0402_5%

1 2

RC121

10K_0402_5%

X76@

RC121

10K_0402_5%

X76@

12

RP61 10K_8P4R_5%@ RP61 10K_8P4R_5%@

1 8

2 7

3 6

4 5

RP45 10K_8P4R_5%RP45 10K_8P4R_5%

1 8

2 7

3 6

4 5

RP55 10K_8P4R_5%@ RP55 10K_8P4R_5%@

1 8

2 7

3 6

4 5

T5

8

T5

8

RC117

10K_0402_5%

X76@

RC117

10K_0402_5%

X76@

12

T5

9

T5

9

CC9

3

100P_0402_50V8J

ESD@

CC9

3

100P_0402_50V8J

ESD@

12

RP

47 10K_8P4R_5%

RP

47 10K_8P4R_5%

1 8

2 7

3 6

4 5

RC132 2.2K_0402_5%RC132 2.2K_0402_5%

1 2

CC9

4

100P_0402_50V8J

@ESD@

CC9

4

100P_0402_50V8J

@ESD@

12

RC6

3 0_0402_5%

RC6

3 0_0402_5%

1 2

CC9

5

100P_0402_50V8J

@ESD@

CC9

5

100P_0402_50V8J

@ESD@

12

RP

64 10K_8P4R_5%@

RP

64 10K_8P4R_5%@

1 8

2 7

3 6

4 5

RC136 1K_0402_5%RC136 1K_0402_5%

1 2

T54T54

RP

48 10K_8P4R_5%

RP

48 10K_8P4R_5%

1 8

2 7

3 6

4 5

RC137 1K_0402_5%@RC137 1K_0402_5%@

1 2

RP58 10K_8P4R_5%@ RP58 10K_8P4R_5%@

1 8

2 7

3 6

4 5

T5

5

T5

5

RC138 0_0402_5%@RC138 0_0402_5%@

1 2

RC122

10K_0402_5%

X76@

RC122

10K_0402_5%

X76@

12

RC5

2 330K_0402_5%

RC5

2 330K_0402_5%

1 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

信息提交成功

信息提交成功