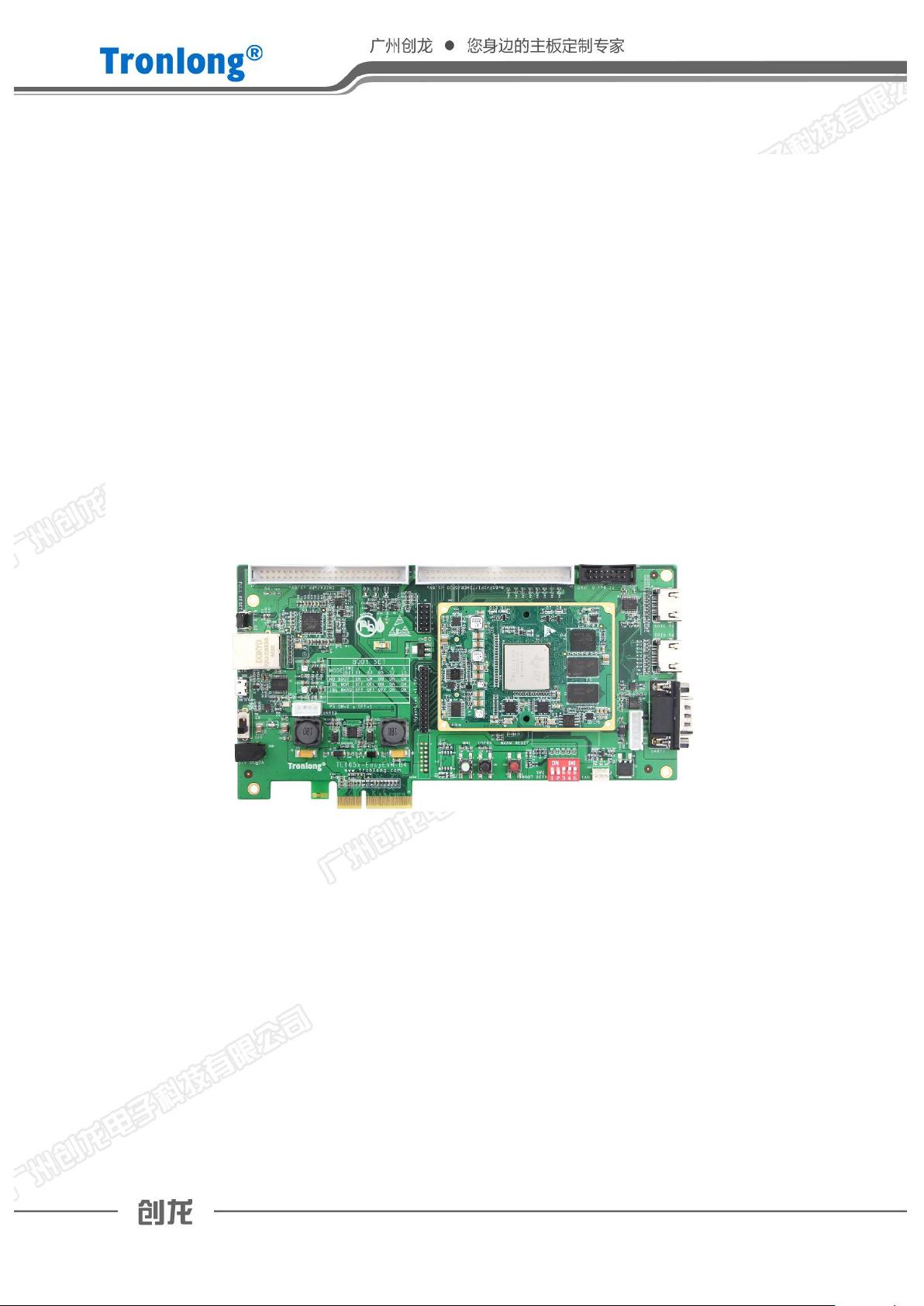

创龙TI C66x多核DSP开发板:高频运算与兼容详解

需积分: 17 138 浏览量

更新于2024-07-16

收藏 1.6MB PDF 举报

该文档主要介绍了创龙TI KeyStone C66x多核定点/浮点DSP开发板,基于TI的TMS320C665x系列,包括单核C6655和双核C6657型号。这款开发板的特点在于其高度兼容性,可以在相同的频率下提供四倍于C64x+器件的乘累加能力。核心配置强大,主频可选1.0GHz或1.25GHz,每核运算能力高达40GMACS(每秒40亿次MACS操作)和20GFLOPS(每秒20万亿次浮点运算),内置了两个Viterbi协处理器和一个Turbo协处理器解码器。每个核心配备有32KB的L1程序存储器(L1P)、32KB的L1数据存储器(L1D)、以及1MB的L2缓存,同时,多核之间共享更大的1MB内存,这使得它在处理密集型应用时表现出色。

开发板提供了丰富的软硬件参数,如SPINORFLASH等,使得用户可以根据项目需求进行定制。文档还包含了开发板的工作环境要求、电气特性、机械尺寸图,以及详细的订购型号和套件清单。对于技术支持,文档提供了公司官网www.tronlong.com作为主要的信息来源,包括销售邮箱sales@tronlong.com、公司总机020-8998-6280,以及技术论坛www.51ele.net、技术邮箱support@tronlong.com和技术热线020-3893-9734。此外,还有附录A提供的开发例程,供开发者参考和实践。

整个文档是为那些需要利用TMS320C665x DSP进行高性能计算和信号处理的工程师设计的,无论是硬件配置还是软件支持,都体现了创龙公司在该领域的专业性和对用户需求的重视。通过阅读这份文档,用户可以全面了解开发板的功能、性能、使用方法以及获取必要的技术支持,以便高效地进行项目开发。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2019-02-20 上传

2019-02-28 上传

2019-02-28 上传

2019-02-20 上传

2019-02-28 上传

2018-12-18 上传

Tronlong_

- 粉丝: 285

- 资源: 166

最新资源

- 行业文档-设计装置-一种切袋器.zip

- android应用源码高仿天天动听音乐-IT计算机-毕业设计.zip

- Assign3

- SMOK

- Luang:一个文件的简单Lua库即可翻译和格式化文本

- conf-deadlines

- tdd-checkout

- 基于python3.7+Qtpy5+opencv的交通监控图像处理.zip

- Sistemas-Distribuidos

- 网络IO模型 Linux环境下的network IO

- CSVFile

- IBM-Data-Analyst

- youshould:Web应用程序可帮助人们向朋友推荐事物

- node-asbs-dummy-ai:使用 node-asbs-lib 的虚拟船舶 AI

- vc在文件改变时得到通知,文件监控程序

- Famintos-Mobile:Projeto de Desenvolvimento Mobile