TMS29F008T, TMS29F008B

1048576 BY 8-BIT

FLASH MEMORIES

SMJS845A – MARCH 1997 – REVISED OCTOBER 1997

9

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

automatic-sleep mode

The ’29F008 has a built-in feature called automatic-sleep mode to minimize device energy consumption which

is independent of CE

, WE, and OE, and is enabled when addresses remain stable for 300 ns. Typical

sleep-mode current is 100 µA. Sleep mode does not affect output data, which remains latched and available

to the system.

algorithm selection

The algorithm-selection mode provides access to a binary code that matches the device with its proper

programming and erase command operations. This mode is activated when V

ID

(11.5 V to 12.5 V) is placed on

address pin A9. Address pins A1 and A6 must be logic low. Two bytes of code are accessed by toggling address

pin A0 from V

IL

to V

IH

. Address pins other than A0, A1, and A6 can be at logic low or at logic high.

The algorithm-selection mode can also be read by using the command register, which is useful when V

ID

is not

available to be placed on address pin A9. Table 4 shows the binary algorithm-selection codes.

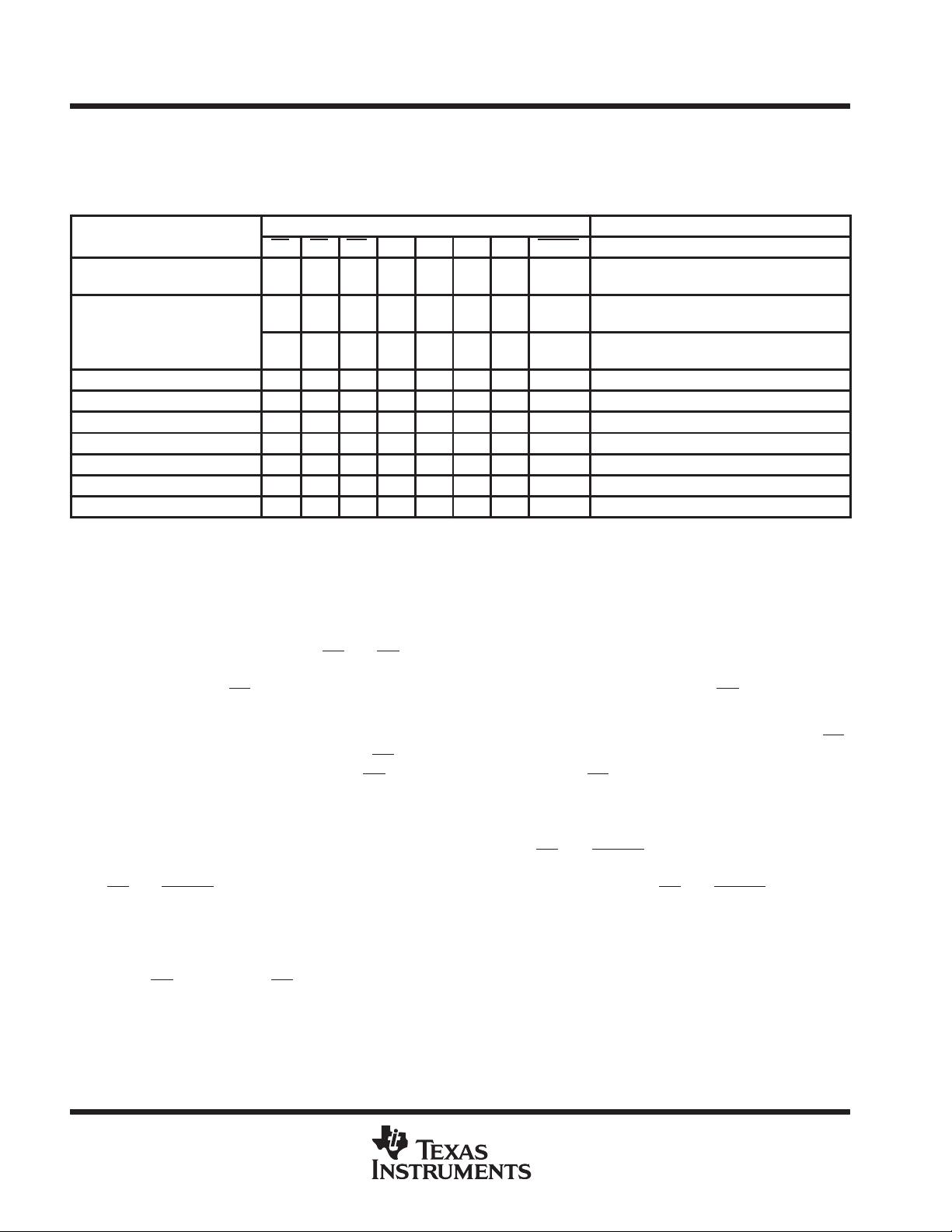

Table 4. Algorithm-Selection Codes (5-V Single Power Supply)

†

CODE DQ7 DQ6 DQ5 DQ4 DQ3 DQ2 DQ1 DQ0

Manufacturer-equivalent code 01H 0 0 0 0 0 0 0 1

TMS29F008T-Byte D6H 1 1 0 1 0 1 1 0

TMS29F008B-Byte 58H 0 1 0 1 1 0 0 0

Sector protection 01H 0 0 0 0 0 0 0 1

†

A1 = V

IL

, A6 = V

IL

, CE = OE = V

IL

erasure and programming

Erasure and programming of the ’29F008 are accomplished by writing a sequence of commands using standard

microprocessor write timing. The commands are written to a command register and input to the command-state

machine (CSM). The CSM interprets the command entered and initiates program, erase, suspend, and resume

operations as instructed. The

CSM acts as the interface between the write-state machine (WSM) and

external-chip operations. The WSM controls all voltage generation, pulse generation, preconditioning, and

verification of memory contents. Program and block-/chip-erase functions are fully automatic. Once the end of

a program or erase operation has been reached, the device resets internally to the read mode. If V

CC

drops

below the low-voltage-detect level (V

LKO

), any programming or erase operation is aborted and subsequent

writes are ignored until the V

CC

level is greater than V

LKO

. The control pins must be logically correct to prevent

unintentional command writes or programming or erasing.

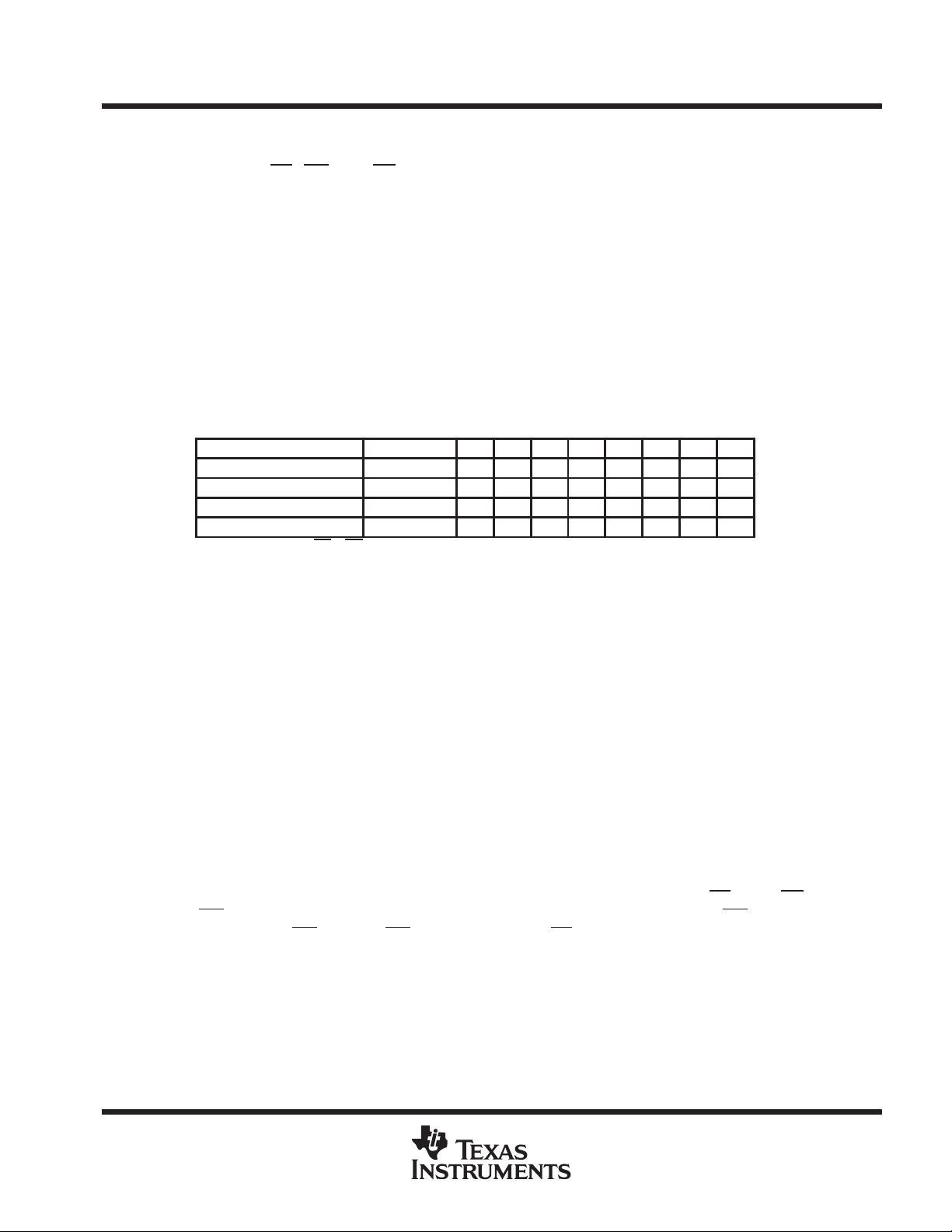

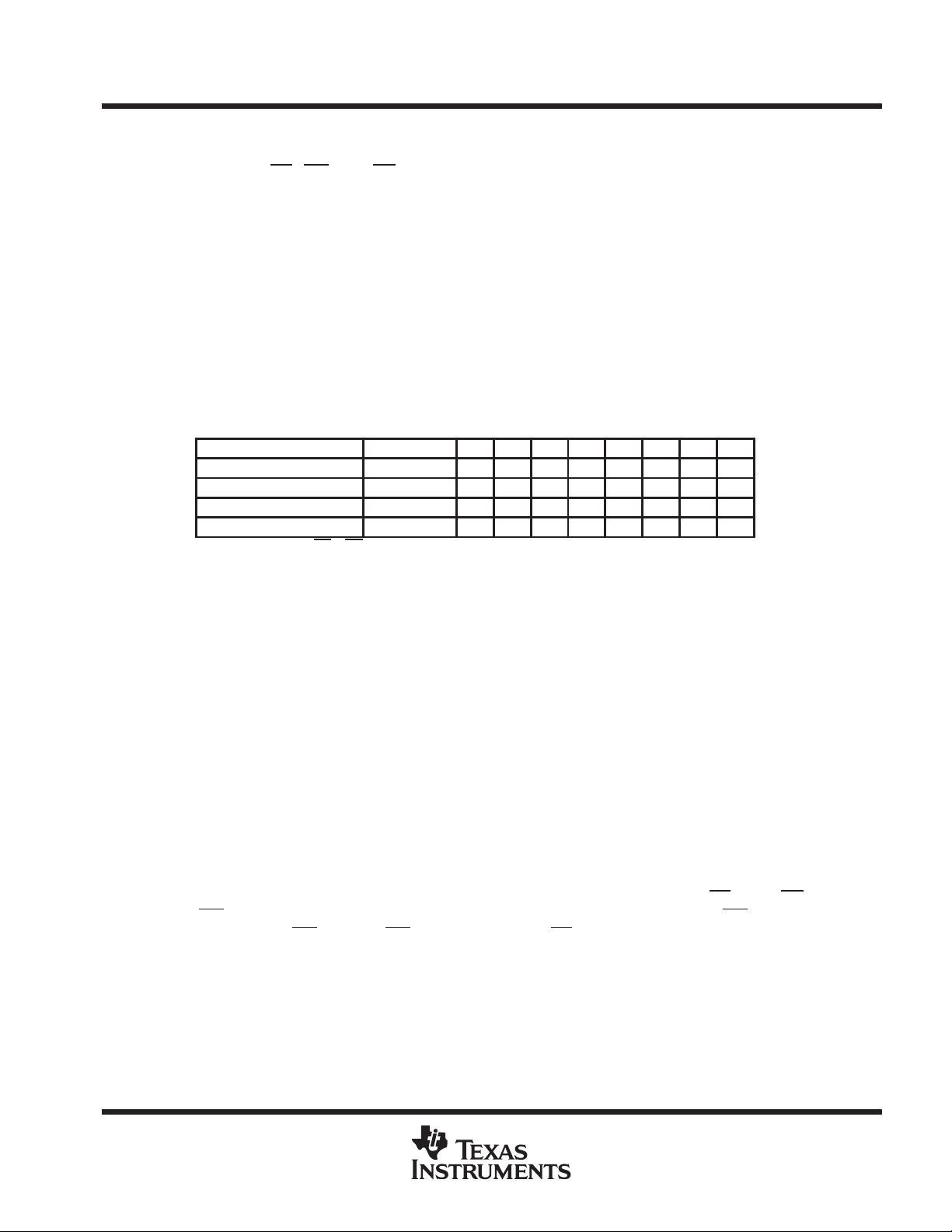

command definitions

Device operating modes are selected by writing specific address and data sequences into the command

register. Table 5 defines the valid command sequences. Writing incorrect address and data values or writing

them in the incorrect sequence causes the device to reset to the read mode. The command register does not

occupy an addressable memory location. The register is used to store the command sequence, along with the

address and data needed by the memory array. Commands are written by setting CE

= V

IL

, OE = V

IH

, and

bringing WE

from logic high to logic low. Addresses are latched on the falling edge of WE and data is latched

on the rising edge of WE

. Holding WE = V

IL

and toggling CE is an alternative method. See the switching

characteristics of the write/erase/program-operations section for specific timing information.

PRODUCT PREVIEW