Verilog EDA实验教程:从基础到综合设计

需积分: 9 142 浏览量

更新于2024-07-25

收藏 2.16MB DOC 举报

"这是一份关于VERILOG实验的指导文档,主要涵盖了基础的EDA技术实践,包括使用ISE开发环境,学习VERILOG语言,设计各种数字逻辑电路,如计数器、乘法器、加法器、比较器,以及应用在实际场景中的流水灯、交通灯和跑表设计等。实验旨在让学生深入理解课堂理论,提升实践能力,并掌握FPGA器件的开发和VERILOG编程。"

实验指导书的核心内容围绕着几个关键知识点展开:

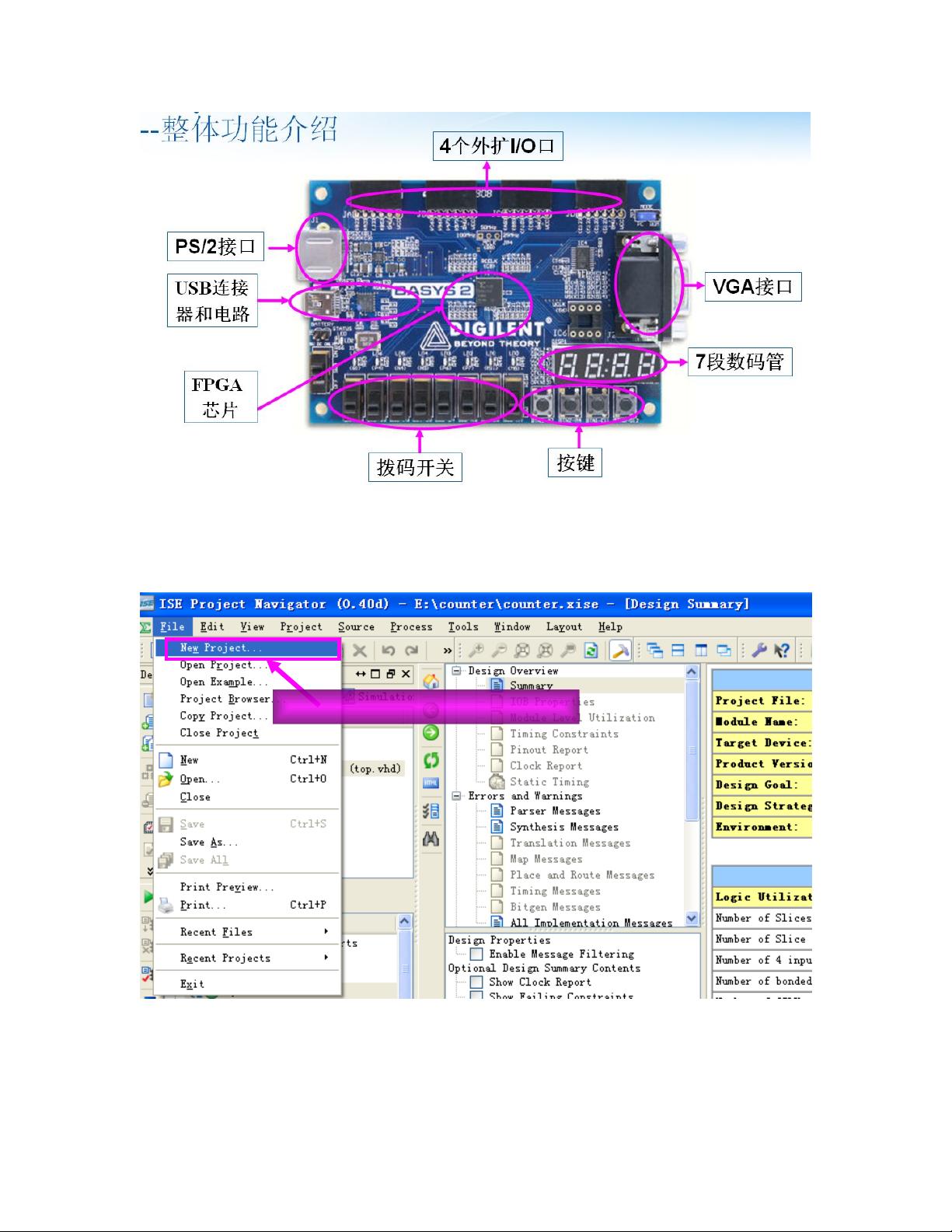

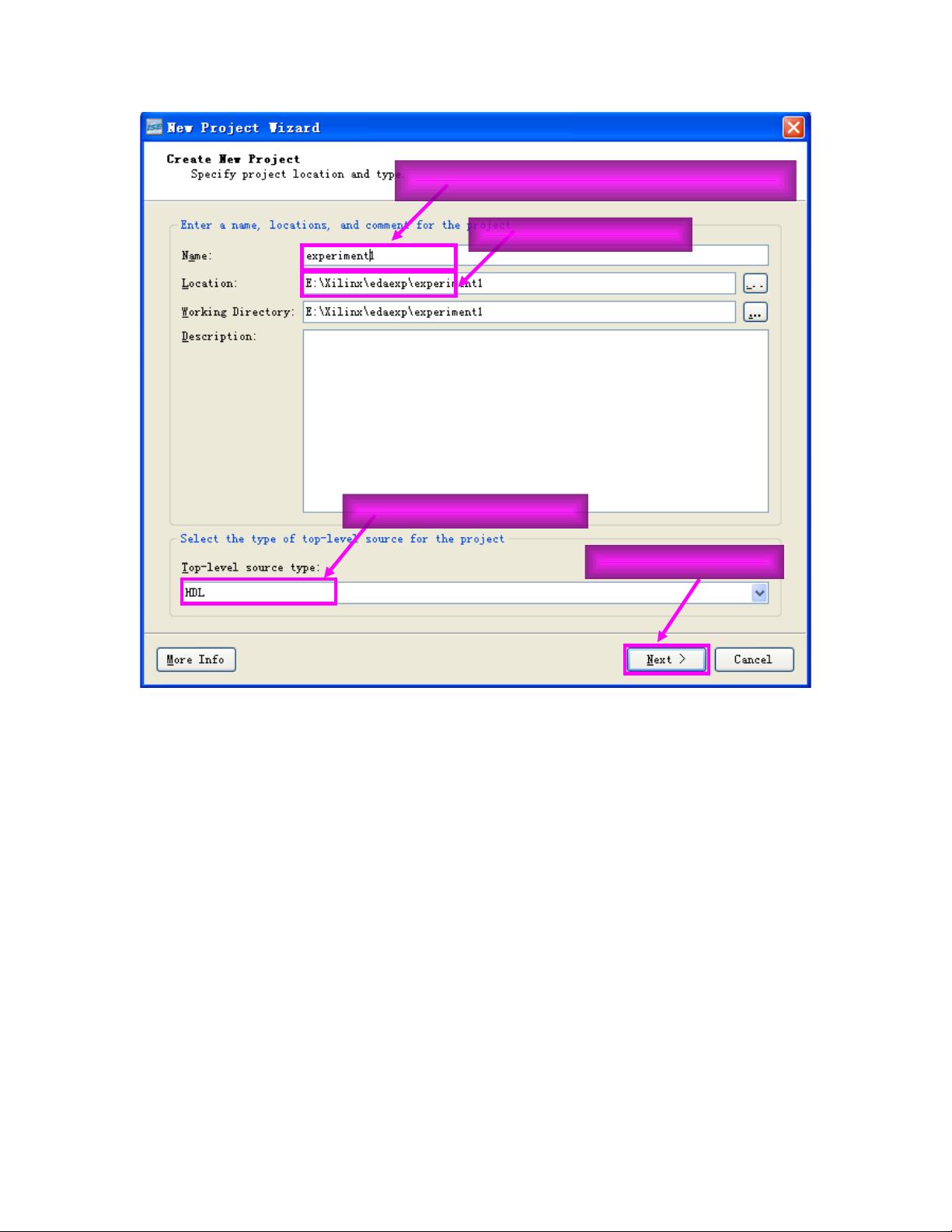

1. **EDA技术与ISE开发环境**:EDA(电子设计自动化)是现代电子系统设计的重要工具,而ISE(Integrated Software Environment)是Xilinx公司提供的一种用于FPGA和CPLD设计的集成开发环境。学生需要通过实验学习如何在ISE中进行项目创建、代码编写、逻辑综合、仿真验证等步骤。

2. **VERILOG语言**:VERILOG是一种硬件描述语言,用于描述数字系统的结构和行为。在实验中,学生需要理解和掌握VERILOG的基本语法,如模块定义、赋值语句、运算符、条件语句、循环结构等,以便设计和实现数字逻辑电路。

3. **组合逻辑电路设计**:这部分涉及加法器、乘法器和比较器的实现。加法器可以实现二进制数字的基本算术运算,乘法器扩展了这一功能,比较器则用于比较两个数字的大小。这些基本单元是数字系统的基础组件。

4. **时序逻辑电路设计**:计数器是时序逻辑电路的典型例子,它能根据时钟信号改变自身的状态。学生需要学习不同类型的计数器(如模N计数器、二进制计数器、同步计数器等)的VERILOG实现。

5. **应用电路设计**:流水灯和交通灯是实际应用的例子,它们涉及到多路开关控制和定时逻辑。流水灯通常用于展示LED的连续点亮效果,而交通灯则是模拟真实交通信号控制的简化模型,涉及状态机的设计。

6. **综合层次性实验**:数字秒表设计结合了前面学到的多种概念,要求学生设计一个可以实时计时的数字系统,这需要对时序控制、计数器、显示驱动等有深入的理解。

实验要求强调了预习、实验过程的规范性和实验报告的重要性,旨在培养学生的独立思考和问题解决能力。实验报告不仅是实验结果的记录,也是理论与实践结合的体现,通过对实验结果的分析,学生能够深化对EDA技术原理的认识。

实验守则则强调了实验室的秩序和设备安全,提醒学生应尊重并保护公共资源,遵守安全规定,确保实验环境的整洁和设备的完好。

点击了解资源详情

点击了解资源详情

134 浏览量

2021-12-15 上传

182 浏览量

171 浏览量

2011-03-17 上传

227 浏览量

160 浏览量

shanekravgogo

- 粉丝: 0

- 资源: 2

最新资源

- Android MVP 快速开发框架Android-ZBLibrary-master

- subject1_raw_mri.zip

- 程序员必须知晓的11个C++要点-供大家学习研究参考

- 4.4 RT-Thread 完成对AT2402 一个字节的读写

- 欧盟GDPR新版数据跨境转移标准合同条款(SCCs)

- 基于STM32F407的TCS230颜色识别的程序

- 基因测序-利用psa方法对基因测序进行开发

- WPF房屋租售管理系统

- 基因二代测序-分别对blast和bwa比对结果进行统计比较-20230506

- 使用HTML和JavaScript编写的猜数字游戏

- 基因测序-统计扩增子引物对应数据库的不同碱基的情况-20230529

- Unity地图随机生成插件 TileWorldCreator 3 v3.1.2p1

- YOLOv8 缺陷检测之AnyLabeling标注格式转换成YOLO格式, YOLO数据集划分为训练集,验证集和测试集

- 新路由3 newifi3 d2刷老毛子Padavan固件

- 答案.rar

- Web-Design-Challenge