QuartusII实现奇偶校验电路设计与仿真教程

“计算机组成原理实验-奇偶校验”

这个实验主要讲解了如何在Quartus II软件中实现奇偶校验功能,这是一种简单的错误检测方法,广泛应用于数据传输和存储中。奇偶校验通过添加一个额外的位来确保数据中的“1”数量是奇数或偶数,从而可以检测出单比特错误。

实验步骤如下:

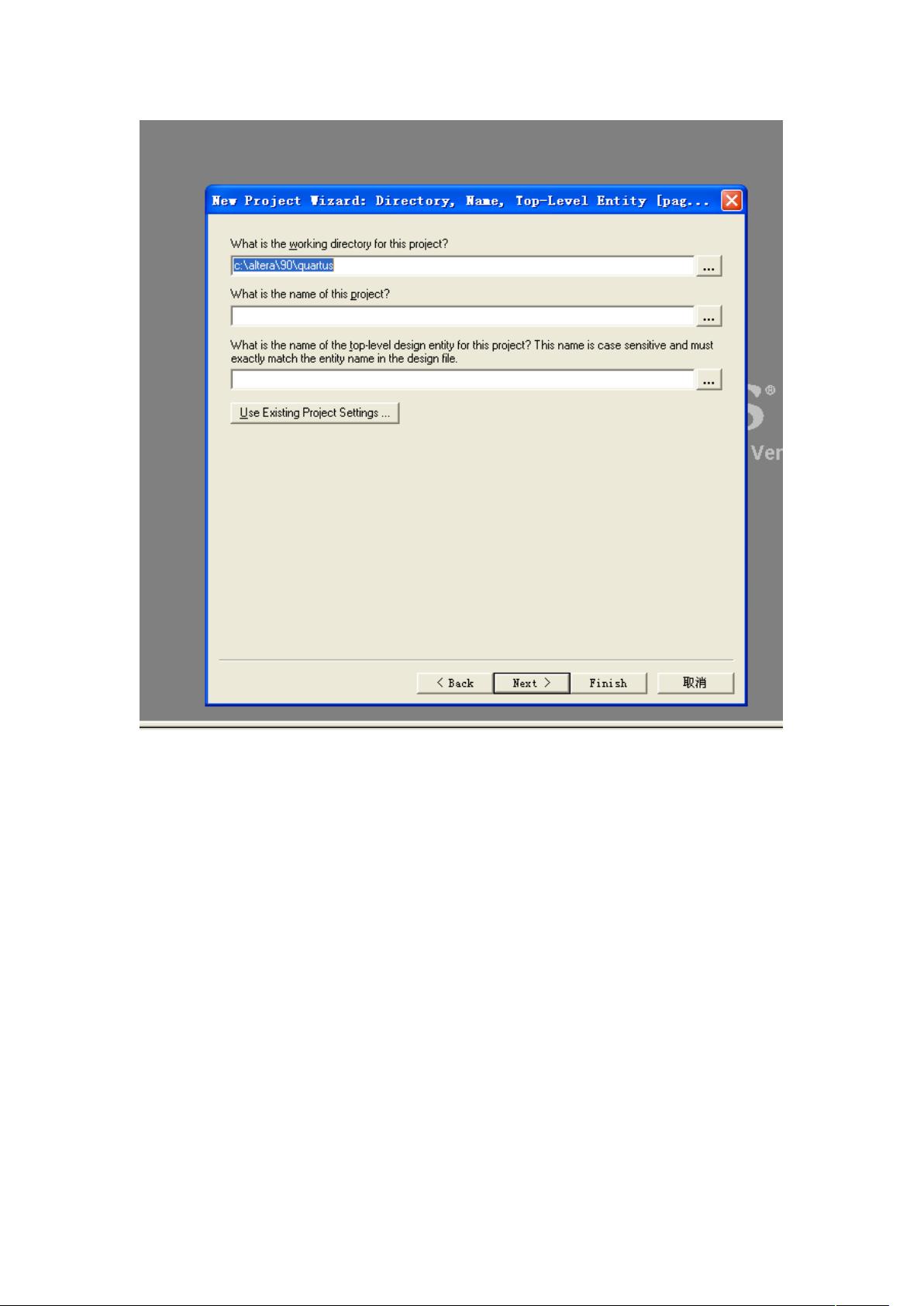

1. 首先启动Quartus II软件,创建新的工程。在“File”菜单中选择“New Project Wizard”,按照向导设置工程的路径、项目名和实体名称。

2. 创建工程后,新建Block Diagram/Schematic文件,用于设计电路逻辑。

3. 在设计中引入所需的元器件。本实验中需要用到74386(四异或门)和7404(六非门)来构建奇偶校验电路,同时还需要输入输出引脚,这些可以通过“Libraries”目录下的“MaxPlus2”和“Primitives”进行选择。

4. 使用虚拟电线连接元器件,形成完整的奇偶校验电路。虚拟电线可以通过工具栏上的相应图标添加。

5. 保存设计文件,确保所有工作都已保存。

接下来,进行模拟仿真以验证电路功能:

6. 新建Vector Waveform File,用于设定输入值并观察输出。

7. 使用Node Finder查找电路中的所有引脚,并在List中设置输入引脚的初始值,可以是0或1,以模拟不同的数据组合。

8. 编译.bdf文件,然后在Processing菜单中选择Simulator Tool,启动函数模拟器生成网络列表并开始仿真。

9. 仿真完成后,查看报告以确认仿真波形是否符合预期。通过波形图,可以判断奇偶校验功能是否正确实现,即在不同输入数据下,输出的校验位能正确反映出数据中“1”的奇偶性。

这个实验详细地介绍了如何在硬件描述语言环境下设计和验证奇偶校验电路,帮助学生理解数字逻辑设计的基本过程,同时也强调了错误检测在计算机系统中的重要性。通过实际操作,学生可以更好地掌握计算机组成原理中的基本概念和实践技能。

2020-05-08 上传

2020-11-29 上传

2024-05-20 上传

2010-05-08 上传

2010-05-19 上传

2009-12-14 上传

2021-12-06 上传

2022-06-11 上传

Sun_cg

- 粉丝: 0

- 资源: 3

最新资源

- 探索数据转换实验平台在设备装置中的应用

- 使用git-log-to-tikz.py将Git日志转换为TIKZ图形

- 小栗子源码2.9.3版本发布

- 使用Tinder-Hack-Client实现Tinder API交互

- Android Studio新模板:个性化Material Design导航抽屉

- React API分页模块:数据获取与页面管理

- C语言实现顺序表的动态分配方法

- 光催化分解水产氢固溶体催化剂制备技术揭秘

- VS2013环境下tinyxml库的32位与64位编译指南

- 网易云歌词情感分析系统实现与架构

- React应用展示GitHub用户详细信息及项目分析

- LayUI2.1.6帮助文档API功能详解

- 全栈开发实现的chatgpt应用可打包小程序/H5/App

- C++实现顺序表的动态内存分配技术

- Java制作水果格斗游戏:策略与随机性的结合

- 基于若依框架的后台管理系统开发实例解析