Vivado软件使用教程:基础操作与综合约束设置

需积分: 27 70 浏览量

更新于2024-06-28

收藏 912KB PDF 举报

"这篇内容介绍了如何进行vivado软件的基础操作,包括分析与综合、约束输入,特别是关于XDC文件的生成和时钟、IO约束的设置。"

在使用vivado这款强大的FPGA设计工具时,理解并掌握其基础操作至关重要。vivado提供了从设计输入到硬件实现的完整流程,其中包括了设计的分析、综合和约束处理等步骤。

首先,设计的分析阶段是通过"OpenElaboratedDesign"按钮进行的,它会检查设计的语法,并在Message窗口中显示ERROR和Warning的数量。这个过程还会生成网络表和原理图,这些文档对理解和调试设计非常有帮助。设计分析完成后,用户可以在OpenElaboratedDesign的子菜单中找到Schematic和Netlist等选项,以便查看设计的可视化表示和逻辑连接。

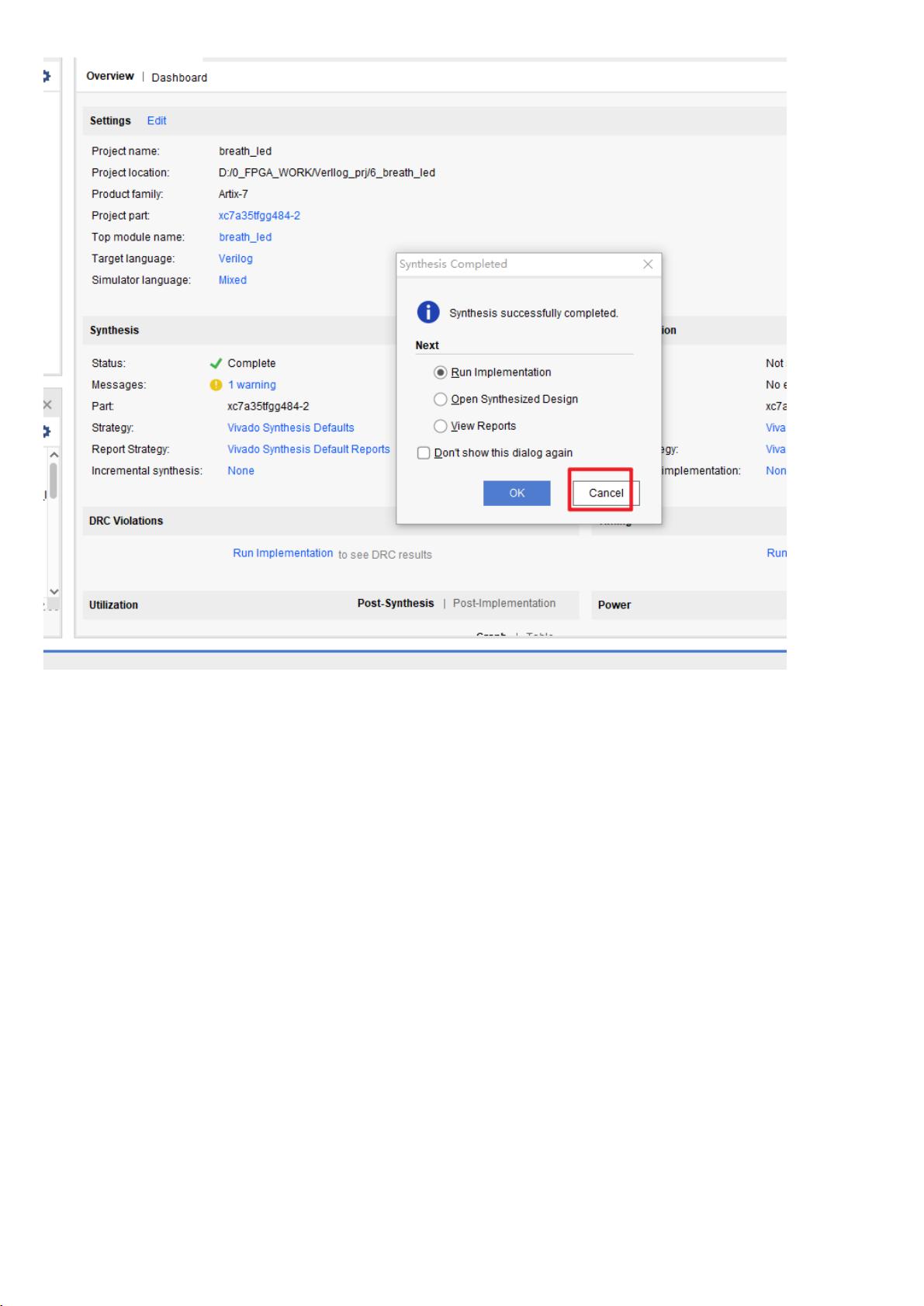

接下来是设计的综合阶段,用户点击"Run Synthesis"按钮启动这个过程。综合过程中,vivado将高级语言描述(如Verilog或VHDL)转换为门级逻辑,同时优化设计以满足性能目标。综合完成后,状态会显示为"Complete"。

约束输入是vivado设计流程中的关键步骤,它确保设计符合实际硬件的限制。有两种主要方法生成XDC(约束文件):一种是通过IO面板直接设置,另一种是手动创建。XDC文件用于绑定.V文件中的虚拟引脚与实际硬件引脚,同时设置电压、速度等级等参数。

时钟约束是约束输入的重要部分,使用`create_clock`命令定义时钟的名称和周期。例如,`create_clock -name clk -period 20 [get_ports sys_clk]` 创建了一个名为clk、周期为20ns的时钟。此外,IO约束确保了引脚的电气特性,如`set_property`命令用于指定引脚位置(如PACKAGE_PINR4)和IO标准(如LVCMOS33),同时绑定到设计中的相应端口。

最后,`set_property BITSTREAM.GENERAL.COMPRESS true [current_project]` 这一行代码是关于位流压缩的设置,启用压缩可以减少下载到FPGA的位流文件大小,提高下载速度。

vivado软件基础操作涉及到了设计的解析、综合以及约束设置等多个环节,每一个环节都对最终设计的功能性和性能有着直接影响。熟练掌握这些基本操作对于进行高效且精确的FPGA设计至关重要。

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2024-09-19 上传

2019-03-28 上传

2018-06-17 上传

171 浏览量

点击了解资源详情

乐高精神

- 粉丝: 0

- 资源: 14

最新资源

- OPNET 用户指南_翻译稿

- 数据库的设计-----VFP

- FLEX 3 CookBook 简体中文学习基础资料PDF

- TOMCAT移植到JBOSS

- Myeclipse7[1].0+JBoss5.0测试EJB3.0环境搭建过程详解

- PROTEUS中文教程

- NCURSES Programming HOWTO中文第二版

- 高性能计算之并行编程技术--MPI并行程序设计

- ORACLE备份策略

- 软件评测师07年大题与答案,Word版

- The Productive Programmer.pdf

- c#团队开发之命名规范

- 计算机操作系统(汤子瀛)习题答案.pdf

- ArcGIS Server轻松入门

- 基于组播技术的网络抢答系统设计

- USB数据采集的几个问题