Xilinx ISE10.1快速入门教程

"xilinx ISE10.1使用教程简介"

Xilinx ISE(Integrated Software Environment)是Xilinx公司提供的一款用于设计、仿真、综合、实现和配置 FPGA(Field-Programmable Gate Array)和 CPLD(Complex Programmable Logic Device)的集成开发环境。ISE 10.1 版本是一个较早的版本,但其基本工作流程对于初学者理解 FPGA 设计仍然是有价值的。

1. **创建新项目 (New Project)**

在开始设计之前,首先需要创建一个新的项目。通过双击桌面上的 Xilinx ISE 10.1 快捷方式打开 Project Navigator。选择 "File" -> "New Project",填写项目名称和位置,确保路径和名称不含中文以避免可能出现的错误。在器件特性对话框中,选择合适的 FPGA 家族、设备型号、封装和速度等级,这些选择应根据实际使用的开发板进行设定。

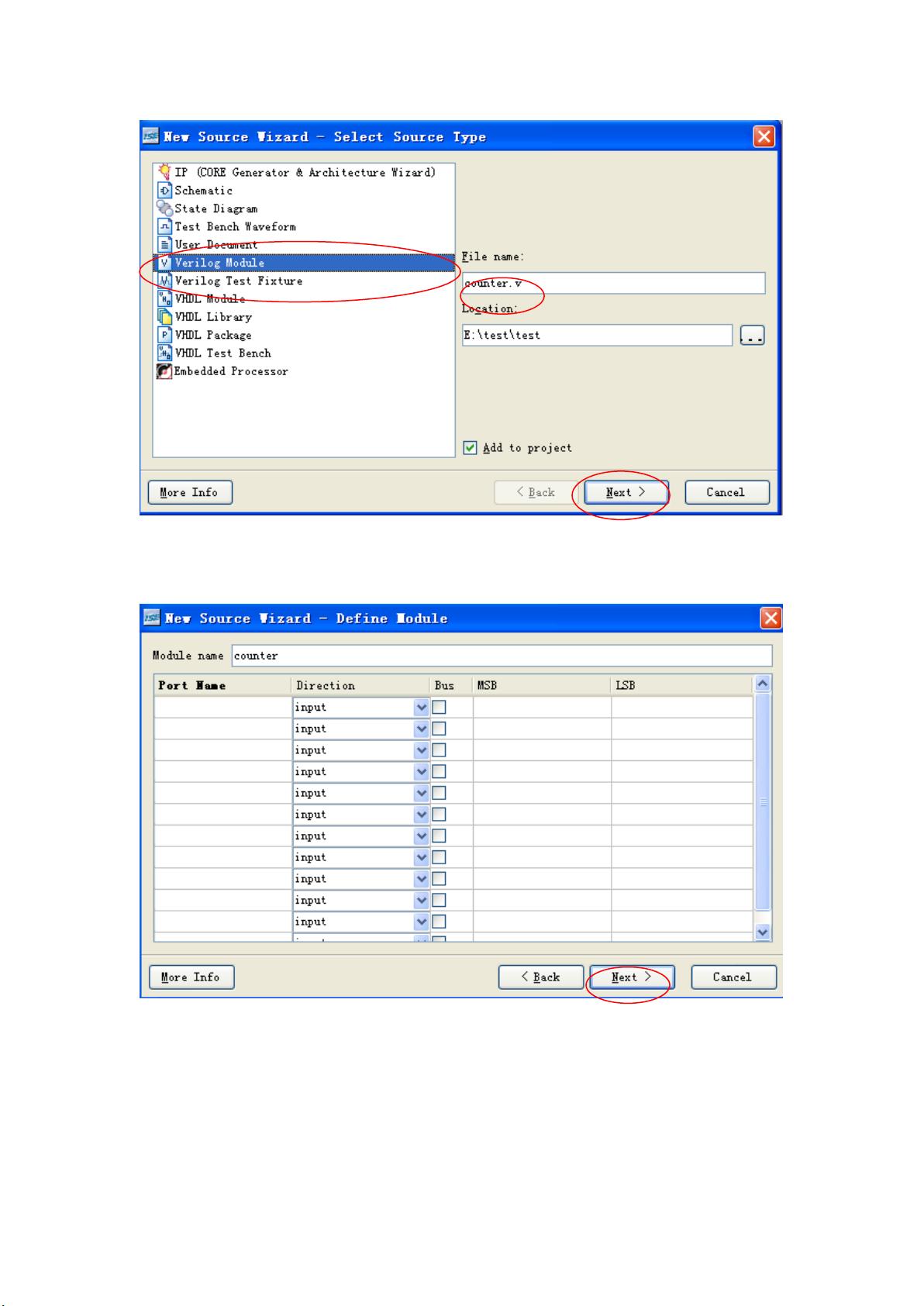

2. **添加源文件 (New Source)**

在工程的 "Source" 文件夹下,右键选择 "New Source",然后选择 "Verilog Module"。输入模块名称,如 "counter",并点击 "Next" 和 "Finish"。接着,可以打开 .v 文件编写 Verilog 代码。

3. **行为级仿真 (Behavioral Simulation)**

要对设计进行验证,可以创建一个 Test Bench。右键点击 "Source" 窗口,选择 "New Source",然后选择 "TestBench WaveForm"。输入测试平台的文件名,如 "counter_tb",关联相应的源文件,设置时钟参数和其他必要的信号,编写测试平台的代码,以模拟真实情况下的输入和期望输出。

4. **ChipScope 分析器 (ChipScope)**

ChipScope 是一款用于 FPGA 在系统调试的工具,可以在设计实施后捕获和分析内部信号。在设计中添加 ChipScope 组件,设置观察和控制信号,便于后期调试。

5. **设计综合 (Synthesize Your Design)**

综合阶段将 Verilog 代码转换为门级网表,这一过程考虑了设计的约束条件,如时序、面积和功耗等。在 ISE 中,选择 "Flow" -> "Start" -> "Synthesis" 来执行这个步骤。

6. **设计实现 (Implement Your Design)**

实现阶段将综合后的网表映射到 FPGA 的具体逻辑单元上,优化布线,生成编程文件。选择 "Flow" -> "Start" -> "Implementation" 开始此过程。

7. **生成编程文件 (Generate Programming File)**

实现完成后,需要生成适用于 FPGA 编程的文件,通常为 bitstream 文件。选择 "File" -> "Create Bitstream" 生成该文件。

8. **使用 ChipScope 分析设计 (Analyze Design Using ChipScope)**

在硬件上运行设计后,通过 ChipScope 探针收集数据,分析设计的内部行为,确认设计是否按照预期工作。

在学习 Xilinx ISE 10.1 的过程中,理解 FPGA 设计的基本流程和每个步骤的作用至关重要。虽然这个版本可能已不再得到官方支持,但它仍然能够帮助初学者掌握 FPGA 设计的基础,为进一步学习更新的工具如 Vivado 或 Vitis 奠定基础。

点击了解资源详情

点击了解资源详情

点击了解资源详情

1195 浏览量

438 浏览量

点击了解资源详情

点击了解资源详情

856 浏览量