西南大学:2020级计算机专业半加器、全加器逻辑功能实验报告

在本实验报告中,针对西南大学计算机与信息科学学院2020级计算机科学与技术(中外合作办学)2班的2022年9月19日实验,学生李春昱进行了半加器和全加器逻辑功能的验证型测试。实验的主要目标包括:

1. 掌握组合逻辑电路的功能测试方法:通过实际操作和理论学习,学生需理解并能够应用到组合逻辑电路的设计和测试中,确保电路在任何时刻的输出仅依赖于当前输入,不受先前状态影响。

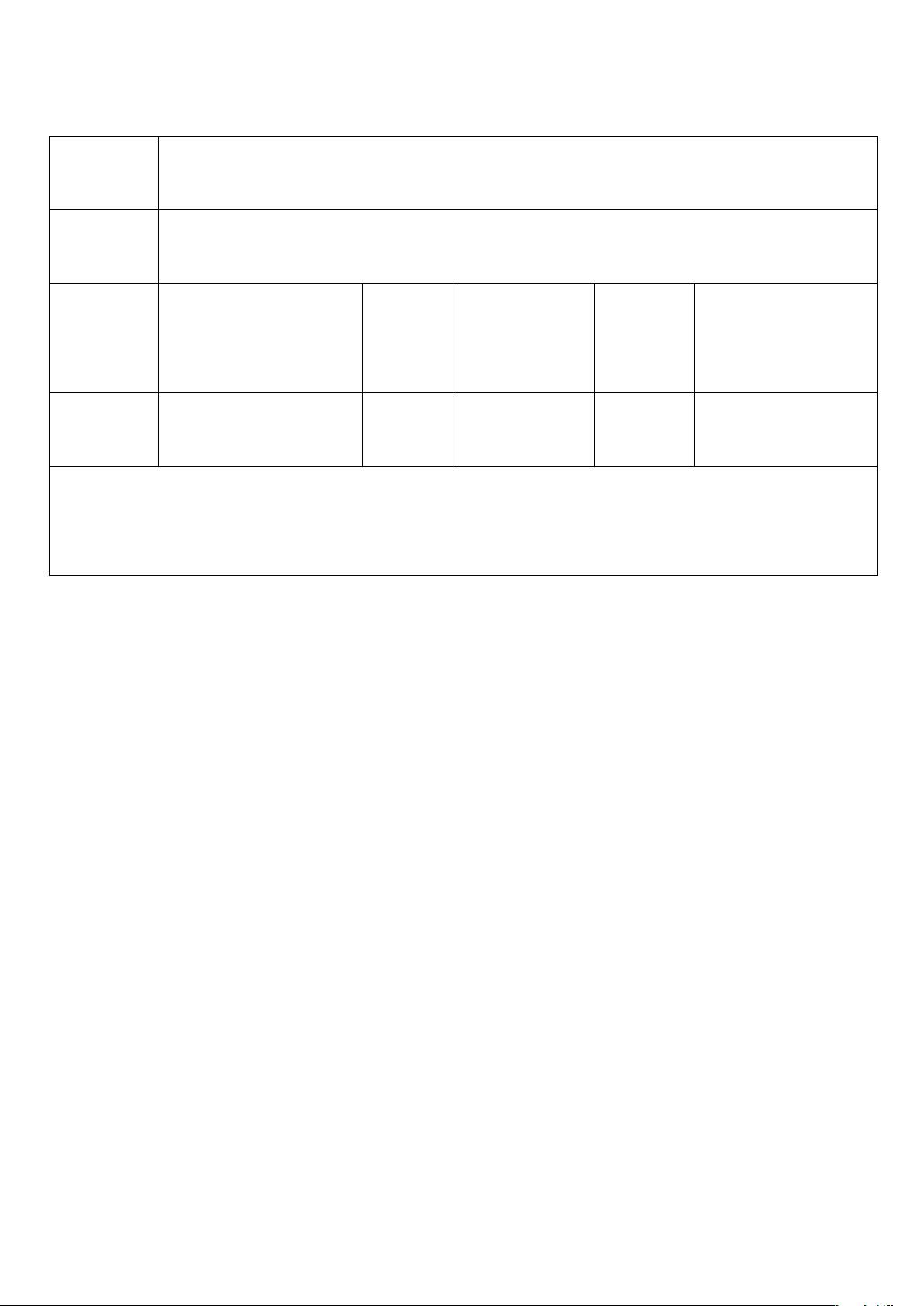

2. 理解和应用半加器和全加器的逻辑功能:半加器用于实现两个一位二进制数的简单相加,其逻辑表达式基于异或(XOR)门和与(AND)门的组合。半加器的输出包括半加和(Si)和进位(Ci),分别表示加数的直接结果和向高位的进位。全加器在此基础上增加了一个额外的功能,即处理低位进位,能够同时处理两个输入和来自低位的进位,其逻辑设计更为复杂,但同样基于基本门电路的组合。

实验内容包括分析组合逻辑电路的原理,从输出开始逆向推导逻辑表达式,然后通过Multisim这样的模拟工具进行电路设计和功能验证。学生需要通过绘制真值表、构建逻辑函数以及实际电路的搭建和测试,来验证半加器和全加器的正确性,确保它们按照预期的逻辑规则工作。

通过这个实验,学生不仅能加深对数字电路基本概念的理解,还能提高逻辑分析、电路设计和实验操作技能,为后续深入学习数字电子技术打下坚实的基础。

相关推荐

自驱OK

- 粉丝: 593

- 资源: 24

最新资源

- pogpoints

- A-Star-Visualizer

- MusicalStructure:显示数组,数组列表,意图和Java代码

- tmux-thumbs-用Rust编写的tmux-finger的快速版本,复制/粘贴vimium / vimperator等tmux。-Rust开发

- 行业文档-设计装置-一种平张纸托盘包装盖板.zip

- 视场演员组件。虚幻引擎4:添加呈现视场的组件

- XSL合并工具,店铺商品订单合并工具

- kiftd私人云盘搭建系统 v1.0.18

- buildTest

- ESP32-W5100:PoC应用程序测试W5100与esp-idf的集成

- 定时关机.rar

- Rcon Web Console-开源

- LSP客户端在Rust中实现并开箱即用地支持rls。-Rust开发

- 行业文档-设计装置-一种具有储物功能的床体包裹面料.zip

- DroidAttack:TPS(第三人称射击游戏)演示游戏,该游戏使用C ++编码的虚幻引擎4构建。 - 开发中

- STM32官方文档HAL&LL库相关