MIPS五段流水线CPU设计实验详解与应用

需积分: 0 28 浏览量

更新于2024-07-01

1

收藏 2.22MB PDF 举报

本章节主要介绍了MIPS五段流水机制设计实验,以第六章“理想流水线CPU设计”为核心。实验的主要目的是让学生深入理解MIPS指令流水线的基本原理,通过实践改造单周期CPU为理想流水CPU,消除冒险冲突,提升CPU性能。在理想流水线设计中,学生将学习到以下几个关键知识点:

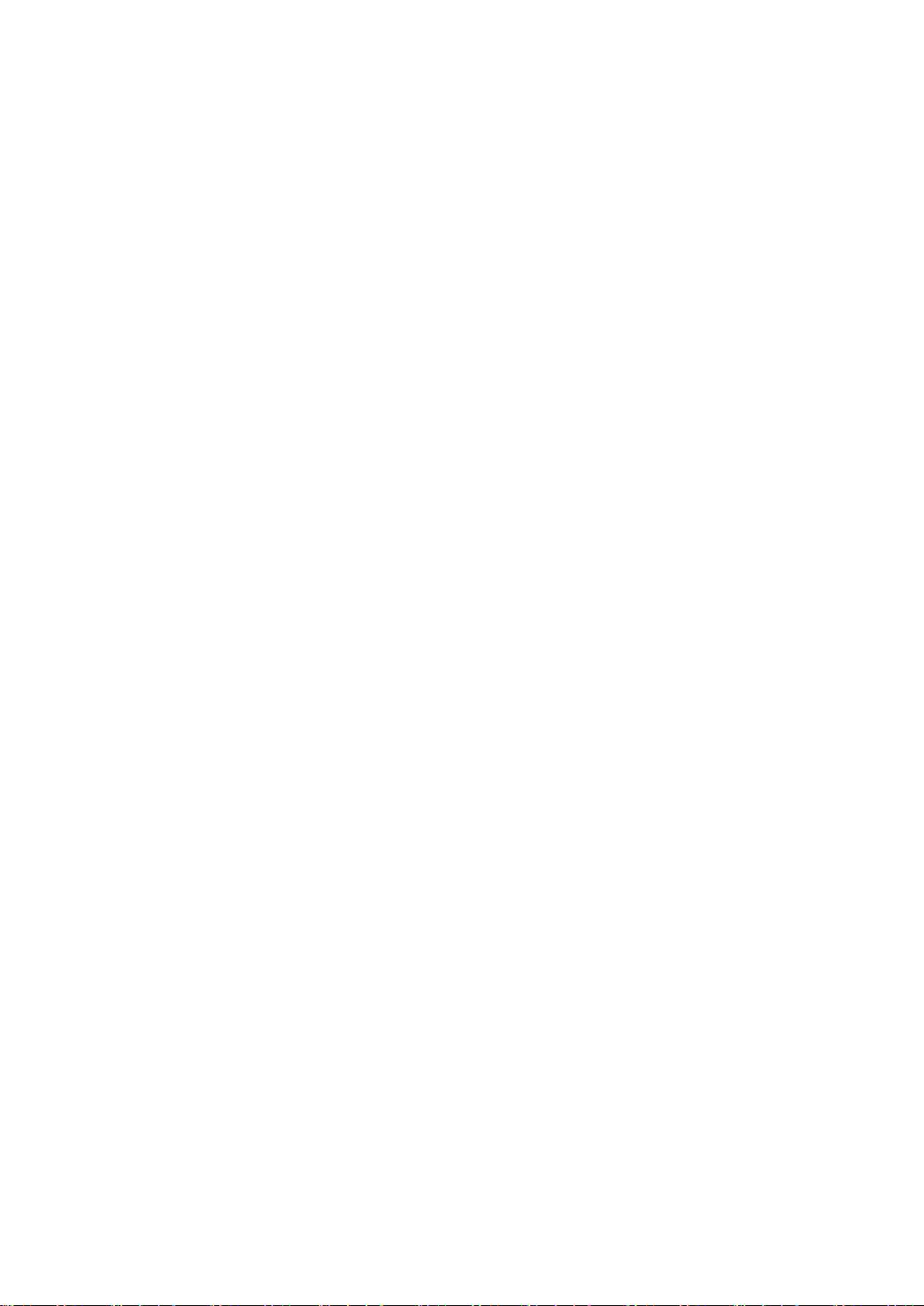

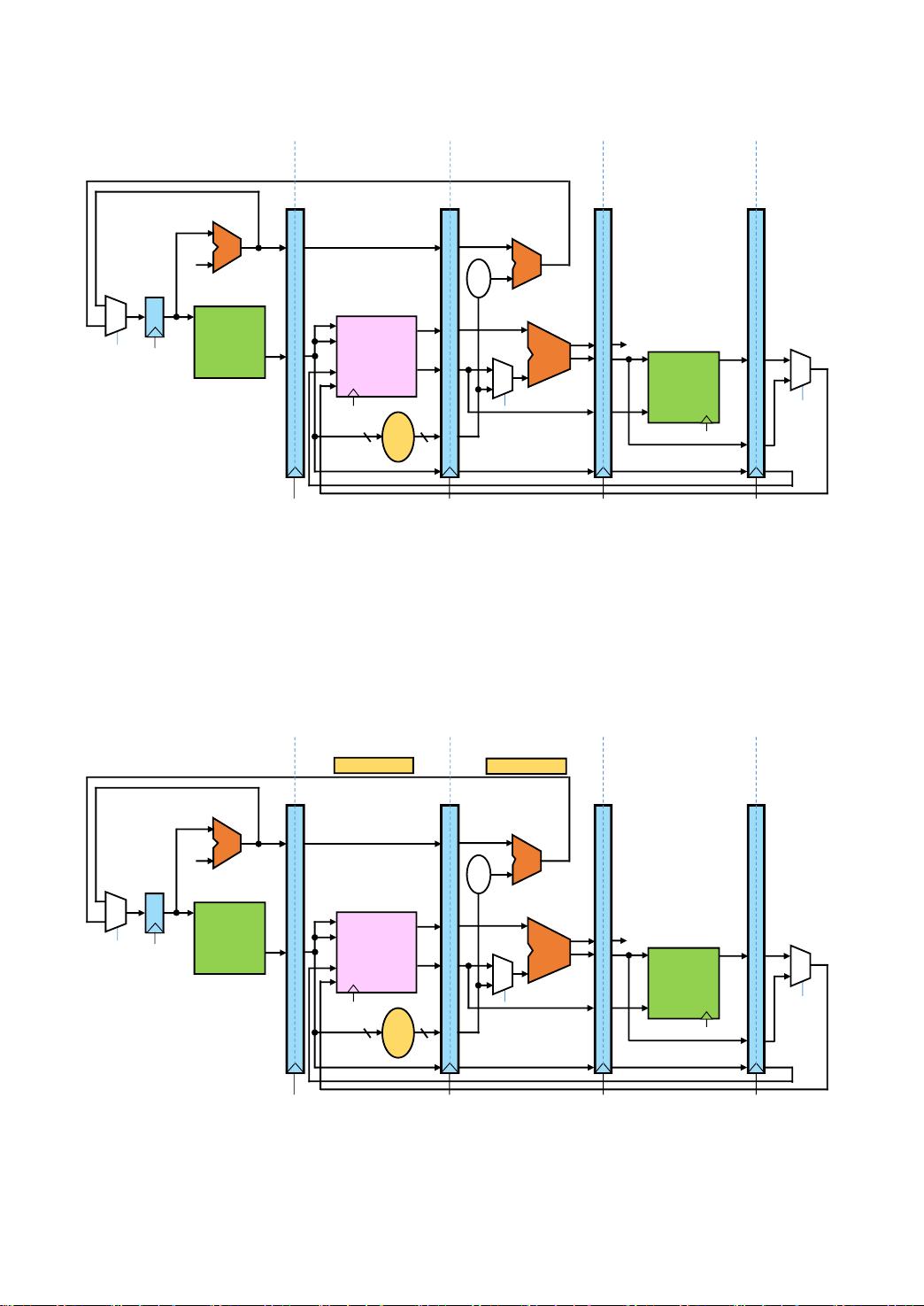

1. MIPS五段流水线结构:MIPS指令流水线通常分为五个阶段,包括取指令(IF)、指令译码(ID)、指令执行(EX)、访存(MEM)和写回(WB)。每个阶段之间通过流水接口部件(锁存器)进行数据传递,确保指令的有序执行。

2. 流水线的概念与应用:流水线技术起源于工业生产,如汽车装配线,将复杂任务分解为多个并行运行的阶段。在计算机中,无论是运算操作流水线还是指令流水线,都是为了提高系统效率,减少等待时间。

3. 单周期CPU与流水线比较:单周期CPU设计中,所有指令执行时间固定,受制于最慢指令,导致效率较低。现代处理器普遍采用多周期设计,特别是流水线CPU,通过时间重叠和空间复用,显著提高处理速度。

4. 流水线设计中的关键因素:为了保证流水线的正常工作,所有阶段需要同步,且各阶段的时间延迟应尽可能相等。锁存器在此过程中扮演重要角色,它们存储并传递前一阶段的结果给下一阶段。

5. 性能分析与时空图:学生需要学会通过时空图来评估流水CPU的性能,这有助于理解流水线的吞吐量、延迟和效率,以及识别潜在的问题和优化点。

通过这个实验,学生不仅可以掌握流水线的设计方法,还能提高对CPU内部工作原理的理解,为后续的处理器设计打下坚实的基础。

2022-08-08 上传

2021-03-19 上传

2021-04-07 上传

2010-11-25 上传

2011-10-29 上传

2022-06-21 上传

2023-10-02 上传

老许的花开

- 粉丝: 34

- 资源: 328

最新资源

- 图布局算法综述(很详细的)

- ORACLE傻瓜手册v2.0

- 基于FPGA 的DDS 调频信号的研究与实现.pdf

- ON_EXTENSION_AND_IMPLEMENTATION_MECHANISM_FOR.pdf

- grails入门指南

- LinkedIn - A Professional Network built with Java Technologies and Agile Practices

- sql性能调整-总结

- 硬盘接口技术详解文档

- 黑客常用DOS命令大全

- Sybase IQ For AIX安装

- GTK+ 2.0教程(PDF中文) unix/linux界面编程必备

- ISO27001标准的英文原版。。

- TD使用手册,比较经典的使用手册,测试必学

- 超市进销存管理系统的开发

- Compiere开发环境配置

- TortoiseSVN中文版手册

已收录资源合集

已收录资源合集