MIPI D-PHY技术详解:移动设备接口新标准

需积分: 7 95 浏览量

更新于2024-09-07

收藏 5.34MB PDF 举报

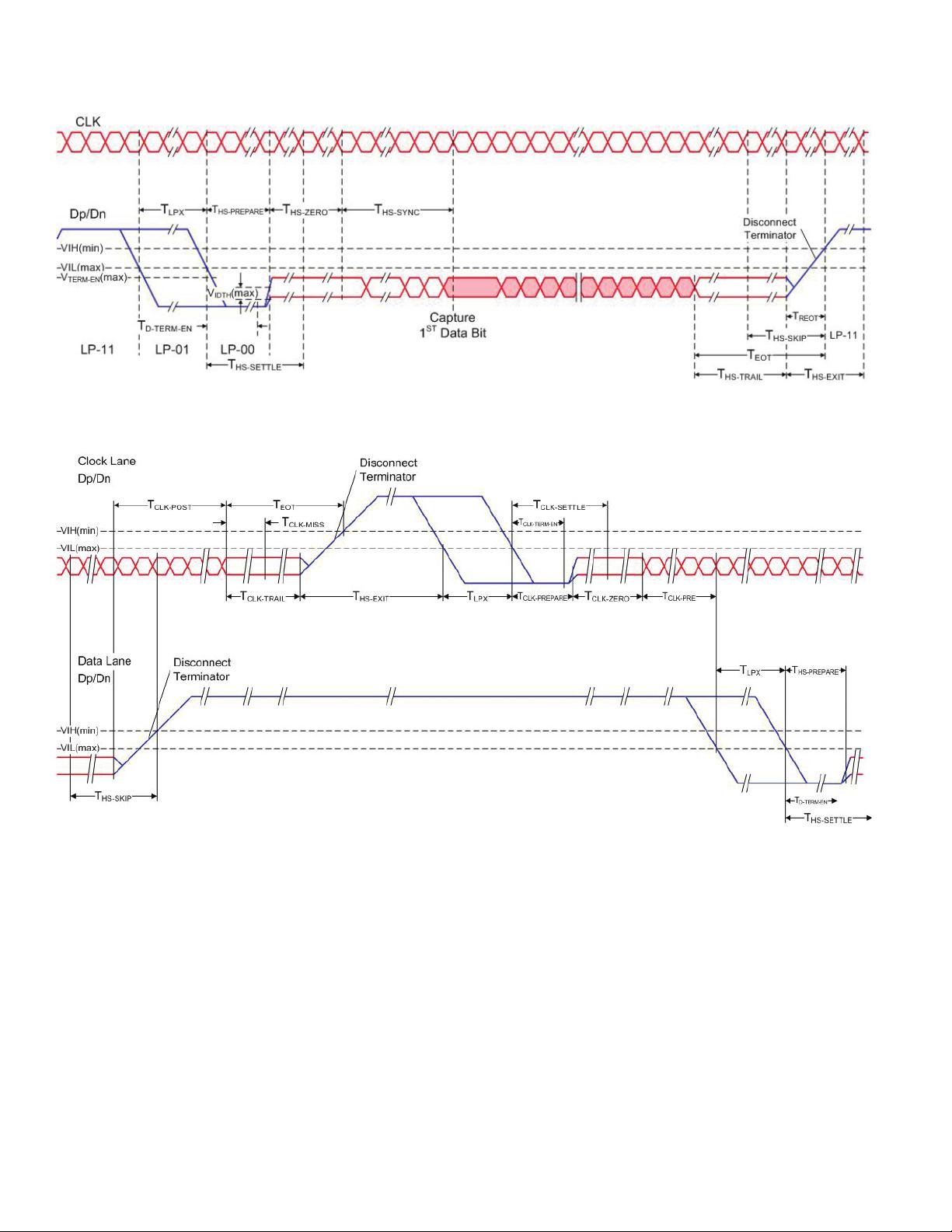

"这份应用笔记主要探讨了MIPI联盟中的D-PHY物理层技术,以及与之相关的CSI(Camera Serial Interface)和DSI(Display Serial Interface)协议层测试。MIPI Alliance致力于为移动设备和便携式设备制定标准化的硬件和软件接口,以提高互操作性、降低成本并解决开发难题。D-PHY是一种可重复使用、可扩展的物理层接口,适用于连接下一代智能手机、平板电脑等设备中的摄像头和显示屏到基带处理器。它具有在高速差分模式和低功耗单端模式之间实时切换的能力,以适应大数据传输或节能的需求。D-PHY支持单数据线或多数据线的简单或双向配置,并且时钟始终单向(主设备到从设备)且与数据相位差90度。"

MIPI D-PHY是MIPI Alliance制定的一种关键的物理层标准,设计用于移动设备中的高速数据传输。它的主要特点包括:

1. **可重用性和可扩展性**:D-PHY可以适应不同的组件和子系统,允许在不同类型的设备间进行接口集成。

2. **模式切换**:能够根据需求在高速差分模式和低功耗单端模式之间动态转换,平衡数据传输速度和电池寿命。

3. **配置灵活性**:支持单数据通道或多个数据通道的操作,可以是单工或双工配置,为设计者提供了更大的灵活性。

4. **时钟方向性**:时钟信号始终由主设备向从设备发送,与数据信号保持90度相位差,称为四相时钟,确保数据传输的精确同步。

MIPI D-PHY技术通常与两个协议层一起使用,即CSI和DSI:

- **MIPI CSI(Camera Serial Interface)**:专为图像传感器和处理单元之间的通信设计,支持高清视频和图像数据的高效传输。

- **MIPI DSI(Display Serial Interface)**:用于显示屏和处理器之间的通信,提供对高分辨率显示内容的支持。

这些标准的引入显著改善了移动设备的开发流程,提高了性能,增强了电池续航,并推动了更小、更低成本的产品设计。MIPI Alliance通过制定这些标准,不仅简化了组件间的兼容性问题,还促进了整个移动行业的创新和发展。

应用笔记进一步讨论了如何理解和执行MIPI D-PHY的物理层测试,以及如何进行CSI和DSI协议层的测试。这包括验证接口的正确性、性能测试、一致性检查以及故障诊断,以确保按照MIPI规范实现可靠的数据传输。测试过程对于确保设备间的兼容性和优化系统性能至关重要。通过使用专业的测试工具和方法,工程师可以有效地调试和优化他们的MIPI接口设计,从而加速产品的上市时间。

2018-10-09 上传

2023-10-17 上传

2023-10-17 上传

2022-07-14 上传

2022-07-15 上传

2022-07-14 上传

2021-05-22 上传

2023-10-11 上传

2023-08-12 上传

aidong20181008

- 粉丝: 0

- 资源: 10

最新资源

- 探索数据转换实验平台在设备装置中的应用

- 使用git-log-to-tikz.py将Git日志转换为TIKZ图形

- 小栗子源码2.9.3版本发布

- 使用Tinder-Hack-Client实现Tinder API交互

- Android Studio新模板:个性化Material Design导航抽屉

- React API分页模块:数据获取与页面管理

- C语言实现顺序表的动态分配方法

- 光催化分解水产氢固溶体催化剂制备技术揭秘

- VS2013环境下tinyxml库的32位与64位编译指南

- 网易云歌词情感分析系统实现与架构

- React应用展示GitHub用户详细信息及项目分析

- LayUI2.1.6帮助文档API功能详解

- 全栈开发实现的chatgpt应用可打包小程序/H5/App

- C++实现顺序表的动态内存分配技术

- Java制作水果格斗游戏:策略与随机性的结合

- 基于若依框架的后台管理系统开发实例解析